| IP개요 |

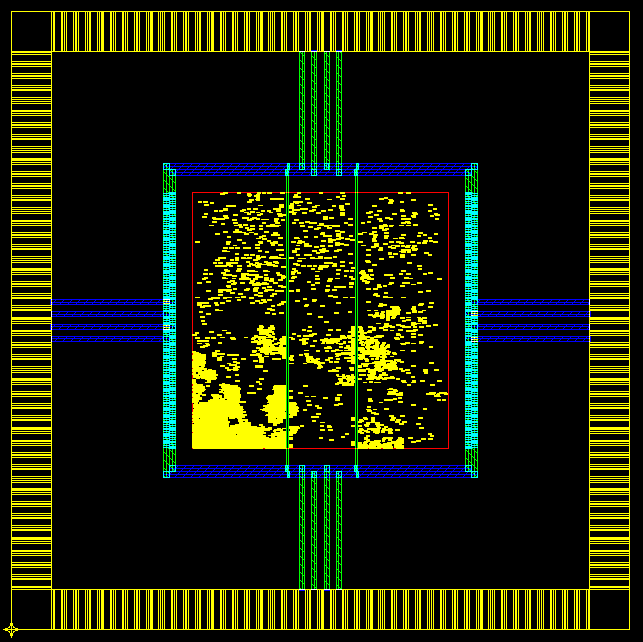

One of the most important blocks in the Orthogonal Frequency Division Multiplexing(OFDM) system is Fast Fourier Transform(FFT) and Inverse Fast Fourier Transform(IFFT). The memory and latency of the first stage are the largest in the Decimation in frequency(DIF) structure. Therefore, it is necessary to efficiently reduce the memory and latency of the first stage. This paper proposes a low-latency FFT and IFFT structure using null signal specified as standard in the 3^rdGeneration partnership project (3GPP). The proposed structure shows that delays can be reduced by 42 percent, areas reduced by 20 percent, and POWER by 13 percent. The proposed architecture is designed with a Magna Chip/SK Hynix 180nm CMOS process with a supply voltage of 1.8V and a maximum operating frequency of 25MHz. |