| IP명 | Computing-in-Memory with Array-to-Array Analog Communication for Neural Network | ||

|---|---|---|---|

| Category | Mixed | Application | AI |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 250MHz |

| 검증단계 | Silicon | 참여공정 | SS28-1901 |

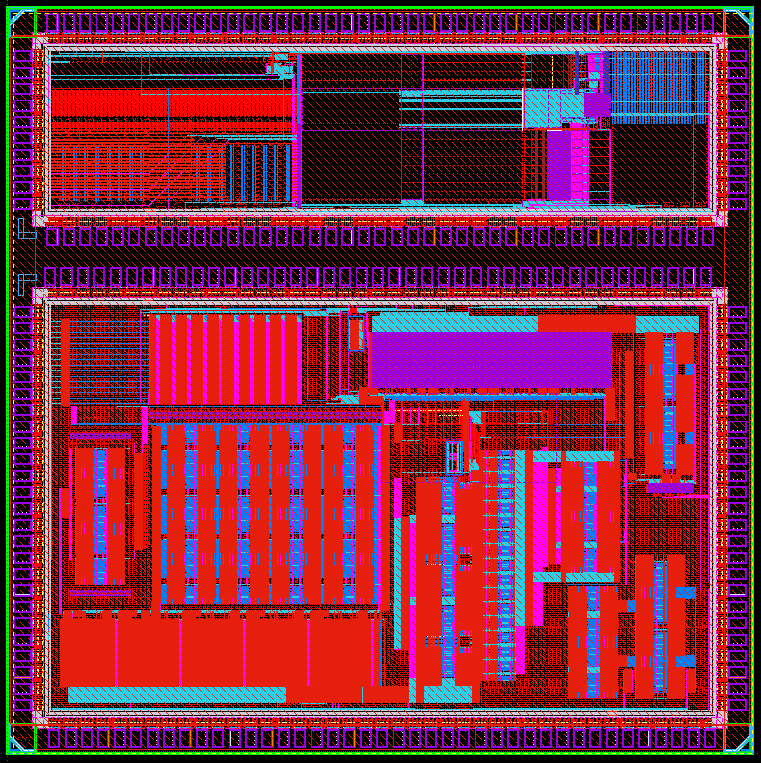

| IP개요 | Computing-in-memory with array-to-array analog communication is designed to implement neural network hardware. This system consists of DACs (Digital-toanalog converter), CIM (Computing-in-memory) arrays, and analog buffers. DACs convert the 8-bit digital codes into analog voltages by two step converting; digital-to-time converter and time-to-analog converter. Two SRAM arrays are used to calculate the weighted sum of neural network. The first array is composed of 32-WL x 200-BL 10T SRAM cells to implement 25 inputs and 32 outputs in 8-bit. The second array requires 5-WL x 256-BL to implement 32 inputs and 5 outputs in 8-bit. The analog buffer drives the output of first array to the input of the second array. This works is being designed and simulated in 28nm technology and is expected to show remarkable measurement results with silicon implementation |

||

- 레이아웃 사진 -

|

|||