| IP명 | A 0.6V 10 b Low-Noise Asynchronous SAR ADC | ||

|---|---|---|---|

| Category | Analog | Application | 무선통신 |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 0.6V |

| IP유형 | Hard IP | 동작속도 | 2MHz |

| 검증단계 | Simulation | 참여공정 | SS65-2002 |

| IP개요 | 기존의 SAR(Successive approximation register) ADC(analog-to-digital)는 8~10bit 수준의 resolution을 가지며 Flash ADC, Sigma-delta ADC와 비교하여 보통수준의 Sampling Frequency와 전력 소모를 가진다. 그러나 무선 센서나 휴대용 기기에서 사용되는 ADC는 더 낮은 전력소모를 요구한다. 본 연구에서는 Voltage domain Comparator와 Time domain Comparator를 사용하여 기존의 SAR ADC에 비해 전력소모를 감소시키고 잡음 특성을 개선하였다. 이를 위해 65nm 공정을 사용하고자 하며 공급전압은 0.6V이다.예상 최대 칩 사용 면적은 4mm X 4mm 이다. | ||

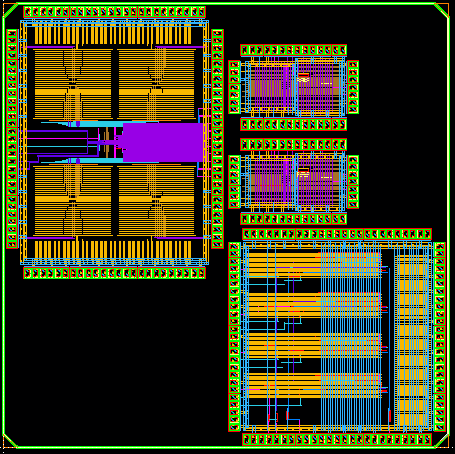

- 레이아웃 사진 -

|

|||