| IP명 | 고성능 광신호 검출용 아날로그 프론트엔드 설계 | ||

|---|---|---|---|

| Category | Mixed | Application | OTDR |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 500MHz |

| 검증단계 | Simulation | 참여공정 | SS65-1902 |

| IP개요 | 본 연구는 OTDR 의 아날로그 부분을 개발하여 시제품 형태의 보드 개발 및 제작을 목적으로 한다. OTDR 을 구성하기 위한 광펄스 OPTIC 보드의 아날로그 부분을 하나의 칩으로 직접화 하여 개발한다. ADP 의 신호를 증폭시키기 때문에 잡음에 가장 민감하게 반응하는 TIA 의 증폭도를 높이고 저 잡음 설계 기법을 적용하여 높은 SNR 을 구현하는 설계를 한다. SNR 을 증가시켜 높은 dynamic range 를 구현 함을 목적으로 한다. 본 연구는 Samsung 65nm 공정을 이용하여 1.2V 공급전압 하에서 12bit, 50MS/s 수준의 고정밀 고속 ADC 를 설계 및 개발하여 높은 data rate 를 구현하고, 10mW 수준의 저전력 설계 기법을 적용하여 전력 소모를 최소화 한다. | ||

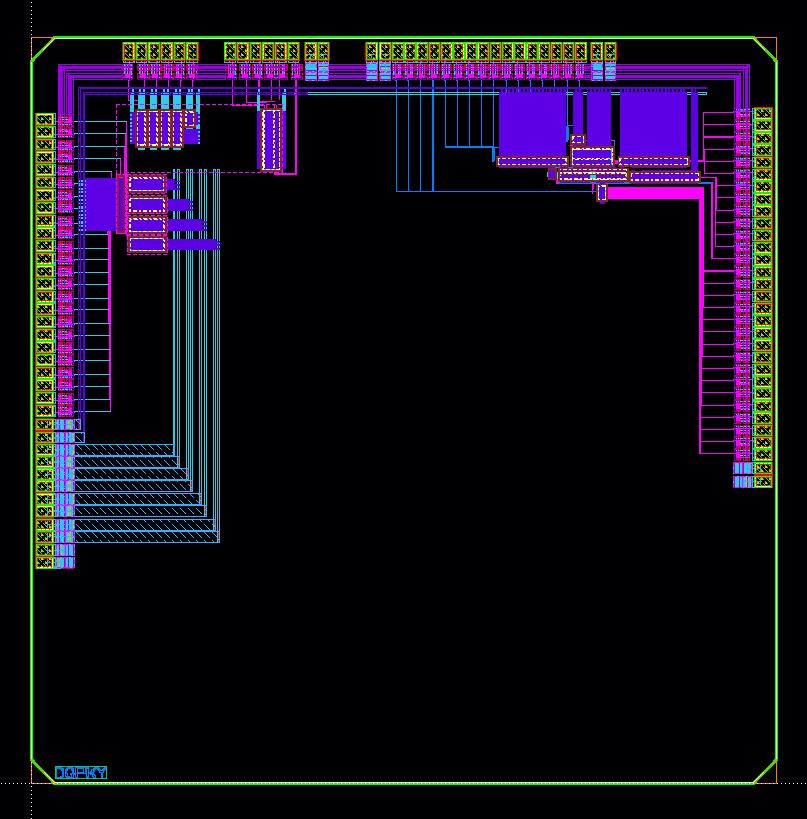

- 레이아웃 사진 -

|

|||