| IP명 | Supply Noise Insensitive Clock Distribution Network for DRAM | ||

|---|---|---|---|

| Category | Digital | Application | DRAM |

| 실설계면적 | 2.66㎛ X 1.11㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 3.2GHz |

| 검증단계 | Silicon | 참여공정 | SS65-1902 |

| IP개요 | 최근 들어, 5G 통신이나 AI, 자동차의 주행보조 시스템 등을 위한 고성능 저전력 기술 요구들이 꾸준히 증가하고 있다. 이러한 요구를 충족시키기 위해 CPU, APU, GPU 뿐만 아니라 DRAM의 경우도 low-power high-performance 특성을 갖도록 발전하여 왔다. 특히, 차세대 mobile DRAM인 LPDDR5의 경우 더 낮은 전력 소모를 하면서 LPDDR4 data 처리 속도인 4.3Gbps의 1.5배에 달하는 6.4Gbps 지원을 목표로 하고 있다. 이러한 저전력 고성능 동작을 위해서는 clock의 jitter 특성이 매우 중요하며, clock jitter 특성에 가장 큰 영향을 미치는 요소는 supply noise로 알려져 있다. 본 회로에서는 supply noise에 insensitive한 DRAM용 clock distribution 구조를 제안하고자 한다. 동작 주파수는 최대 3.2GHz이며, 동작 전압은 1V 이하를 사용할 예정이다. 제안된 회로는 analog 및 digital 회로를 모두 사용한 mixed회로로 구현하였다. |

||

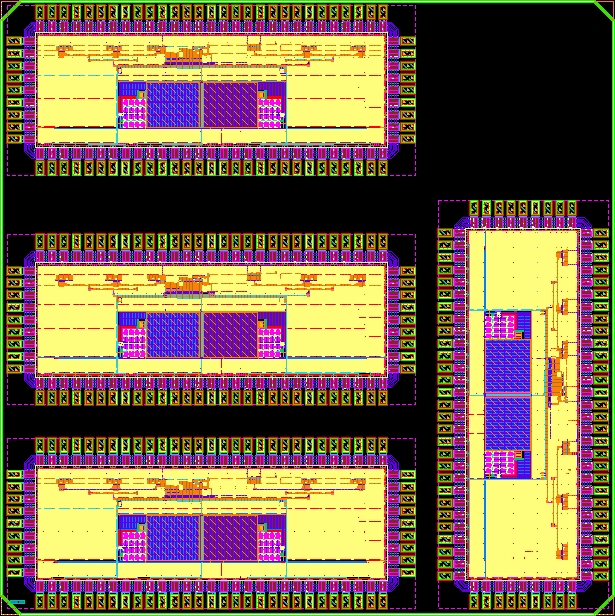

- 레이아웃 사진 -

|

|||