| IP명 | A Referenceless Clock and Data Recovery Circuit With Bidirectional Frequency Detector | ||

|---|---|---|---|

| Category | RF | Application | High Speed Interface |

| 실설계면적 | 1.8㎛ X 0.7㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 2Hz |

| 검증단계 | Silicon | 참여공정 | MS180-1902 |

| IP개요 | 본 논문은 180nm CMOS 공정을 기반으로 한 양방향 주파수 검출기를 이용한기준 클럭 없는 하프-레이트 클럭 데이터 복원(CDR)을 다룬다. 양방향 주파수 검출기(FD)는 고조파 잠금 문제를 제거하고 주파수 획득 시간을 감소시키는 것을 목적으로 한다. 전압-조절 발진기(VCO)의 정확한 주파수 대역을 선택하기 위해 넓은 범위의 VCO를 위한 주파수 대역 선택기(FBS)를 사용하였다. 실험 결과는 주파수 획득 시간이 4.82us 임을 보여준다. | ||

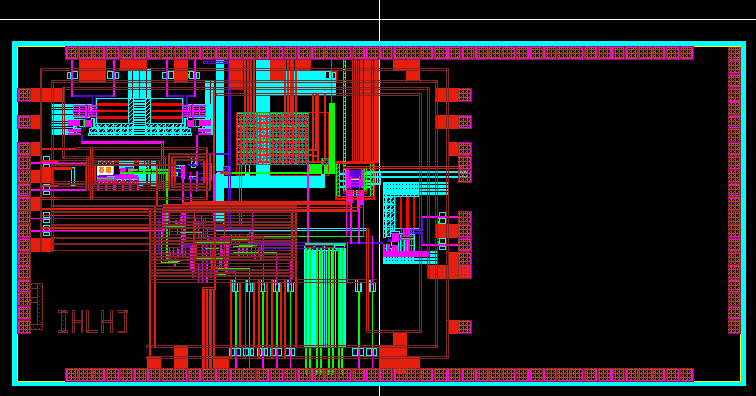

- 레이아웃 사진 -

|

|||