| IP명 | Nano-scale CMOS technology에서의 발열 완화 레이아웃 기법 및 열 인식 트랜지스터 모델 개발 | ||

|---|---|---|---|

| Category | Analog | Application | consumer electronics |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 3.3/2.5/1.2V |

| IP유형 | Hard IP | 동작속도 | 150 MHz |

| 검증단계 | FPGA | 참여공정 | SS65-1901 |

| IP개요 | 본 연구는 Nano-scale CMOS technology의 발열완화 레이아웃 기법과 열 인식 트랜지스터 모델 개발에대한 연구로 발열로 인한 단일 트랜지스터 및 회로의성능저하 감소 및 예측을 목적으로 한다. 트랜지스터 내열이 가장 취약한 드레인 영역에 Metal/via를 이용한 열통로를 생성하여 응집된 열을 완화시켜 온도를 낮추고,회로 내 각 트랜지스터 마다 다른 온도를 인식하는 모델을 통해 측정 이전에 그 효과를 예측한다. Samsung 65nm공정을 이용하여 NAND gate, Flip-Flop 등을 포함하는 standard library cell을 개발하며 GHz의 고속동작 Ring oscillator를 제작하여 1.2V 공급전압 하에 발생하는 발열 현상에 대해 확인한다. 회로 내 발생하는 열을 예측하고 제안하는 레이아웃 기법을 통해 전력소모를 최소화 하여 Nanoscale의 CMOS공정에서 열적, 전기적으로 최적화된 회로를 설계한다. | ||

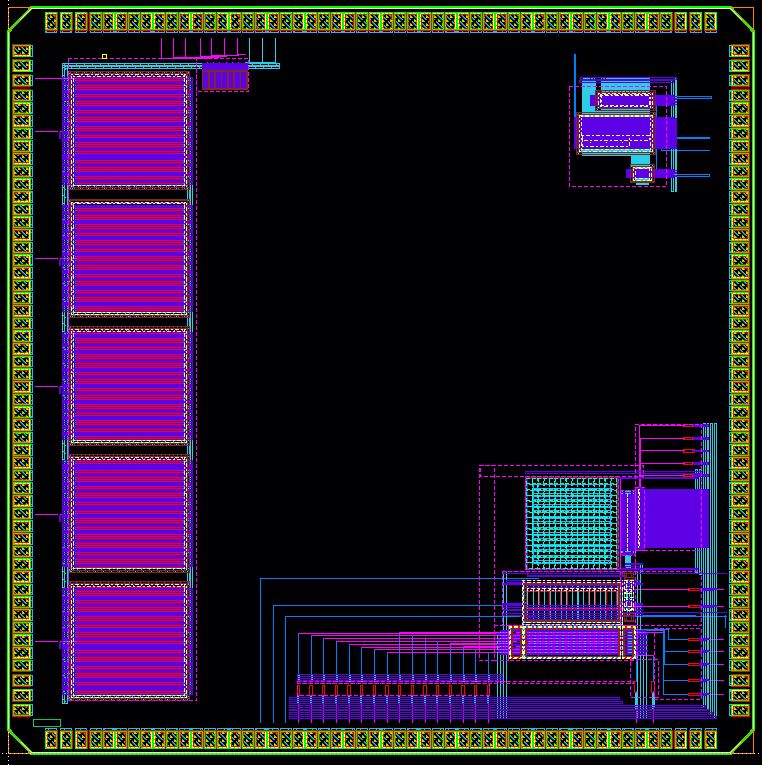

- 레이아웃 사진 -

|

|||