| IP명 | 2GS/s 9-Bit Direct Digital Frequency Synthesizer with Nonlinear Digital-to-Analog Converter | ||

|---|---|---|---|

| Category | Analog | Application | Frequency Synthesizer |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.2/1.8V |

| IP유형 | Hard IP | 동작속도 | 2GHz |

| 검증단계 | Silicon | 참여공정 | SS65-1901 |

| IP개요 | Nonlinear DAC를 기반으로 DDFS (Direct Digital Frequency Synthesizer)를 Samsung-65 nm 공정을 사용하여, 1.2 V 전압과 1 GHz의 최대 동작 주파수를 가지는 회로를 구현하고자 한다. DDFS의 성능 및 전력 효율을 향상시키기 위하여 세 가지 방법을 제안한다. 첫 번째, 대다수의 DDFS는 보통 고속으로 동작하기 때문에 CML (Current Mode Logic)을 사용하여 static power가 발생을 하고 power가 많이 소모된다. 이번에 구현하고자 하는 회로는 CML이 아닌 CMOS로 구현을 하여 static power를 줄이고자 한다. 두 번째, digital decoder에서 하드웨어의 복잡성 및 전력 소모를 줄이기 위하여 (Coarse phase based Consecutive Fine Amplitude Grouping scheme)을 사용한다. 세 번째, MCT(Mixed-wave Conversion Topology)를 사용하여 dynamic performance를 높인다. |

||

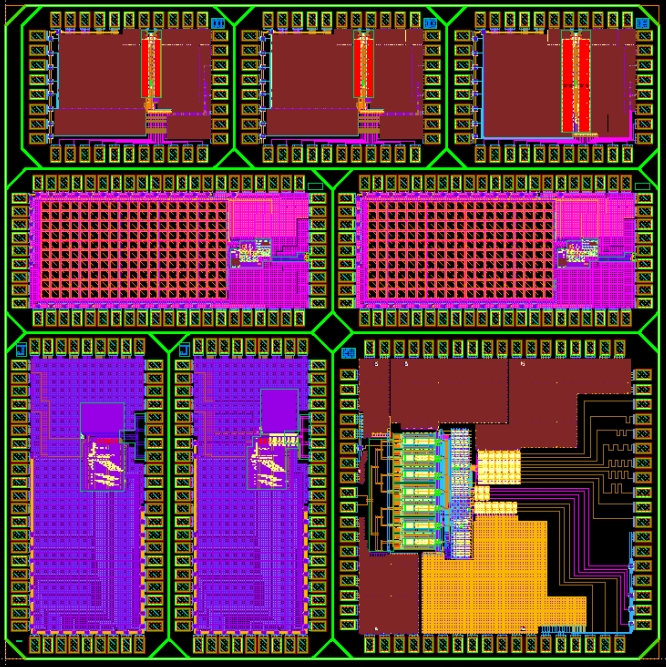

- 레이아웃 사진 -

|

|||