반도체설계교육센터 사업은 지식경제부, 반도체산업협회, 반도체회사(삼성전자, 하이닉스반도체, 매그나칩반도체, 동부하이텍, 앰코테크놀로지코리아, KEC, 세미텍, TowerJazz)의 지원으로 수행되고 있습니다.

## 시스템 수준 설계 기술동향

반도체 공정기술의 발달로 급증하는 집적능력을 충분히 활용하기 위하여 시스템 반도체의 설계복잡도가 증가하게 되었다. 즉, 하나의 칩에 많은 기능블록을 집적하 거나 보다 복잡하지만, 고성능의 기능블록을 추가하게 된다. 하지만, 이러한 설계복잡도의 증가 속도보다 설계자의 설계생산성은 그에 미치지 못하는 문제가 심화하 였다. 이러한 문제를 해결할 수 있는 방법의 하나로 시스템 수준 설계기술이 주목받고 있다. 본 고에서는 시스템 수준 설계기술 동향에 대해 알아보고자 한다. (관련 기사 P06~09참조)

## CCTV 영상 보안 시스템의 보안 위협 및 대응 방안

CCTV는 화상정보를 특정의 목적으로 특정 사용자에게 전달해 주는 시스템으로, 초기 금융기관 등의 범죄 방지용으로 사용되었으나, 최근에는 가정, 학교, 회사, 공공기관 등 사회 전반으로 그 사용범위가 넓어지고 있다. 특히 각종 범죄가 증가함에 따라 CCTV는 방범용으로 사용하는 등 적용범위가 기하급수적으로 증가하게 되었으나, 방범 등의 목적으로 설치, 관리하는 CCTV의 영상정보는 정보의 유출 위험에 무방비 상태로 노출되어 있어 언론을 통해 그 문제점이 심각하게 부각되고 있다. 본고에서는 보안이 취약한 현장단과 관제센터 간의 네트워크상에서 영상 시스템의 보안 위협에 대한 문제점을 알아보고, 기존의 영상 시스템에서의 데이터 변조나 해킹 등의 보안 문제를 해결하기 위한 대응 방안에 대해 알아보고자 한다. (관련기사 P10~12참조)

## 3-D NAND Flash Memory (2)

소자의 크기를 줄이지 않으면서 집적도를 향상시키기 위한 방법으로 최근 각광받는 방법은 3-D method이다. 이는 기존의 단순한 2차원의 1층 제조 방법에서 어나 수직 방향으로 동일한 소자를 다수 적층함으로서 소자 크기를 유지하면서 집적도를 크게 향상시킬 수 있다. 이것은 마치 1층 주택을 아파트로 대체하면서 지 면적은 그대로 유지하면서 가구 수를 크게 늘리는 방법과 동일하다고 할 수 있다. 따라서 현재 세계 유수의 반도체 제조 회사들은 이 3-D memory 개발에 점을 두고 있으며 그중에서도 1개의 트랜지스터로 구성할 수 있는 Flash memory 개발에 주력하고 있다. 따라서 본 고에서는 지난 호에 이어서 TCAT, V NAND 개발 동향에 대해서 살펴보도록 하겠다. (관련기사 P14~19 참조) 166호뉴스레터\_인쇄:레이아웃 1 11.04.01 오후 6:35 페이지 3

|                      | MPW (Multi-Project Wafer) |                                                     |          |          |                                                                                   |                        |                        |                      |                                                                                                                                                                 |                             |  |  |  |  |  |  |  |

|----------------------|---------------------------|-----------------------------------------------------|----------|----------|-----------------------------------------------------------------------------------|------------------------|------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|--|

| 신청                   | 현황                        |                                                     |          |          |                                                                                   |                        |                        |                      |                                                                                                                                                                 |                             |  |  |  |  |  |  |  |

| 구분                   | 공정                        | 제작가능면적<br>(mm2 x 칩수)                                | 신청<br>팀수 | 채택<br>팀수 | 설계면적<br>(mm2 x 칩수)                                                                | DB<br>마감               | Die<br>-out            | 비고                   |                                                                                                                                                                 | Die 비고<br>out               |  |  |  |  |  |  |  |

|                      | TJ RF<br>0.18             | 5x5mm <sup>2</sup> x 2                              | 5        | 5        | 5x5mm <sup>2</sup> x 1<br>2.5x2.5mm <sup>2</sup> x 4                              |                        |                        | DB<br>전달완료           |                                                                                                                                                                 | )12<br>.10                  |  |  |  |  |  |  |  |

| 제99회<br>(11-02)      | 동부<br>BCD<br>0.35         | 5x5mm² x 3                                          | 6        | 6        |                                                                                   | 2011.<br>2,22          | 2011.<br>6.1 ?         | DB<br>전달완료           |                                                                                                                                                                 | )12.<br>.10                 |  |  |  |  |  |  |  |

|                      | 동부<br>0.13                | 5x5mm <sup>2</sup> x 23                             | 30       | 30       | 5x5mm <sup>2</sup> x 18<br>5x2.5mm <sup>2</sup> x 8<br>2.5x2.5mm <sup>2</sup> x 4 | 2011.<br>3.21          | 2011.<br>7.6           | DB<br>검토중            | * 105~107회는 우선모집 결과임전체모집 가능수의 50% 선정                                                                                                                            |                             |  |  |  |  |  |  |  |

| 100회                 | 동부<br>BCD<br>0.35         | 5x5mm² x 3                                          | 7        | 6        | 5x2.5mm <sup>2</sup> x 6                                                          | 2011.<br>4.7           | 2011.<br>7.12          |                      |                                                                                                                                                                 |                             |  |  |  |  |  |  |  |

| (11-03)              | 삼성<br>0.13                | 4x4mm² x 48                                         | 41       | 41       | 4x4mm <sup>2</sup> x 40<br>4x8mm <sup>2</sup> x 1                                 | 2011.<br>4.25          | 2011.<br>8.25          |                      | 집제작 현황                                                                                                                                                          |                             |  |  |  |  |  |  |  |

| 101회                 | TJ RF<br>0.18             | 5x5mm <sup>2</sup> x 2                              | 8        | 8        | 2,5x2,5mm² x 8                                                                    | 2011.<br>5.2           | 2011.<br>7.19          |                      | 구분 공정 제작가능면적 제작 제작면적 Die-out 현재<br>(mm2 x 칩수) 칩수 (mm2 x 칩수) 예정일 상태                                                                                              | 비고                          |  |  |  |  |  |  |  |

| (11-04) <sub>N</sub> | 0.18                      | 4.5x4mm <sup>2</sup> x 20                           | 21       | 20       | 4.5x4mm² x 20                                                                     | 2011.<br>5.13          | 2011.<br>9.5           |                      | 세명이외 점점 (10-07) 90n 4x4mm <sup>2</sup> x 20 15 4x4mm <sup>2</sup> x 15 220 제작주 F                                                                                | )ie:3.25<br>PKG:4.5<br>테작예정 |  |  |  |  |  |  |  |

| 102회<br>(11-05)      | 0.55                      | 5x5mm² x 3                                          | 10       | 6        | 5x2.5mm <sup>2</sup> x 6                                                          | 2011.<br>5.25          | 2011.<br>8.31          |                      | M/H 4 5 v4mm² v 40 32 4 5 v4mm² v 32 2011. 제작 다                                                                                                                 | Die:1,24<br>PKG:3.11        |  |  |  |  |  |  |  |

| 103회                 | TJ<br>CIS<br>0.18         | 5x5mm <sup>2</sup> x 1                              | 5        | 4        | 2,5x2,5mm <sup>2</sup> x 4                                                        | 2011.<br>6.21          | 2011.<br>9.21          |                      | (10-08)                                                                                                                                                         | Die:3,2                     |  |  |  |  |  |  |  |

| (11-06)              | 동부<br>BCD<br>0.35         | 5x5mm² x 3                                          | 9        | 5        | 5x5mm <sup>2</sup> x 1<br>5x2,5mm <sup>2</sup> x 4                                |                        | 2011.<br>10.12         |                      | 0.13 5x5mm² x 6 18 2.5x2.5mm² x 12 2.25 제작중                                                                                                                     | PKG:3,30<br>체작예정            |  |  |  |  |  |  |  |

|                      | TJ<br>BCD<br>0.18         | 5x5mm <sup>2</sup> x 2                              | 1        | 1        | 5x5mm <sup>2</sup> x 1                                                            | 2011.<br>8.29          | 2011.<br>11.15         |                      | TJ<br>SIGe 5x5mm² x 1 4 2,5x2,5mm² x 4 524 직중                                                                                                                   |                             |  |  |  |  |  |  |  |

| 104회<br>(11-07)      | M/H<br>0.35<br>M/H        | 5x4mm <sup>2</sup> x 20                             | 7        | 7        | 5X4mm <sup>2</sup> X /                                                            | 2011.<br>8.29<br>2011. | 2011.<br>12.20<br>2011 | 설명회<br>개최<br>-MU-221 | 제98회 0.18 WH (11-01) MH 5x4mm² x 20 19 5x4mm² x 19 2011. 침제                                                                                                     |                             |  |  |  |  |  |  |  |

|                      | 0.18<br>삼성                | 20개 서버                                              | 15<br>23 | 15<br>23 | 4,5x4mm <sup>-</sup> x 15                                                         | 8.29                   | 12.20 -<br>2012.       | -삼성:4.1              | 0,35 M/H 0,18 4.5x4mm² x 20 20 4.5x4mm² x 20 20 4.5x4mm² x 20 20 4.5x4m² x 20 6.7 작중                                                                            |                             |  |  |  |  |  |  |  |

|                      | 65n<br>TJ<br>CIS          | (4x4mm <sup>2</sup> x 48)<br>5x5mm <sup>2</sup> x 1 | 1        | 1        | 2.5v2.5mm² v 1                                                                    | 8.19<br>2011.          | 1,15<br>2012.          |                      | 0.10 0.7 극중                                                                                                                                                     |                             |  |  |  |  |  |  |  |

| 105=1                | 0.18<br>동부                |                                                     |          |          | 5x5mm <sup>2</sup> x 1                                                            | 10.10                  | 1,11                   |                      | * M/H = 매그나칩/하이닉스, TJ = TowerJazz<br>* 우선/정규모집에서 마감될 경우 후기모집은 진행되지 않음.                                                                                          |                             |  |  |  |  |  |  |  |

| 105회<br>(11-08)      | 0.35                      | 5x5mm <sup>2</sup> x 3                              | 2        | 2        | 2,5x2,5mm <sup>2</sup> x 1                                                        | 10.13                  | 1.18 ?                 | 정규모집<br>:~4.15       | <ul> <li>Die-out 일정은 Diechip 제작완료 기준임, Package는 Die-out후 3주 이상 소요됨.</li> <li>2011년 MPW 참여 일정 및 방법은 홈페이지(www.idec.or.kr) 참조</li> <li>위의 내용은 3/29 기준임.</li> </ul> |                             |  |  |  |  |  |  |  |

|                      | 동부<br>0.11<br>KEC 4       | 5x5mm <sup>2</sup> x 13<br>5x5mm <sup>2</sup> x 20  | 6        | 6        | 5x2.5mm <sup>2</sup> x 5<br>2.5x2.5mm <sup>2</sup> x 2                            |                        | 2012.<br>1.10<br>2012  |                      |                                                                                                                                                                 |                             |  |  |  |  |  |  |  |

| ŀ                    | KEC 0.                    | 5 5x5mm <sup>2</sup> x 20                           | -        | -        |                                                                                   | 10.14                  |                        |                      | * 문의 : 이의숙(042-350-4428, yslee@idec.ka                                                                                                                          | nist.ac.kr)                 |  |  |  |  |  |  |  |

## NDA가 체결된 Design Data 유출 금지 안내

IDEC의 MPW 참가를 통해 전달받은 Design Data 일체는 NDA를 통해서 법적인 구속력을 가지며, 관리 소홀로 인한 외부로의 공개 또는 유출 시 개인뿐만 아니라 개인이 속해 있는 WG에 자격 박탈과 같은 강력한 규제가 가해질 수 있습니다. 협약에 의해, 형사상 책임을 물을 수 있음을 알려 드립니다. MPW 참여자 분들은 Design Data 및 관련 자료의 관리를 철저히 하시어 불이익을 당하는 일이 없도록 거듭 당부 드립니다.

NDA 체결 후 수령한 Design Kit 일체는 IDEC에 칩 수령 후 2개월 이내에 반드시 삭제하고, NDA 폐기확인서를 제출하여 제3자에 의한 공개 및 유출이 일어나지 않도록 주의 바랍니다.

IDEC Newsletter • 02 | 03

수강을 원하는 분은 IDEC홈페이지(www.idec.or.kr)를 방문하여 신청하시기 바랍니다.

## 본 센터 강좌 일정 |

| 강의 일자   | 강의 제목                  | 분 류  |

|---------|------------------------|------|

| 4월 4-5일 | SOC-Encounter 교육(Flat) | Tool |

■ 강좌일: 4월 4-5일

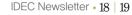

■ 강좌 제목 : SOC-Encounter 교육(Flat) ■ 강사 : 황재헌 부장 (Cadence Korea)

## [ 강좌개요 ]

Customer IC 를 제작하는 Tool은 다양한 기능의 제공이 수반되는데 그중 Layout Tool 교육은 Real Pattern을 실현하는 과정에대한 교 육으로서 그 방법및 Performance에대한 설명. 그리고 Deep SubMicron으로 진행 될수록 발생하는 차이점에 대한 Cadence Tool의 Capability 이해를 내용으로 하여 진행 할 예정임.

[ 수강대상 ]

[ 강의수준 ] · 초중급

석박사과정 및 기업체 연구원

[ 강의형태 ]

· 이론 + 실습

[ 사전지식, 선수과목 ]

· SOC-Encounter의 주요 기능은 무엇인가...?

· RTL2GDS Flow에 있어 어느 Stage에 해당한가...?

· Design Kit란 무엇인가...?

\* 문의 : 이승자 (042-350-8536, sjlee@idec.kaist.ac.kr)

## 채용 안내

## • KAIST 반도체설계교육센터(IDEC)를 이끌어 갈 젊음과 열정을 가진 인재를 찾습니다.

#### 1. 모집 분야

•모집인원 : 연구직 (신입·경력), 0명

• 자격조건 : 대졸 이상. 반도체설계 관련 전공자. 영어 능통자 우대.

• 주요업무 : - 국·내외 Fab을 통한 칩 설계. 제작 지원

- Digital, Analog 칩 TEST기술 지원

- EDA tool 교육 및 기술 지원

## 2. 제출 서류

• 당사 입사지원서(홈페이지에서 다운로드)

• 최종학교 성적증명서 1부

• 졸업(예정) 증명서 1부

## 3. 접수 기간 및 접수처

• 접수기간 : 2011년 4월 29일(금)

• 접 수 처 : (305-701) 대전광역시 유성구 구성동 373-1 한국과학기술원 반도체설계교육센터 104호

• 접수방법 : 우편접수, 이메일 접수

• 문 의 처: 042-350-4045, shchoi@idec.kaist.ac.kr

• 홈페이지: www.idec.or.kr

#### 4. 기타

• 기타 자세한 사항은 홈페이지(www.idec.or.kr) 참조

• 접수된 서류는 인비 처리하며 반환하지 않음.

## IDEC Platform Center (IPC) 사업계획서 추가 및 변경

• 시스템 반도체 육성을 위한 정부정책 및 산업체 Needs에 의거, IT 및 융합 기술의 핵심영역에서의 학·연·산 협업을 통한 융복합형 인력양성을 목적으로 IDEC에서는 2011년도 IDEC Platform Center (IPC) 공모하였다. 사업계획서 작성시 아래 내용을 추가.

#### 선정 된 IPC 혜택

● 에산지원 : 2개의 IPC선정 예정[각 4억원 내외(총 예산 8.5억원)] ● 가점혜택 : 2011년도 산업융합원천기술개발사업(정보통신) 신규지원 사업 중 "융복합 혁신 반도체 기술개발 사업" 선정 평가시 가점 혜택 부여 (현재, 한국산업기술평가관리원 주요사업공고에 공고)

◆ 본 사업을 2011년까지 지원하지만 성공적으로 진행 될 경우, 2012년 이후 관련 사업 선정 평가시 가점을 받을 수 있음

#### 1. 사업계획서 추가 내용

| 구분        | 항목                        | 추가 될 내용                                                                                                                                                                                                                                                                                                      |

|-----------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 제2장<br>2절 | 기술 플랫폼<br>구축 방안           | ◆실습, 연구 시작(試作), 창업/사업화 플랫폼의 구축,<br>적어도 구축 방안에 대한 연구가 사업내용에 포함<br>되어야 함                                                                                                                                                                                                                                       |

| 제2장<br>3절 | 교육(커리큘럼)<br>개발 및<br>운영 전략 | ●해당 플랫폼을 위한 최소한 시규 5개의 융합교과목에 대한 curriculum, 각 교과목의 Syllabus의 개발. (단, 여기서 융합과목이란 : 전자, 전산 외의 내용을 포함할 수 있으며, 기존의 전통적인 전자공학 분야의 어느 단일 교과목의 범위를 넘을 수 있는 과목을 일걸음)  ◆상기 Syllabus에 의거한 각 교과목의 pt 수준 강의 노트, 혹은 교재의 개발 정규과정에 편입하는 방안의 제안, 혹은 편입한 실적의 제시  *개발된 교과목에 대한 강의 delivery 방식/학생연구는문 지도와 기술토론 주행 방식에 대한 제안 작성 |

| 제2장<br>4절 | 연구개발<br>전략                | <ul> <li>해당 플랫폼 분야의 기술적 경쟁력 확보를 위하여 가장<br/>중요한 핵심주제를 선정(선정 배경과 함께 제시)</li> <li>선정 주제에 대한 연구 수행 계획(연구원, 수행방법,<br/>예산, 통시, 추진하는 교육 플랫폼의 활용방안, 혹은<br/>플랫폼 구축에의 공헌 방안)을 제시</li> </ul>                                                                                                                            |

| 제2장<br>5절 | 관련 산업의<br>네트워킹            | ◆플랫폼의 구축 및 운영에 있어서 관련 분야 기업, 연구<br>소가 어떻게 협력할 것인지 구체적인 방안, 2012년 이후<br>이 시업의 결과를 본 시업에 어떻게 연결 할 것인기에 대한<br>방안 제시                                                                                                                                                                                             |

|           |                           |                                                                                                                                                                                                                                                                                                              |

## 2 신청절차 및 방법

| Z. LOZA       | × 0 H                      |                             |                               |                              |

|---------------|----------------------------|-----------------------------|-------------------------------|------------------------------|

| 사업설명회<br>참석   | 계획서<br>제출                  | 서류평가                        | 발표평가                          | 최종평가<br>후 선정                 |

| IPC 사업<br>설명회 | 계획서 작성<br>후 우편 및<br>온라인 제출 | 계획서<br>제출한<br>대상자에<br>한해 평가 | 서류평가<br>에서 선정<br>된자에<br>한해 평가 | 평가위원화<br>에서 최종<br>심의 후<br>선정 |

| IDEC          | 총괄책임자                      | 총괄책임자                       | 총괄책임자<br>및<br>기술책임자           | IDEC                         |

### 3. 계획서 제출

◆ 제출방법: 우편 및 담당자 E-mail를 통해 제출 ◆ 제출기간: 2011, 3, 1(화) ~ 2011, 4, 15(금) 18:00 까지 ◆ 주소: 대전광역시 유성구 과학로 335번지 한국과학기술원

반도체설계교육센터(N26) 104호

◆ E-mail : ejkim@idec.kaist.ac.kr

\* 신청서 양식 및 기타 자세한 사항은 반도체설계교육센터 홈페이지(http://www.idec.or.kr) 참조

\* 문의: 김은주(042-350-8533), 최신희(042-350-4045)

166호뉴스레터\_인쇄:레이아웃 1 11.04.01 오후 6:35 페이지 5

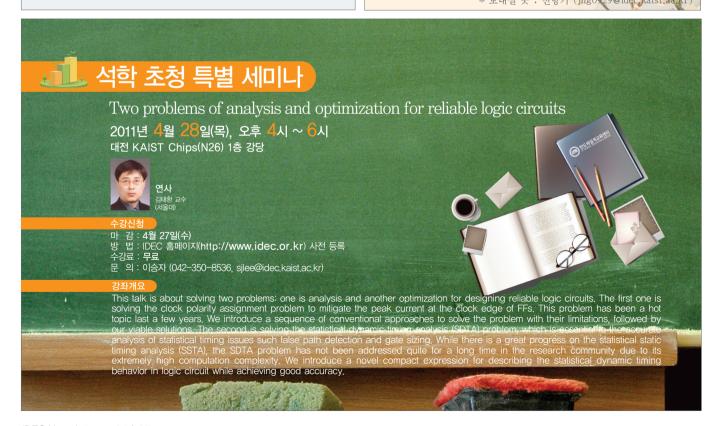

## 제2기 IDEC 장학금 수여식

• 반도체설계교육센터(IDEC, 소장 경종민)는 지난 3월 29일 (회), 제3차 IDEC 운영위원회의에 앞서 전자 및 반도체 전공자 중 우수학생을 선발하여 장학금을 지급하는 「반도체설계교육 센터 장학생, 장학금 수여식을 가졌다.

(좌로부터, 조성환 교수(KAIST), 배현민 교수(KAIST), 경종민 소장(IDEC), 박찬오 군(성균관대), 나은수 군(광운대, 이기준 교수(총남대), 감이섭 교수(KAIST), 이희덕 교수(총남대, 박인철 교수(KAIST))

「제2기 반도체설계교육센터 장학생」은 나은수 군(광운대 전자통신공학과 석사과정, 책임교수: 정용진 교수)과 박찬오 군(성균관대 전자전기컴퓨터 공학과 석사과정, 책임교수: 조준동 교수)이 선발되어 130만원의 장학금을 각각 받았다.

「반도체설계교육센터 장학생」은 연 2회(학기별) 각 2명을 선발하며 선발 기준은 IDEC WG(Working group) 소속 대학교 재학생 또는 입학예정자 로서 ▲가정형편이 곤란하여 학비조달이 어려우며, 학업성적 또는 연구실 적이 우수한 자 또는 ▲기타 장학금 지급이 필요하다고 인정된 자로서 WG 책임교수의 추천이 필요하다.

반도체설계교육센터는 학습 의욕이 높은 학생들이 반도체 분야에 깊은 관심을 두고 경제적 어려움 없이 자신의 꿈을 펼칠 수 있도록 앞으로도 지원

#### E<sup>2</sup>L

고급 교육자료를 언제든지 다시 볼 수 있는 최적의 조건을 이공계 학생 및 산업체 인력에게 제공할 수 있도록 교수님들의 많은 관심과 적극적인 참여를 바랍니다.

- 신규 교육자료 제출 방법

- •교육자료 종류 : 강의자료, 동영상 자료, 시험문제(답안지 포함) 등

- 제출 서류 : 교육자료 등록 신청서와 교육자료

- 제출 방법 : 담당자에게 메일(silee@idec.kaist.ac.kr) 발송

- •분야: 반도체공학, 디지털시스템, 아날로그회로, 집적회로, 통신 & 신호처리, SoC. 초고주파회로. 컴퓨터 구조 등

- 종류 : 강의자료(PPT,PDF,HWP), 시험문제, 동영상 자료

#### ●동영상 강의자료 제작 안내

동영상 강의 제작(제작비 무료)을 희망하시거나 동영상 자료를 보유하고 계신 교수님들의 많은 참여를 바랍니다. 제작을 희망하실 경우 동영상 자료는 신 청자가 IDEC을 방문하여 녹화할 수도 있고, IDEC이 신청자를 직접 방문하여 녹화할 수 있습니다.

다운받으신 자료에 대한 소감 및 의견을 홈페이지(http://edu.idec.or.kr)에 남겨주시면 사용자들의 의견을 적극 반영하여 양질의 교육자료가 많이 공유될 수 있도록 더욱 노력하겠습니다.

\* 문의 : 이승자 (042-350-8536, sjlee@idec.kaist.ac.kr)

## 독자 여러분들께

IDEC Newsletter는 매월 알찬 정보와 소식을 담아 독자여러분들을 찾아뵙고자 노력하고 있습니다.

뉴스레터를 보고 느낀점. 앞으로 다루어주었으면 하는 의견이 있으면. 100자 분량으로 보내주시기 바랍니다.

좋은 의견을 보내주시는 독자분들께는 IDEC 상품권을 보내드립니다.

\* 보내실 곳 : 전항기 (jhg0929@idec.kaist.ac.ki

IDEC Newsletter • 04 | 05

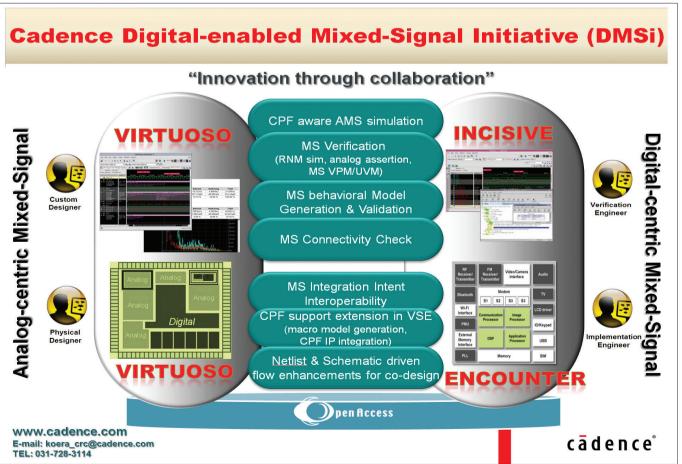

## **IDEC** Distinguished Lecturer

## About the Program

IDEC에서는 반도체 관련 분야 저명한 강사님들을 모시고 IDLP를 시작하게 되었습니다. 전국 대학. 기업체, 연구소 등 다양한 기관에서 훌륭한 초청 강연을 보다 손쉽게 접할 수 있는 기회가 되기를 희망합니다. 기술 세미나, 워크샵 등에 본 프로그램의 강사님들을 초청하시어 그 분들의 생각, 비젼, 지식을 공유하시기를 기대합니다. 더불어, 본 프로그램에 강사님으로 활동하실 분들의 적극적인 관심과 참여를 부탁드립니다.

#### **Current Lecturers**

Lecture 1

A Path Towards Efficient Design and Verification of Analog /Mixed-Signal Systems Noise and Aperture Analysis of Clocked Comparators Lecture 2

based Serial Links

Lecture 3

What Designers Want from Analog Circuit Optimizers :Myths and Truths Equalizer Design and Performance Trade-offs in ADC-

Signal Integrity Design of TSV Based 3D IC

Lecture 2 Wireless Power Transfer using Magnetic Field Resonance

Understanding electrical detection of Bio molecule using

신영수 교수 (KAIST)

홍성철 교수

High-Performance and Low-Power ASIC Design Using Pulsed-Latches

Low-Power Low-Leakage VLSI Design: Circuits, Design Methodologies, and Best Practice

강연자와 직접 연락하셔서 강연에 관한 사전 협의(날짜, 장소, 강연 내용)를 해주시기 바랍니다. 강연 관련 비용은 IDEC에서 지불하니, 강연 신청 기관에서는 지불하실 필요가 없습니다. 신청관련 및 자세한 사항은 홈페이지(http://idlp.idec.or.kr)을 참고 바랍니다.

문의: 전항기 (042-350-8535, ihq0929@idec.kaist.ac.kr)

##

# 시스템 수준설계 기술동향

#### 광운대학교 컴퓨터공학과

이준환 교수

연구분야: Electronic system level design, Computer vision

based user interface High-level testing E-mail: ioonhwan.vi@gmail.com

## 서론 - 시스템 수준 설계기술의 중요성

System-on-a-chip(SoC)으로 대변되는 시스템 반도체 설계에서 시스템 구조설계 또는 시스템 수준 설계는 필수적인 설계단계이다. 반도체 공정기술의 발달로 급증하는 집적능력을 충분히 활용하기 위하여 시스템 반도체의 설계복잡도가 증가하게 되었다. 즉. 하나의 칩에 많은 기능블록을 집적하거나 보다 복잡하지만, 고성능의 기능 블록을 추가하게 된다. 하지만, 이러한 설계복잡도의 증가 속도보다 설계자의 설계생산성은 그에 미치지 못하는 문제가 심화하였다. 이러한 문제를 해결할 수 있는 방법의 하나로 시스템 수준 설계기술이 주목 받고 있다. 다시 말해, 설계 추상화수준 (design abstraction level)을 기존 register transfer level(RTL) 또는 그 이하 수준에 서 상위수준인 시스템 수준(electronic system level 또는 ESL) 으로 올림으로써 설계 생산성을 높일 수 있다.

| Time  | Level of abstractions         | Design size<br>(unit: gate count) | Languages             | Simulationspeed<br>for an SoC<br>(cycles per second) |  |

|-------|-------------------------------|-----------------------------------|-----------------------|------------------------------------------------------|--|

| 2000s | Electronic system level (ESL) | 10M+                              | C/C++/SystemC         | 100 ~ 100M+                                          |  |

| 1990s | Register transfer level (RTL) | 100K ~ 1M                         | Verilog, VHDL         | ~30                                                  |  |

| 1980s | Gate level (GL)               | 1K ~ 10K                          | Schematic             | NA                                                   |  |

| 1970s | Transistor level (TL)         | ~ 100                             | SPICE netlist, layout | NA                                                   |  |

표 1. 시대별 설계 추상화 수준 및 그 특성

추상화 수준을 높여서 설계생산성을 높일 수 있는 것은 위 표 1에서 보는 바와 같이 지난 수십 년간의 경험을 통해 이미 증명된 바 있다. 각 추상화 수준이 설계 시작점(design entry)으로 사용되기 시작한 연대와 효과적으로 설계할 수 있는 크기(design size)와 사용되는 언어들을 표시했다. 보는 바와 같이 시스템 수준 설계에는 SystemC 또는 C 계열의 언어를 사용한다.

또한, RTL 및 ESL의 경우, 약 1천만 gate count 크기의 SoC의 시뮬 레이션 속도를 초당 시뮬레이션 cycle 수(cycles per second 또는 cps)로 보인다. 보는 바와 같이 RTL의 경우 약 30cps 수준이지만. ESL의 경우 수백 million cps까지도 가능하여 거의 실제 chip의 속도에 육박하기도 한다. 이러한 고속의 시뮬레이션 속도로 말미암아 시스템 전체의 동작을 과학적이고 정밀하게 분석할 수 있게 된다. 예를 들어, SoC 내의 모든 블록이 300MHz clock으로 동작한다고 가정할 때. 실제 1초 시나리오를 시뮬레이션하는데 RTL은 10 million seconds

(약 115일)가 소요된다. 반면, 100Kcps 속도의 ESL 모델은 1 kilo seconds(1시간 이하)이 소요된다. 흔히 시스템 구조분석을 위해 2~3초 시나리오를 수백 번 이상 수행하기 때문에 RTL 시뮬레이션을 통한 시스템수준 설계가 불가능하게 된다.

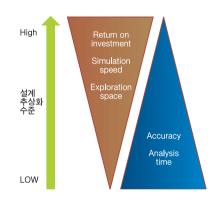

그림 1에서 보이는 바와 같이 같은 정도의 설계노력을 기울일 때, 상위 수준에서 설계활동이 이루어질수록 그 효과가 커지는 것은 주지의 사실이다.

그림 1. 설계 추상화 수준에 따른 설계 생산성 변화

현재 수천만 gate가 넘는 크기의 SoC들도 RTL에서 설계를 하고는 있다. 하지만, 제품의 경쟁력을 극대화하기 위해서는 추상화 수준을 높여 경쟁력 있는 제품을 생산하는 것이 매우 중요하다. 특히 막대한 설계비용이 투입되는 SoC 설계의 경우, 규모의 경제를 통한 투자 자금 회수 및 이익 창출이 필요하다. 즉, 시장의 제 1 또는 제 2공급자가 되어야 이익창출 및 재투자를 할 수 있는 선순환 구조를 갖게 된다. 예를 들어. 하나의 SoC 개발에 수백억에서 수천억 원 이상의 투자 비용이 필요한 모바일 모뎀 SoC 시장에서 미국 퀄컴사의 시장점유율이 지배적으로 큰 것을 생각해 볼 수 있다. 퀄컴을 제외하면 모바일 모뎀 SoC 시장에서 사업을 영위하는 회사의 수는 손에 꼽을 정도로 그 수가

RTL기반의 전통적 설계기술의 한계를 보여주는 의미 있는 설문결과 를 살펴보자. 2003년 Embedded Market Forecasters가 수행 한 설문결과에는 947명의 세계 유수 반도체 회사 엔지니어들이 참여 했는데, 다음과 같은 결과가 나왔다.

- 2. 설계 전 성능요구사항을 50% 이상 만족시키지 못하는 설계가 30% 이상

- 3. 약 54%의 설계가 평균 4개월의 일정지연을 경험

- 4. 45,000건의 설계가 시작되어 약 13%인 6,000건이 취소

이러한 설계문제들의 원인으로는 다음과 같은 이유로 응답하었다.

- 전체 시스템에 대한 제한된 visibility 응답자의 65%

- 제한된 문제 추적 (limited ability to trace) 54%

- 시스템의 수행을 제어할 수 있는 한계 (limited ability to control execution) - 42%

위의 설문 결과는 전통적인 설계기술의 한계를 잘 보여준다. 제시된 문제의 원인을 통해 블록수준이 아닌 전체 시스템 수준에서의 설계 필요성을 확인할 수 있다.

SoC 또는 시스템 반도체 설계 생산성 제고를 위해 또는 설계의 성공 을 위해 필수적인 시스템 수준 설계 기술들의 현황 및 한계를 살펴 보고, 이를 극복하기 위한 주요 연구 주제들을 소개한다.

## 본론 – 시스템 수준 설계기술의 현황과 문제

시스템 수준 설계기술은 크게 두 가지 특징이 있다. 첫 번째 특징은 시스템 수준 하드웨어 모델(앞으로 ESL 모델이라 함)을 이용하여 이루어진다. 주로 C 계열 언어를 이용하여 하드웨어의 동작을 기술 한다. 전체 시스템을 실제 시나리오를 이용하여 고속 정확하게 시뮬 레이션할 수 있는 ESL 모델의 개발이 시스템 수준 설계 활동의 성패 를 좌우한다 해도 과언은 아니다. 두 번째 특징은 실제 target binary 를 소프트웨어로 이용한다는 것이다.

즉, PC에서 개발한 상위수준 source code를 가공하여 소프트웨 어를 대체하는 것이 아니라 이를 실제 프로세서용 컴파일러를 이용 하여 target binary를 만든 후 이를 ESL 모델에 탑재하여 시스템 수준 시뮬레이션을 한다. 이렇게 함으로써, 실제 시나리오에 따른 시스템의 동작을 면밀히 분석하고 최적화할 수 있게 된다.

시스템 수준 또는 ESL은 RTL보다는 높고 알고리즘보다는 낮은 수준 이다. RTL에서도 behavioral level, synthesizable level, 심지어 gate-level 설계까지 다양한 추상화 수준이 가능하듯이 시스템 수 준에서도 목적에 따라 다양한 추상화 수준이 존재한다. 그중에서 대 표적으로 유용한 ESL 모델의 추상화 수준을 살펴보면 다음과 같다.

- Programmer's view (PV) level

- Programmer's view with timing (PVT) level

- Verification view (VV) level

PV level은 소프트웨어 programmer를 위한 수준으로 시스템 내의 모든 하드웨어 동작을 register-accurate한 수준으로 설계하는 ESL 모델의 수준이다. 소프트웨어가 하드웨어의 동작을 제어할 때 이용하는 유일한 통로가 하드웨어 블록의 register들이기 때문에 하드웨어의 동작을 register-accurate하게 설계한 ESL 모델은 실제 소프트웨어와 상호작용이 가능하다. 이러한 register-accuracv는 실제 target binary를 ESL 모델에 올려 시뮬레이션하기 위한 최소한의 요구사항이기도 하다. PV level에서는 하드웨어의 동작수행에 소요 되는 시간인 latency에 대한 정보가 없다.

반면 PVT level에서는 하드웨어의 latency 정보를 추가하여 하드 웨어와 소프트웨어 간의 상호작용 뿐 아니라 그에 소요되는 시간까지 시뮬레이션할 수 있다. 물론 이때 timing 정보의 정확도를 RTL수준 으로 하면 할수록 시뮬레이션 속도가 낮아지는 문제가 발생하게 되어 시스템 수준의 구조설계 관점에서 유의한 수준의 정확도를 설정해야

마지막으로 W level은 말 그대로 설계검증을 위한 ESL 모델의 추상화 수준으로 C 버전의 RTL 설계이다. 따라서 기능 및 timing 정보가 정확한 반면 시뮬레이션 속도는 PV나 PVT level보다 현저히 느리게 된다. 보통 PV level은 million cps 수준, PVT level은 100K cps 안팎, 그리고 VV level은 수백 cps 수준의 시뮬레이션 속도를 보인다. 현저하게 큰 차이가 남을 알 수 있다.

실제 target binary 소프트웨어와 ESL 모델을 이용한 고속 정확한 시뮬레이션을 바탕으로 다음과 같은 시스템 수준 설계활동들을 수행할

- 구조탐색 및 최적화

- 조기 소프트웨어 개발

- 시스템 수준 전력소모 예측

- Behavioral synthesis

<del>-</del>

이러한 설계활동들은 하드웨어와 소프트웨어를 동시에 이용하기 때문에 보다 실제 시나리오에 가까운 환경에서 시스템 전체의 성능을 최적화하거나 개발기간을 단축하는 목적을 가진다.

구조탐색 및 최적화는 하드웨어와 소프트웨어를 동시에 고려하여 다양한 시스템 구조를 탐색하여 최적의 결과를 얻는 활동이다. 시스템의 동작뿐 아니라 성능까지 시뮬레이션 되어야 하므로 PVT level의 ESL 모델을 이용한다. 아직 알고리즘 단계에 있는 블록의 경우, 이를 소프트웨어로 구현할 경우와 하드웨어로 구현할 경우로 나누어 전체 시스템의 성능변화를 측정하고 주어진 요구조건에 맞는 최적의 하드웨어-소프트웨어 partitioning을 찾을 수도 있다. Partitioning 후에는 하드웨어와 소프트웨어 간 인터페이스에서 일어나는 일을 면밀히살펴 최적화하는 작업도 포함된다. 시스템 성능에 큰 영향을 주는 외부 메모리의 접근 횟수를 줄이기 위한 상위 알고리즘 또는 하드웨어/소프트웨어의 기능 최적화도 매우 중요한 활동 중하나다. 또한, cache size, on-chip memory size, bus topology 등 미세한조정에 따른 시스템의 성능변화를 분석하여 최적화하는 것도 구조탐색 및 최적화 활동에 포함된다.

실례로 저자가 산업체에서 근무하던 시절에 모바일 모뎀 SoC 구조설계에 ESL 모델을 적용하여 성능개선에 큰 효과를 얻은 바 있다. 휴대단말용 모뎀 SoC의 주요기능은 무선으로 수신된 packet data - header와 payload로 구성 - 를 정해진 목적지(메모리 또는 IO device를 이용한 외부 칩으로 전송)로 전달하는 것이다. 이를 위해 서는 정해진 시간 간격으로 많은 양의 packet data header를 해석하여 payload를 정해진 목적지로 전달해야 하는데, 이 과정에서 packet data를 외부 메모리에 쓰고 읽는 동작을 수차례 반복하게된다. 이렇게 많은 양의 data를 외부 메모리에 쓰고 읽는 동작은 시스템성능에 커다란 악영향을 주게 된다. 외부메모리 접속비용과 시스템성능 간의 관계는 주로 하드웨어 엔지니어들이 이해하고 있으나, 이들은 모뎀의 동작 알고리즘을 모르기 때문에 이러한 최적화를 수행하기 어렵다.

반대로 알고리즘 엔지니어는 외부메모리 접속이 시스템 성능에 미치는 영향을 이해하지 못하는 경우가 대부분이다. 경험 많은 시스템 엔지 니어가 해결할 수 있는 문제이기는 하나 정확한 시뮬레이션 없이 알고 리즘 변경에 따른 외부메모리 접속 횟수 감소 및 시스템성능 개선 효과를 계산하는 것은 상당히 보수적일 수밖에 없다. 또한, 알고리즘 변경을 위해 추가적인 하드웨어가 필요했는데, 이쯤 되면 복잡한 성능 변화를 손으로 계산하기도 어렵게 된다. 어렵사리 많은 가정을 도입 하여 개선 효과를 계산하더라도, 그 수치가 뚜렷이 크지 않은 이상 추가 하드웨어 설계와 같은 커다란 추가비용을 결정할 수 있는 경우는 매우 드물다. PVT level ESL 모델을 이용한 시뮬레이션 결과의 정량 적 분석을 통해 알고리즘 수정 및 하드웨어 추가를 통해 평균 60% 이상의 성능개선이 가능함을 확인했다. 반면 손으로 계산한 보수적 예상 개선 효과는 30% 미만으로 나왔다. 보수적 계산과 시뮬레이션 결과의 차이가 큼을 알 수 있다. 또한, 추가된 하드웨어에 direct memory access controller(DMAC)가 포함되어 packet data를 외부 메모리로 전송했는데, DMAC가 접근하는 영역을 noncachable로 설정해야 하는 것을 검증과정에서 시행착오를 거쳐 알게 되었다. DMAC를 이용한 경험이 없던 터라 시스템 수준 설계를 통해 구조설계/최적화에 따른 설계변경 내용의 검증이 가능했다.

조기 소프트웨어 개발은 PV level ESL 모델을 하드웨어로 삼아 실제 소프트웨어를 개발함으로써 전통적인 설계기술보다 일찍 소프트웨어 검증이 가능함을 의미한다. 전통적인 RTL이하 설계기술에서는 실제 소프트웨어를 하드웨어에 올려 integration test를 시작하는 시점이 기껏해야 하드웨어를 FPGA보드에 구현하는 시점이 되어야 한다. 모바일 모뎀 SoC의 경우, 표준의 알고리즘 설계 그리고 RTL 설계가 끝난 후(약 2년여 소요)에나 이러한 integration test가 가능해진다. 반면 PV level ESL 모델은 알고리즘 구현 후(약 1년여 소요)부터 개발이 가능하기 때문에 integration test가 조기에 가능하다.

보통 SoC 또는 임베디드 소프트웨어의 상당 부분이 하드웨어와의 상호작용이 빈번함을 감안할 때, integration test에 필요한 시간이 길고 중요함을 알 수 있다. 이러한 조기 소프트웨어 개발의 효과는 비단 소프트웨어 개발에 그치는 것이 아니라 하드웨어 개발에도 좋은 feedback으로 사용될 수 있다. 즉, 소프트웨어와의 상호작용을 효율적으로 하기 위해 하드웨어 일부가 변경되거나 새로운 하드웨어가추가되는 등의 feedback이 가능하다.

ESL 모델을 이용한 조기 소프트웨어 개발 예로는 Motorola, Nokia, 삼성전자와 같은 휴대전화 제조사의 phone simulator가 있다. Phone simulator는 휴대전화의 하드웨어들을 PV level ESL 모델로 구현한 것으로 휴대전화 소프트웨어를 integration하는 목적으로 사용된다. 휴대전화 개발기간의 대부분이 이 integration 작업임을 감안할 때, 그 효과가 매우 크리라 예상된다. 특히 자사 탑재 칩을 대부분 자체 생산한 Motorola사가 phone simulator 개발에 적극적이었는데, 이는 미리 칩 개발정보를 이용하여 칩 개발 전 휴대전화 소프트웨어 개발을 다양한 국가/모델에 맞춰 개발함으로써 향상된 기능의 휴대전화를 한발 앞서 개발하기 위한 목적이 크기 때문이다.

또 다른 예로는 저자가 산업체에 근무할 당시, operating system (OS) porting을 칩 생산 전 PV level ESL 모델을 이용하여 수행한 후 칩 fab-out 당일 OS porting을 완료한 사례이다. 전통적인 설계 방식에서는 OS porting은 칩 생산 후 4~6주 정도 소요되는 작업 이므로 최소 4주 이상의 개발기간을 단축하였다. 일반적으로 FPGA 보드를 이용한 OS porting은 불가능하다. 왜냐하면, FPGA보드로 구현한 시스템과 실제 칩 시스템은 여러모로 다른 register interface 및 다른 기능블록들이 존재하기 때문이다.

시스템 수준 전력소모 예측 또한 매우 중요한 시스템 수준 설계활동 중 하나이다. 그 이유는 전통적인 RTL이하 전력소모 예측은 SoC 전체에 적용할 경우, 분석속도가 너무 느리거나 분석결과가 정확하지 않은 반면 시스템 수준 전력소모 예측은 빠르면서 정확할 수 있기 때문이다. 현재 SoC 전체의 전력소모 예측은 RTL이하 전력소모 예측 기술의 특성상 시뮬레이션 결과를 이용한다. 앞서 언급한 바와 같이 SoC 전체를 RTL에서 시뮬레이션하는 것은 현실적으로 불가능하다.

따라서 현실적인 대안으로 SoC 내 하드웨어 블록마다 최대전력을 소모할 수 있는 시나리오를 상정하여 전력소모를 예측한다. 그 후 각 블록의 전력소모 값의 합을 SoC의 예측 전력소모로 계산하는데, 이는 흔히 실제 SoC의 전력소모량과는 서너 배의 큰 차이를 보인다. 실제 시나리오 수행 시 SoC 내의 모든 IP 블록들이 최대전력을 소모하는 경우는 극히 드물거나 없기 때문이다. 주어진 시나리오에 따른 블록 수준의 전력소모 예측은 RTL이하 수준에서 매우 정확하지만, 전체 SoC의 전력소모 예측은 불가능한 수준이다. 반면, ESL에서 실제 시나리오를 이용한 전체 SoC의 시뮬레이션은 가능하다. 다만, 정확도가 높은 ESL 전력모델(power model) 생성 자동화를 통한 ESL 전력소모 예측 정확도 항상이 중요한 연구과제이다.

현재 ESL 전력예측에 관한 부분은 대부분 학계에서 연구되고 있는 내용이 대부분이다. 몇몇 선도적인 기업들이 ESL 전력모델 생성 또는 ESL 전력소모 예측기술을 상용화하여 시장에 진입하였으나, 현저히 낮은 예측 정확도나 수동 전력모델 생성 등의 문제로 사라져 갔다. 특히 ESL 전력모델의 정확도 향상에 관한 논문들이 대부분이며, 주로 전력모델링 대상 설계블록의 동작 이해를 바탕으로 전력모델을 생성하기 때문에 엔지니어의 동작 이해 정도에 따라 전력모델이 가변할수 있고 전력모델 생성 자동화가 불가능한 문제가 크다. 매우 활발한연구활동이 이루어지는 분야로 주목할 만하다.

마지막으로 behavioral synthesis 기술은 ESL 설계를 RTL 설계로 합성(synthesis)하는 기술로, ESL 모델을 design entry로 하는 top-down design flow 실현을 위해 필수 불가결한 설계 자동화 기술이다. 이미 많은 연구가 진행되었고, 상용툴로 시장에 선 뵌지도 10년여가 되어간다. Mentor Graphics사의 CatapultC와 Forte사의 Cynthesizer 등이 시장 지배력을 확장하고 있으나, 저자의 산업체 재직 시 경험에 의하면 아직 SoC 구현 flow에 들어갈 정도로 성숙한 툴은 아니다. 즉, 툴 사용자가 툴의 기능을 많은 부분 이해하여 어떠한 style의 C 계열 입력 코드를 넣어야 원하는 RTL 코드가 출력되는지 알고 써야 하는 수준이다. Logic synthesis tool들도 synthesizable 코드가 존재하지만, 정의가 잘 되어 있고 C 계열 언어와 달리 hardware description language의 syntax가 복잡하지 않기 때문에 입력 코드의 style이 잘 정의되어 있다. 또한, CatapultC의 경우, C++ 코드를 입력으로 받는데 datapath 합성에는 매우 효과적이나 control 회로 합성에는 취약한 면이 있다. SystemC 설계를 입력 받는 Cynthesizer의 경우, datapath와 control 회로합성이 효과적 이긴 하지만 SystemC 설계 수준이 RTL에 가까운 낮은 수준이라는 것이 문제 중 하나이다.

SoC 설계는 이미 많은 구성 블록들이 RTL이하 수준 intellectual property (IP) circuit으로 존재하고 있기 때문에, ESL 모델을 개발할 때 RTL IP를 reference로 삼아 bottom—up 방식으로 개발하게 된다. 특히 PVT level ESL 모델을 개발할 경우, RTL IP와의 timing accuracy가 100%가 아니라는 사실로부터 시스템수준 설계결과의 신뢰성이 의문시될 수 있다. 또한, PVT level ESL 모델을 개발하는 것 자체도 큰 진입 장벽 중 하나로 작용한다. 즉, 설계언어 학습에서 부터 RTL IP로부터 ESL 모델을 개발하는 설계기술까지 많은 투자가

필요하기 때문이다. 이러한 문제들을 해결하기 위해 RTL 코드를 컴파일 하여 ESL 모델을 자동생성 해주는 설계자동화 툴도 있으나, 결과물인 ESL모델의 시뮬레이션 속도가 RTL대비 10~100배 정도 개선되는데 그치는 단점이 있다.

## 앞으로 할 일

ESL 모델의 정확도 문제를 불식시키기 위해서는 top-down 설계 flow를 SoC 구현 flow로 정착시키는 것이 가장 효과적인 방법이다. 즉, 모든 설계를 알고리즘 설계 후 ESL 모델을 먼저 만들고 이를 이용하여 RTL 설계를 하는 것이다. 이때, ESL 모델의 latency는 timing constraint로 활용되고 RTL 구현상 ESL 모델의 latency와 같거나 적은 수행시간을 갖게 되는 것은 문제가 되지 않는다. 이러한 top-down design flow 정착에 필수적인 기술이 앞서 언급한 behavioral synthesis 기술이다. 1990년대 logic synthesis 기술의 성숙으로 말미암아 design entry가 gate-level에서 RTL로 급격히 변하는 것을 경험한 바 있다. 유사하게 behavioral synthesis 기술의 성숙에 따른 ESL로의 design entry 변화 및 top-down design flow의 정착을 어렵지 않게 예측할 수 있다.

이러한 변화에 대응하기 위해서는 시스템 수준 설계기술에 대한 지속적인 연구와 더불어 고급인력 양성을 위한 지속적이고 전략적인 노력을 게을리하면 안 되겠다. 우리나라 SoC 설계 경쟁력 확보를 위한 투자로 지금이 가장 적기라 생각된다. 특히, 국가 R&D 과제로 추진되는 SoC 설계과제들부터 이러한 시스템 수준 설계기술의 활용을 장려하는 것이 좋은 시작점이 되리라 생각한다. 또한, 이러한 상위수준설계기술에 투자할 수 없는 중소기업들을 위한 방안도 고려되어야할 것 같다.

끝으로 시스템 수준 설계기술의 활용뿐 아니라 관련 설계 자동화 기술의 연구개발 및 사업화를 위한 투자도 고려해 볼 필요가 있다. 시스템 수준 전력소모 예측기술은 아직 연구단계로 전 세계 반도체 설계 자동화 시장을 석권하고 있는 미국이나 유럽회사들에서조차 독보적인 기술을 확보하지 못한 상황이다. 전력소모 예측기술은 다른 시스템 수준 설계 활동과 별개로 독자적인 시장 창출이 가능한 분야이기도 하다. 이미 다른 시스템 수준 설계기술들은 기존의 설계 자동화 툴 시장의 강자들이 기술을 확보하고 시장을 지배해 가고 있지만, 시스템 수준 전력소모 예측기술은 좋은 연구성과를 바탕으로 우리나라의 설계자동화 툴 산업을 태동하게 할 수 있는 좋은 분야라 생각된다. 특히, 세계적인 경쟁력을 확보한 각종 정보기기 단말생산 업체와 반도체 업체를 보유하고 있는 우리나라의 산업환경을 고려할 때, 툴 개발에 우호적인환경이 조성되어 있다 하겠다.

## 기술동향컬럼

## CCTV 영상 보안 시스템의 보안 위협 및 대응 방안

#### 안양대학교 컴퓨터공학교

http://cad.anyang.ac.kr

강민섭 교수

연구분야: 네트워크 보안, RFID/USN, 스미트그리드 E-mail: mskang@anyang.ac.kr

#### 안양대학교 컴퓨터공학과

강민석

연구분야: 정보보안, 스마트그리드, Zigbee E-mail: volof7lv@anyang.ac.kr http://cad.anyang.ac.kr

CCTV(Closed Circuit Television: 폐쇄회로 TV)는 화상정보를 특정의 목적으로 특정 사용자에게 전달해 주는 시스템으로, 초기 금융 기관 등의 범죄 방지용으로 사용되었으나, 최근에는 가정, 학교, 회사, 공공기관 등 사회 전반으로 그 사용범위가 넓어지고 있다[1]. 특히 각종 범죄가 증가함에 따라 CCTV는 방범용으로 사용하는 등 적용범위가 기하급수적으로 증가하게 되었으나, 방범 등의 목적으로 설치, 관리하는 CCTV의 영상정보는 정보의 유출 위험에 무방비 상태로 노출되어 있어 언론을 통해 그 문제점이 심각하게 부각되고 있다 [1,2].

현재 CCTV의 보안체계는 너무 허술해 사생활침해를 넘어 영상정보가 불법적인 조작을 통하여 사실관계가 바뀌거나 결정적인 증거 등이 고의적으로 파기될 위험성도 있다. 케이블 연결은 중간에 또 다른케이블을 따로 연결하면 영상을 훔쳐보거나 저장하는 것이 가능하며, 방화벽 없이 카메라와 관제센터를 인터넷으로 연결한 경우에도 해킹을통해 영상정보가 제삼자에게 유출될 수 있다[1,2,3,5].

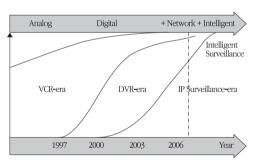

영상 보안에서 초창기에는 VCR 저장장치 기반의 아날로그 기술을 기반으로 하여 CCTV 카메라로부터 획득된 영상정보를 폐쇄적인 유선 전송로를 이용하여 관제센터로 전송하면 관리자가 모니터를 통하여 직접 영상을 감시하였다. 그러나 IT 기술의 발달과 더불어 DVR 기반의 영상압축 및 디지털 전송기술을 사용하는 이른바 디지털 시대로 발전하였으며, 최근에는 광대역 통신망 및 개방 프로토콜을 사용하는 IP 기반의 네트워크와 영상 자동분석 및 인식 기술이 결합한 지능형 영상보안 기술로 진화하고 있다 [1,2,5].

기존의 디지털 영상 보안 시스템의 대부분은 현장단의 카메라로부터 Video Server로 압축되지 않은 데이터를 전송하면 Video Server 는 영상 압축 알고리듬을 통하여 영상정보를 압축하여 관제센터에 있는 View Server로 정보가 전송된다.

이러한 기존의 방법은 네트워크를 통하여 Video Server에서 View Server로 전송되는 구간을 해킹하여 데이터의 고의적인 조작이나 파기 등의 위험성에 노출되어 있다[3,4,5]. 이에 본고에서는 보안이 취약한 현장단과 관제센터 간의 네트워크상에서 영상 시스템의보안 위협에 대한 문제점을 알아보고, 기존의 영상 시스템에서의데이터 변조나 해킹 등의 보안 문제를 해결하기 위한 대응 방안에대해서 기술한다.

## 보안 위협 요소

[그림 1]은 영상보안 기술의 진화 과정을 나타낸 것이다. 영상보안 시스템의 기본구성은 영상촬영을 위한 CCTV 카메라, 영상을 볼 수 있는 디스플레이 장치, 카메라와 디스플레이 장치를 연결시켜 주는 전송망, 영상을 저장할 수 있는 저장매체로 요약할 수 있다[2,5].

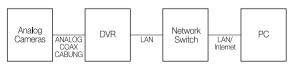

## ■ Network DVR을 통한 아날로그 CCTV 시스템

초창기의 VCR을 통한 아날로그 CCTV 시스템 방식[5]은 영상을 아날로그 방식으로 받아 폐쇄적인 유선 전송로를 이용하여 전송하고 VCR에 저장, 관리자가 모니터를 통하여 직접 감시하던 시스템을 말한다.

그림 1. 영상 보안 기술의 진화 [2]

이는 아날로그 방식의 비디오 테이프를 사용하였기 때문에 관리 비용과함께 데이터 취급 및 사용에 많은 문제점이 있었다. 또한, 모니터와 VCR은 보여주는 기능과 저장하는 기능 밖에 없으므로 수동적인 시스템이고 그 때문에 감시자는 지속적으로 모니터를 주목해야 하는 문제점이 있다[2,5]. 90년도 후반부터는 IT 기술의 진보로 아날로그 CCTV로부터 획득된 정보를 DVR(Digital Video Recorder)을 사용하여디지털로 변환하여 하드디스크 등의 디지털 저장장치에 기록하는방식이 개발되었다. [그림 2]는 Network DVR을 통한 아날로그 CCTV 시스템을 나타낸다[5].

그림 2. Network DVR을 통한 아날로그 CCTV 시스템 [1]

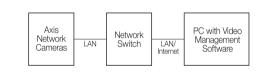

## ■ IP 카메라를 사용한 CCTV 시스템

최근에는 인터넷 프로토콜(IP)을 사용하여 감시 영상을 전송, 저장, 모니터링 할 수 있는 IP Surveillance 영상보안 시스템으로 전환하는 추세이다. 비슷한 개념으로 현재 시장에서는 네트워크기능이카메라에 접목되는 기술을 사용한 CCTV 제품들을 일컬어 NVR(Network Video Recorder)라고도 불린다. 일반적으로 DVR은 16채널을 지원하지만, IP Surveillance는 네트워크 대역폭까지 설치 채널에 제약이없으며[3], 영상정보를 획득하는 과정에서 소프트웨어와 융합하여지능형 영상 제어가 가능하다. [그림 3]는 인터넷, 인트라넷, 전용선등을 이용하여 CCTV 영상정보를 NVR 서버로 전송하는 IP 카메라를 사용한 CCTV 시스템[1]을 나타낸다[5].

그림 3. IP 카메라를 사용한 CCTV 시스템

CCTV 영상정보를 감시·관리하는 보안관제센터에서는 보안 위협에 대해 적극적으로 대처하지 못할 경우 영상에 대한 기밀이 노출로 말미암은 심각한 보안 문제가 발생할 수 있다. 현재 국내에 설치되고 있는 CCTV 시스템에서 발생할 수 있는 보안 위협들은 CCTV 카메라와 연결된 VCR, DVR 서버의 동축케이블 또는 IP Surveillance의 LAN/WAN 선을 물리적으로 절단하거나, 동축케이블의 분배로 무단영상 획득 등의 물리적인 위협이 존재한다.

네트워크 기반의 CCTV 시스템은 관리를 위하여 고정된 공인 IP를 사용하거나, ISP(Internet Service Provider) 회사를 통한 유선 IP에 DDNS(Dynamic Domain Name Service)를 사용하여 도메인을 등록하여 사용할 경우, 이를 이용하여 공격자는 더욱 쉽게 크래킹하여 영상 정보를 획득할 수 있다[1,2,5]. 공격자는 도청을 통해 합법적인 사용자의 각종 정보를 훔쳐내어, 공격자 자신을 시스템에 합법적인 사용자로 인식될 수 있게 하거나 억지공격기법을 통하여 합법적인 사용자로 인식될 때까지 지속적으로 공격을 가할 수 있다.

## ■ 악의적인 공격자에 의한 보안 위협

악의적인 공격자가 CCTV 영상관제센터 및 영상 감시 네트워크에 연결 된 건물에 침입하거나 또는 방문 업체 직원으로 가장하여 DVR서버의 IP 주소를 검색하거나 조사하고, 시스템에 해킹 프로그램이나 바이러스, 악성코드를 삽입하고 시스템 제어에 필요한 기타 정보를 유출할 가능성이 있다. 또한, 공공기관 및 기업에 구축, 관리를 담당하는 업체의 담당자는 관리하는 장비의 IP 주소와 ID, 패스워드를 알고 있기 때문에 언제든지 정보를 유출할 수 있는 위험이 있다. 또한, 일부 업체에서는 공공기관에 구축한 사실을 다른 고객사에게 시연해 줌으로써 시연되는 CCTV 시스템의 정보가 유출될 수 있으며, 악의적으로 공격자에 의해 이러한 정보가 범죄에 사용될 가능성이 크다.

#### 대응 방인

[표 1]은 아날로그 CCTV 카메라 방식과 네트워크 기반 CCTV 카메라 방식에 대해 가이드라인에서 권장하는 개인영상정보 보호를 위한 기술적 조치 권고 사항의 일부를 나타낸다[3].

| 구분     | 조치사항                                                                                    | 비고          |  |

|--------|-----------------------------------------------------------------------------------------|-------------|--|

| 1 아들히  | 1-1. 개인영상정보를 DB 등에 집적하여<br>별도로 저장·보관하는 경우에는 이를<br>암호화한다.                                | 공통          |  |

| 1. 암호화 | 1-2. 개인영상정보를 정보통신망을 통해<br>외부로 전송하는 경우에는 보안 프로토콜<br>을 사용한다.                              | 네트워크<br>카메라 |  |

|        | 2-1. 관리책임자 및 업무 담당자의 개인<br>영상정보에 대한 접근 및 처리권한을 차등<br>부여한다.                              |             |  |

| 2. 접근  | 2-2 전보, 퇴직 등 인사이동이 발생하여<br>개인영상정보에 대한 접근권한이 변경<br>된 경우에는 지체 없이 당해 접근 권한을<br>변경 또는 말소한다. | 공통          |  |

| 통제     | 2-3. 개인영상정보에 대한 접근 권한<br>부여, 변경 또는 말소에 대한 내역을 기록<br>하고, 당해 기록을 5년간 보관한다.                |             |  |

|        | 2-4, IP 필터링을 통해 권한 없는 제 3자의<br>접근을 제어한다.                                                | 네트워크        |  |

|        | 2-5. SSL, IDS(침입탐지시스템) 등 홈페이지<br>보안 기술을 적용한다.                                           | 카메라         |  |

표 1. 개인영상정보 보호를 위한 기술적 조치 기준

위의 가이드라인에 맞추어 보안에 대한 대책[3]으로 첫째, 공격자가 추적하기 어려운 ID와 Password를 사용하고 정기적으로 암호를 바꾸

166호뉴스레터\_인쇄:레이아웃 1 11.04.01 오후 6:36 페이지 13

어야 하며, 둘째, 방화벽 또는 IP 필터링을 통해 관리센터와 각 CCTV의 등록된 IP를 제외한 네트워크 접근 허용을 차단하고, 셋째, 패킷의 헤더를 통해 웜바이러스 및 DOS(Denial of Service), DDOS(Distribute Denial of Service) 공격, 해킹 등의 유해 공격을 탐지하여 방화벽, IP 필터링을 작동시키는 IDS(Intrusion Detection System)를 도입하여 공격에 대비한다.

넷째. 다수의 네트워크 CCTV 카메라를 관리하기 위해 IEEE 802.1x 인증기법으로 인증기관에 대한 접근 요청, 인증 기관은 사용 자의 EAP 시작 메시지만 송신 허용하는 비인증 상태 유지, 인증 기관이 사용자 ID를 요구하는 EAP 메시지 송신, 사용자 ID 회신, 인증 기관 인증 서버에 전송, 인증 서버에서 인증 알고리듬에 의거 수락 혹은 거부 메시지를 인증 기관에 회신, 수락 시 인증 기관은 사용자를 인증 상태로 전환하여 통신하는 절차를 통한 중앙집중식 영상관제시스템 을 사용한다.

다섯째. 네트워크 카메라와 어플리케이션들 간에 영상 정보가 128 비트로 암호화되는 HTTPS(SSL(Secure Sockets Layer) over HTTP) 기법을 사용한다. 이는 표준으로 정해진 몇 가지 암호화 알고 리듬 중 하나를 선택하고, 서버 인증과 키 교환을 한 후, 클라이언트 인증과 키를 교환하고 연결 설정은 완료하고 두 개의 해쉬값의 연결 해주며 암호화 통신 환경을 만들어준다.

여섯째. CCTV 카메라와 중앙 관제 어플리케이션 또는 관리자 PC 간 의 완벽한 별도의 가상 터널을 형성하여 RSA(Rivest Shamir Adleman), DH(Diffie-Hellman), RC2(Rivest Cipher 2), RC4(Rivest Cipher 4), DES(Data Encryption Standard), 3DES, SHA-1, MD5, SEED, AES(Advanced Encryption Standard) 등의 다양한 알고리듬으로 터널이 구성된 네트워크로 전송되는 모든 영상데이터 가 암호화되도록 한다.

일곱째. CCTV 영상 감시 네트워크는 물리적 또는 VLAN으로 기업 내부의 데이터 네트워크 망과 분리해 동일한 백본 상의 혼용을 철저히 통제하여 네트워크에 공격할 수 있는 여지를 미연에 방지한다. 여덟째. 영상에 대한 접근, 재생, 수정, 복사 등에 대한 권한 부여를 관제 센터 에서 엄격하게 통제하여야 한다. 아홉째, 국내 표준 대칭키 알고리듬 등을 사용하여 암호화된 형태로 물리 디스크 내에 안전한 영상 저장 기능을 제공하여야 한다. 열 번째, 영상을 찍음과 동시에 시간정보 및 촬영 위치, 촬영자 등의 워터마킹 정보 등은 LSB(Least Significant Bit)방식 등 정보 은닉 기법을 사용하여 저장하는 기능을 제공하여야

열한 번째, 임의의 프레임마다 서명(SIGN) 알고리듬을 적용한 무결성 검증 기능을 제공하고 기기 자체에 대해 합법적 기기인지에 대한 인증 이 필요하다. 열 두 번째, IP Surveillance의 경우 CCTV로부터 입력 된 영상에 사람 얼굴, 차량 번호와 같은 사생활과 관련된 정보가 포함 될 경우, IP Surveillance는 이 부분을 알아볼 수 없도록 부분 암호화 작업을 하고, 이후 적절한 권한을 가진 사용자가 범죄해결 등의 목적 으로 감시 영상을 조사할 필요가 있을 경우 권한을 가진 자의 인증을

얻어 암호화 이전의 정상적인 영상으로 복구하며, 권한이 없는 사용 자는 부분 암호화된 영상만을 보게 되어 개인 정보의 유출 우려를 보다 완화할 수 있다[3]

## 향후 방향 및 결론

CCTV는 쇼핑센터, 학교지역, 주차시설, 대중교통역사, 군대, 그리고 수많은 크고 작은 회사에 이러한 감시의 눈이 되어준다. 지금까지 CCTV 시스템에서 움직이는 영상에 대한 동작탐지 기술이 고도화 되고, 기술범위를 확대함으로써 감시지역에 대한 경계가 강화되고는 있지만, 비 또는 눈이 내리거나 나무가 흔들리거나 자동차가 움직일 때 이를 사람으로 오인하는 오탐지로 시간을 낭비하는 일도 자주 발생 한다. 그러나 최근에 지능형 감시 시스템이 새롭게 등장하여 감시 카메라에서 잡은 이미지를 처리해 실내외 환경에서 실제 사람의 존재 여부를 탐지하여 외부 출입자를 발견하면 운용자에게 알람을 통해 통보하고, 모니터에서 그 사람이 위치를 표시하는 시스템이 등장하고

또한, 방치된 물체 혹은 없어진 물체를 감지하거나 배회 되는 모습을 감지하고. 라인을 넘거나 역방향을 감지하여 관리센터에 알람 표시를 하는 지능형 영상 보안 시스템이 있고, 모션 트래킹을 통하여 이동 물체를 따라다니면서 촬영하거나, 카메라에서 포착된 개인 신상정 보만을 자동으로 모자이크 처리하는 마스크 기능, 배경을 무시하고 의미 있는 물체의 움직임만을 감지하는 지능형 영상 보안 시스템도 연구 중이다. 덧붙여 영상을 포함한 수많은 알람 정보 등을 고성능 의 자원을 같이 사용함으로써 암호화 전송 혹은 암호화 터널링 (VPN) 기술구현에 보다 한발 다가설 수 있다[1,5].

한편. CCTV. DVR. 그리고 IP 카메라 등 영상 보안 시스템 간 표준 프로토콜이 부재하여 사용제품 간 호환성이 없어 호환성 확보에 대한 요구가 강력히 제기되고 있는 실정으로 국내에서도 ETRI와 국내 기업 간의 표준 프로토콜을 마련하고 있다. 그러나 현재 전국에 설치된 많은 CCTV 시스템은 보안에 매우 취약한 구조로 되어 있다. 점진적 으로 암호화 및 터널링이 가능한 제품이 개발되고, 더욱 지능적인 역할을 수행할 수 있도록 제품이 개발되어야 할 것이다.

## Reference

- [1] 한국전자산업진흥회, CCTV 산업 동향, 2008, 01.

- [2] ETRI, 지능형 영상보안 기술현황 및 동향, 전자통신동향분석 제 23권 제 4호 2008, 08,

- [3] 이홍섭, cctv개인영상정보보호가이드라인해설서, 한국정보보호진 흥원, 2006.10.

- [4] 중소기업청. 영상보안 시스템의 시장기술 보고서, 중소기업청. 2009 10

- [5] 전범종, 디지털CCTV의 현황과 전망, 한국디지털CCTV연구조합, 2010. 04.

MPW(Multi-Project Wafer) Design Contest

# 2011 IDEC MPW 설계공모전

IDEC MPW 설계공모전을 통하여 자신이 설계한 IC를 국내 최고의 Foundry 업체에서 제작할 수 있습니다 여러분이 주인공이 되어 생각을 현실로 구현해 보십시오

#### ○ 2011년 MPW 공정 지원 내역

| 공정지원사      | 공정[ɹm]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 공정내역                                                      | size        | 칩수            | Package                             |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------|---------------|-------------------------------------|

|            | 0.13µm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMOS 1-poly 6-metal                                       | 4mm x 4mm   | 96            | 208pin QFP                          |

| 삼성         | 65nm(*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CMOS 1-poly 8-metal<br>(RF지원, Option(HRI, Inductor, MIM)) | 미정          | 20            | 208pin QFP                          |

|            | 0.13.mm CMOS 1-poly 6-metal 4mm x 4mm 96 65nm(*) (RFAIR) Option(HR] Inductor, MIM)) 미원 20 0.35.mm (Optional layer (DNW, HR], BJT, CPOU) 6-7) 0.18.mm (Optional layer (DNW, HR], BJT, CPOU) 6-7) 0.18.mm (Gmetala) Thus metals (BFAIR) 48-75 (Optional layer (DNW, HR], BJT, MIM) 6-7) 0.13.mm (CMOS 1-poly 6-metal (RFCMOS, Top : UTM) 5mm x 5mm 23 0.11.mm(*) (CMOS 1-poly 6-metal 5mm x 5mm 13 0.15.mm (CMOS 1-poly 4-metal 5mm x 5mm 15 0.03.mm x 5mm 15 0.03.mm x 5mm 15 0.03.mm x 5mm 15 0.03.mm x 5mm 25 0.18.mm CIS CMOS 1-poly 4-metal 5mm x 5mm 26 0.18.mm CIS CMOS 1-poly 4-metal 5mm x 5mm 27 0.18.mm RFCMOS RFCMOS 1-poly 4-metal 5mm x 5mm 27 0.18.mm RFCMOS RFCMOS 1-poly 6-metal 5mm x 5mm 20 0.18.mm RFCMOS RFCMOS 1-poly 6-metal 5mm x 5mm 4 0.18.mm SiGe SiGe BICOMOS 1-poly 6-metal 5mm x 5mm 4 0.5.mm x 5mm 15 0.5.mm CMOS 1-poly 6-metal 5mm x 5mm 4 | Design 144pin<br>Package 208pin QFP                       |             |               |                                     |

| 매그나칩/하이닉스  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (6metal을 Thick metal로만 사용가능                               | 4.5mm x 4mm | 80            | Design 200pin<br>Package 208pin QFP |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 5mm x 5mm   | 23            | 208pin QFP                          |

| 동부하이텍      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOS 1-poly 6-metal<br>(RFCMOS, Top: UTM)                 | 5mm x 5mm   | 13            | 208pin QFP                          |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOS 2-poly 4-metal                                       | 5mm x 5mm   | 15            | 144pin QFP                          |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           |             |               |                                     |

| TowerJazz  | 0.13um                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CMOS 1-poly 3-metal(MT)                                   | 5mm x 5mm   | 2             | 지원하지 않음                             |

| 1011010022 | 0.18µm RFCMOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RFCMOS 1-poly 6-metal                                     | 5mm x 5mm   | 4             |                                     |

|            | 0.18µm SiGe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SiGe BiCOMOS 1-poly 6-metal                               | 5mm x 5mm   | 1             |                                     |

| KEC        | 0 <u>.</u> 5μm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13.im                                                     | 20          | 28pin ceramic |                                     |

|            | 4μm BJT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BJT 1-poly 2-metal                                        | 3mm x 3mm   | 20            | 28pin ceramic                       |

#### ○ 2011년 MPW 진행 일정

|                 | 공정사           |                    |      | 우선모집     |          | 정규모집     |          | 후기              | DB마감       | DB전달     |          | Package  |

|-----------------|---------------|--------------------|------|----------|----------|----------|----------|-----------------|------------|----------|----------|----------|

| 구 분             |               | 공 정                | 제작칩수 | 신청마감     | 선정발표     | 신청마감     | 선정발표     | 접수시작<br>(선착순마감) | (Tape-Out) | (Fab-In) | Chip-out | -out     |

|                 | TowerJazz     | 0.18µm (SiGe)      | 1    |          |          | 10,10,31 | 10,11,15 |                 | 11,02,11   | 11,02,22 | 11,05,24 | 11,06,24 |

| 98회             | 매그나칩/<br>하이닉스 | 0.35μm             |      |          |          | 10.10.31 |          |                 |            | 11.02.25 | 11.06.07 |          |

|                 | 매그나칩/<br>하이닉스 | 0 <u>.</u> 18μm    |      |          |          | 10,10,31 |          |                 | 11,02,11   | 11,02,25 | 11,06,07 | 11,07,07 |

|                 | TowerJazz     | 0.18µm(RF)         |      |          |          | 10.11.20 | 10.12.06 |                 | 11.02.21   | 11.03.07 | 11.05.11 |          |

| 99회<br>(11-2)   | 동부            | 0.35μm<br>(BCDMOS) |      |          |          | 10,11,20 |          |                 |            | 11,03,09 | 11,06,01 |          |

|                 | 동부            | O,13μm             | 23   |          |          | 10.11.20 | 10.12.06 |                 | 11.03.21   | 11.04.06 | 11.07.06 | 11.08.06 |

| 100회            | 동부            | 0,35μm<br>(BCDMOS) |      |          |          | 10.12.05 | 10.12.20 |                 | 11.04.07   | 11.04.20 | 11.07.12 | 11.08.12 |

|                 | 삼성            | 0.13µm             | 48   |          |          | 10,12,05 | 10,12,20 |                 | 11,04,25   | 11,05,09 | 11,08,25 | 11.09.10 |

|                 | TowerJazz     | 0.18µm(RF)         | 2    |          |          | 10,12,15 | 10,12,30 | 11,02,01        | 11,05,02   | 11,05,16 | 11,07,19 | -        |

| (11-4)          | 매그나칩/<br>하이닉스 | 0.18μm             | 20   |          |          | 10.12.15 | 10,12,30 | 11,02,01        | 11,05,13   | 11,05,27 | 11,09,05 | 11,10,05 |

| 102회<br>(11-5)  | 동부            | 0,35μm<br>(BCDMOS) | 3    |          |          | 11,01,05 | 11,01,20 | 11,03,15        | 11,05,25   | 11,06,08 | 11,08,31 | 11,09,30 |

|                 | TowerJazz     | 0.18μm(CIS)        |      |          | 10,12,20 | 11,02,06 | 11,02,20 | 11,04,06        | 11,06,21   | 11,07,05 | 11,09,21 |          |

| (11-6)          | 동부            | 0.35μm<br>(BCDMOS) |      |          |          | 11.02.06 |          | 11.04.06        |            | 11.07.20 | 11.10.12 |          |

|                 | TowerJazz     | 0.18µm<br>(BCDMOS) |      |          |          | 11.03.02 |          | 11,05,06        | 11.08.29   | 11.09.14 | 11,11,15 |          |

|                 | 매그나칩/<br>하이닉스 | 0,35μm             | 20   | 10,12,05 |          | 11,03,02 | 11,03,15 | 11,05,06        | 11,08,29   | 11.09.14 | 11,12,20 | 12,01,20 |

|                 | 매그나칩/<br>하이닉스 | 0,18μm             |      |          |          | 11,03,02 |          | 11,05,06        | 11.08.29   | 11.09.14 | 11,12,20 |          |

|                 | 삼성            | 65nm               | 20   |          |          | 11.03.02 | 11.03.15 | 11.05.06        | 11.08.19   | 11.09.05 | 12.01.15 | 12.02.15 |

|                 | TowerJazz     | 0.18µm(CIS)        | 1    |          |          | 11.04.15 | 11.04.29 | 11.07.15        | 11.10.10   | 11.10.24 | 12.01.11 | -        |

|                 | 동부            | O.11μm             | 13   |          |          | 11.04.15 | 11,04,29 | 11,07,15        | 11,10,10   | 11,10,26 | 12,01,10 | 12,02,10 |

| 105회<br>(11-8)  | 동부            | 0.35µm<br>(BCDMOS) | 3    |          |          | 11.04.15 | 11,04,29 | 11,07,15        | 11,10,13   | 11,10,26 | 12,01,18 | 12,02,18 |

|                 | KEC           | 4µm                | 20   | 11.01.20 | 11.02.08 | 11.04.15 | 11,04,29 | 11,07,15        | 11,10,14   | 11,10,28 | 12,01,27 | 12,02,27 |

|                 | KEC           | 0.5µm              | 20   |          |          | 11,04,15 | 11.04.29 | 11,07,15        | 11,10,14   | 11,10,28 | 12,01,27 | 12,02,27 |

| 106회<br>(11-9)  | 삼성            | 0,13µm             |      |          |          | 11.05.15 |          | 11.08.15        |            | 11.11.25 | 12.03.09 |          |

| 107회<br>(11-10) | 매그나칩/<br>하이닉스 | 0.18µm             |      |          |          | 11.06.30 |          | 11.08.31        | 11.12.15   | 11.12.30 | 12.04.10 | 12.05.10 |

참여 대상 : IDEC Working Group(WG) 대학의 학부생 및 대학원성

Special Article

3-D NAND Flash Memory 개발 동향 (2)

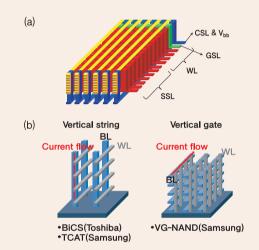

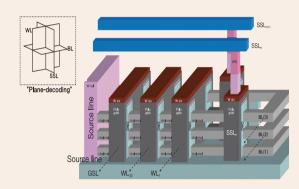

#### 서로

소자의 크기를 줄이지 않으면서 집적도를 향상시키기 위한 방법으로 최근 각광받는 방법은 3-D method이다. 이는 기존의 단순한 2차원의 1층 제조 방법에서 벗어나 수직 방향으로 동일한 소자를 다수 적층함으로서 소자 크기를 유지하면서 집적도를 크게 향상시킬 수 있다. 이것은 마치 1층 주택을 아파트로 대체하면서 용지 면적은 그대로 유지하면서 가구 수를 크게 늘리는 방법과 동일하다고 할 수 있다. 따라서 현재 세계 유수의 반도체제조 회사들은 이 3-D memory 개발에 중점을 두고 있으며 그중에서도 1개의 트랜지스터로 구성할 수 있는 Flash memory 개발에 주력하고 있다. 따라서 본 칼럼에서는 지난호에 이어서 TCAT, VG-NAND 개발 동향에 대해서 살펴보도록 하겠다.

## TCAT[1]

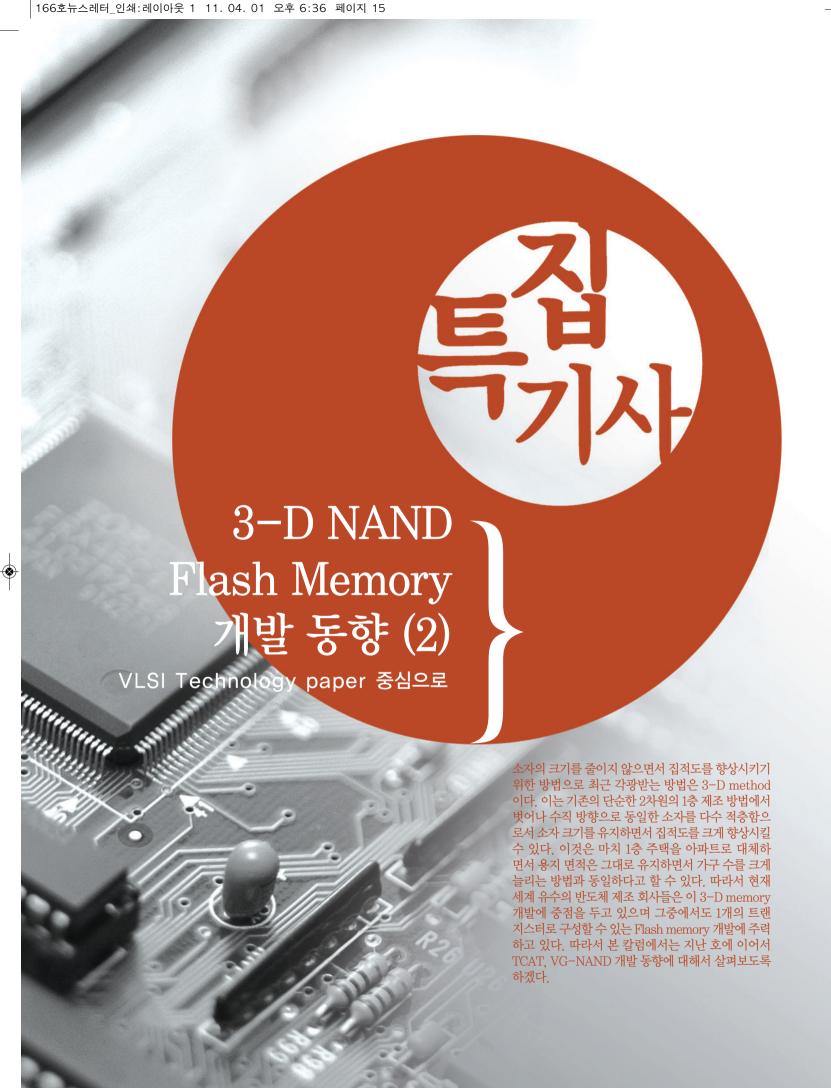

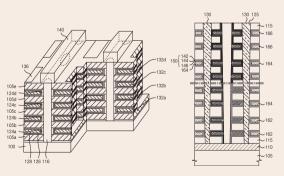

TCAT 구조는 삼성이 2009 Symposium on VLSI Technology 에서 발표한 구조로서 기본적으로는 BICS와 동일한 구조이나 BICS의 문제점인 폴리 실리콘 gate를 금속 gate로 대체해서 gate 동작 속도를 대폭적으로 향상시킨 구조이다.

그림 1. TCAT 설명 ((a) : 구조도, (b) gate 공정 설명도)

그림 1에서 보다시피 TCAT 구조의 핵심은 삼성이 'gate replacement'라고 부르는 금속 gate 형성 과정에 있다. 먼저 금속 gate가 들어갈 자리를 Nitride로 채워서 연속적으로 적층한다음 습식 식각 공정을 통해서 이 Nitride를 제거한다. 그 다음 CVD(chemical vapor deposition) 증착 공정을 통해서 텅스텐을 빈자리에 채워 넣은 다음 gate 간의 절연을 위해서 하단의연결된 부위를 건식 식각 공정을 통해서 절단해서 각각의 gate를 완성하게 된다.

초기 단계에서 금속 gate를 적층하지 않은 이유는 금속의 식각이 다른 물질에 비해서 매우 어렵기 때문이다. 하지만, 이 부분이 TCAT의 강점이자 약점이라고 할 수 있다. 분명히 금속 gate를 사용해서 gate의 동작 속도는 근본적으로 향상되지만 그만큼 공정이 복잡해지기 때문에 제조비용이 BICS보다 상승하고 습식 식각 공정에서 식각비와 식각시간의 중요성이 매우 높아지게된다. 이러한 식각 공정상의 산포를 최소화해야 양산단계로 이어질

수 있을 것이다. 그러나 BICS역시 기본적으로 높은 식각비를 필요로 하는 건식식각 공정이 핵심공정이므로 이 부분의 수율 획득이 양산으로 이어지기 위한 큰 과제 중 하나가 될 것이다.

그림 2. TCAT 구조의 단면도와 지우기 동작 설명도

BICS와 차별되는 TCAT의 두 번째 특징은 지우기 동작에 있다. BICS가 GIDL까지 사용해서 약간 무리하게 지우기 동작을 수행하는 것이 비해서 TCAT는 처음부터 substrate 영역을 p-type으로 도핑 하였기 때문에 일반적인 메모리 소자의 p-well 과 동일한 형태로 지우기 동작을 할 수 있으며 hole의 공급 또한 그림에서 보듯이 매우 원활하게 할 수 있다. 이러한 장점 때문에 현 시점에서 TCAT 구조는 기본 구조가 거의 완성단계에 있다고 할 수 있으며 2010 Symposium on VLSI Technology[2]에서도 구조 개선을 통한 기본 동작의 문제점 개선보다는 SSL트랜지스터의 길이 조정을 통한 누설 전류 감소와 전하 저장층의 구조 변경을 통한 저장 전하 간의 간섭을 줄이는 구조와 같은 세부적인 다듬기에 들어간 내용이 발표되었다.

현 시점에서 TCAT 구조는 BICS에서 발생하는 gate 저항과 지우기 동작 문제를 해결해서 매우 유용한 구조라고 할 수 있다. 하지만, TCAT 구조 또한 동일하게 폴리 실리콘을 사용한 수직 방향 채널 구조이기 때문에 적층 수 증가에 따른 채널 저항의 증가 문제가 존재한다. 고집적 적층구조로 대량 생산되기 위해 서는 TCAT의 이러한 문제점을 극복하거나 상쇄할 만한 대안이 제시되어야 할 것으로 여겨진다. TCAT 관련 특허는 삼성전자에서 이미 다양한 구조와 공정에 대해서 등록이 완료된 상황이다. 단 BICS와는 달리 저항 변화 메모리에 관한 청구항은 발견되지 않고 대신 청구항 자체에 다결정 실리콘이 아닌 단결정실리콘을 사용하는 것을 명시하고 있다.[3].[4]

그림 3. TCAT 관련 특허 도면들

IDEC | 특집기사

그림 3의 2개 도면은 각각 2007년 11월 8일, 2010년 1월 25일에 출원된 특허도면으로서 모두 단결정 실리콘을 채널로 사용하는 청구항이 개시돼 있다. 이렇게 실제 공정상 구현이 어려운 단결정 실리콘을 청구항으로 명시한 것으로 보면, 향후 공정 기술 발달에 따른 단결정 실리콘의 사용 가능성을 매우 크게 예상하고 있다고 생각된다.

## VG-NAND[5]

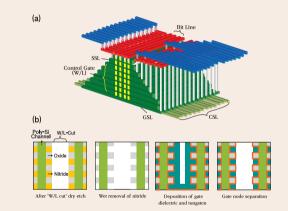

VG-NAND 구조는 삼성종합기술원에서 2009 Symposium on VLSI Technology에 발표한 구조로서 BICS 구조의 문제점을 개선한 동일 구조인 TCAT과는 달리 근본적으로 접근 방식을 달리한 구조이다.

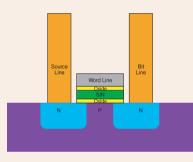

그림 4. VG-NAND 설명도((a) : 구조도, (b) 타 구조와의 차이점)

그림 4에서 보다시피 VG-NAND는 BICS, TCAT과는 달리 gate 구조가 수직이고 채널은 수평 방향으로 구성되어 있다. 이렇게 함으로써 BICS, TCAT의 근본적인 문제점인 적층수 증가에 따른 채널 저항 증가를 해결하였다.

VG-NAND 구조에서의 채널은 수평 방향으로 형성되어 있기 때문에 적층수가 증가해도 채널의 길이는 항상 일정하며 이는 이론적으로는 무한대의 적층수를 가지더라도 채널저항은 모든 적층단계에서 전부 일정하다는 계산이 나오게 된다. 여기에 수직 방향의 gate는 TCAT처럼 gate 치환 공정이 필요없이 gate 형성을 위한 식각 공정 이후 바로 금속 물질을 gate hole 상에 증착함으로써 고성능의 금속 gate를 형성할 수 있는 장점이

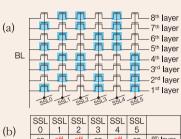

또한, 소자 구조 자체가 일반적인 Flash memory 소자를 2중으로 형성한 형태의 구조이기 때문에 내부의 물리적인 현상에 대한 이해가 쉽다는 장점이 있다. 이러한 장점이 있는 VG-NAND 구조이지만 역시 단점 또한 만만치 않다. 먼저 각 층의 선택을 위한 SSL 구조의 경우 BICS, TCAT과는 달리 계단식의 구조가 아닌 SSL 트랜지스터를 선택적으로 n-type 도핑을 함으로서 마치 2진수에 의한 번호를 부여하듯 각 층을 선택할 수 있는 encoder 회로형태를 구성해서 선택하게 된다.

|   | SSL | SSL | SSL | SSL | SSL | SSL |                       |

|---|-----|-----|-----|-----|-----|-----|-----------------------|

| ) | 0   | 1   | 2   | 3   | 4   | 5   |                       |

| ′ | on  | off | off | on  | off | on  | 8 <sup>th</sup> layer |

|   | off | on  | off | on  | off | on  | 7 <sup>th</sup> layer |

|   | on  | off | on  | off | off | on  | 6 <sup>th</sup> layer |

|   | off | on  | on  | off | off | on  | 5 <sup>th</sup> layer |

|   | on  | off | off | on  | on  | off | 4 <sup>th</sup> layer |

|   | off | on  | off | on  | on  | off | 3 <sup>rd</sup> layer |

|   | on  | off | on  | off | on  | off | 2 <sup>nd</sup> layer |

|   | off | on  | on  | off | on  | off | 1 <sup>st</sup> layer |

그림 5. VG-NAND 구조의 SSL 구성도(a: 등가 회로, b: 선택 방법)

그림 5는 VG-NAND의 SSL 구성을 보여주고 있다. 그림 (a)에서 짙은 색으로 칠해져 있는 부분이 n-type 도핑이 되어서 무조건 on 상태인 트랜지스터이며 그림 (b)는 각 층의 선택 방법을 나타내고 있다. 예를 들어서 3번째 층을 선택할 경우 SSL1, SSL3, SSL4 라인을 on 상태로 바꾼다.

이 경우 다른 층들은 전부 1개 혹은 2개의 SSL이 off 상태가 되어서 선택되지 않지만 3번째 층은 전부 on 상태가 되므로 선택이 돼서 전류가 흐르게 된다. 이러한 방법으로 SSL을 구성함으로써 BICS, TCAT이 계단 형식으로 측면을 구성하면서 생기는 문제 점인 적층 수 증가에 따라서 측면방향으로 필요 없는 공간이 계속 늘어나게 되는 점을 해결하였다.

분명히 이러한 SSL 구조는 공간 절약 측면에서는 매우 유리하지만 이렇게 SSL을 구성하기 위해서는 각층의 형성단계에서 SSL 구성을 위한 리소그래피 공정과 도핑 공정이 필요로 하게된다. 물론 이 리소그래피 공정과 도핑 공정은 앞서 말한 3-D stacking 방법에 비하면 매우 간소한 공정이지만 적층단계에서 리소그래피 공정을 전혀 사용하지 않는 BICS, TCAT구조에 비하면 분명히 약점이 된다고 할 수 있다. 따라서 이 구조의 효용성 여부는 실제 공정상 추가 비용이 이 구조를 적용함으로써 얻어지는 집적도 향상으로 상쇄될 수 있는지가 관건이될 것이다.

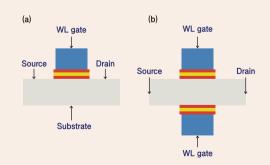

그림 6. 일반적인 Flash memory 소자와 VG-NAND 구조 비교 (a: Normal Flash memory, VG-NAND)

두 번째 문제점은 지우기 동작에 있다. 그림 6에서 볼 수 있듯이 VG-NAND의 구조는 분명히 구조상으로 보면 일반적인 NAND Flash memory 구조와 유사하지만 두 소자가 서로 등을 맞대고 있는 형태이기 때문에 Substrate 전압, 즉 접지 전압을 구조적으로 인가할 수 없는 단점이 있다. 이는 지우기 동작에서 접지 전압에 인가되는 높은 양의 전압이 source와 drain 라인에 인가되어서 지우기 동작을 할 수는 있지만, memory string이 길어질 경우 string line의 중간 정도에 위치한 소자는 소스나 drain과의거리가 너무 멀어서 전압이 제대로 인가되지 않고 이것 때문에지우기 동작이 제대로 수행되지 않을 가능성이 있다.

이러한 문제 때문인지 2010 Symposium on VLSI Technology 에서는 삼성에서 VG-NAND 구조에 대한 개선안을 발표하지 않았다. 대신 대만의 Macronix 사에서 VG-NAND 구조의 개선안을 발표하였다. [6]

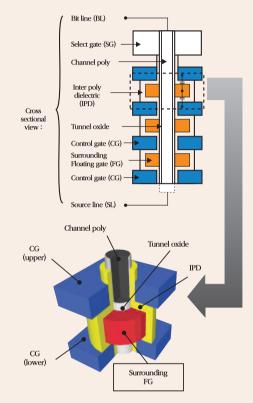

그림 7. Macronix사의 VG-NAND 구조도

그림 7에서 볼 수 있듯이 구조상으로는 삼성종합기술원의 VG-NAND 구조와 큰 차이를 보이지 않지만, SSL을 간략하게 하고 측면 방향의 계단형식으로 변경한 것을 알 수 있다. 이것은 Macronix사의 판단으로는 SSL 인코딩 방식을 적용함으로써 생기는 제조공정상의 리스크가 집적도 향상보다 더 큰 문제라고 판단한 것으로 풀이된다. 다른 차이점으로는 채널 구조를 기본적으로 n-type으로 도핑한 'buried-channel' 구조를 적용해서 폴리 실리콘 채널을 사용하면서 생기는 높은 채널 저항 문제를 원천적으로 해결한 점에 있다.

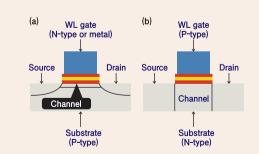

그림 8. 일반적인 소자의 채널과 buried-channel 구조에서의 채널 영역 (a: 일반 소자. b: buried-channel)

그림 8은 일반 채널을 적용한 소자와 buried-channel을 적용한 소자와의 차이를 설명한 것이다. 가장 큰 특징은 Substrate, 즉 well 영역의 도핑 타입으로서 일반적으로는 P-type으로 도핑하고 채널 형성은 gate 전압에 의한 전자들의 집중으로 형성된 반전층을 통해서 전류가 흐르게 된다. 하지만, 이 경우전체 substrate 영역에서 전류가 흐르는 영역은 단지 gate 부근의 매우 작은 영역뿐이기 때문에 저항이 커지게 된다. 특히 이러한 문제는 기본적으로 채널 저항이 높은 폴리 실리콘을 사용할 경우 더욱 증가하게 된다.

buried-channel은 이와 반대로 substrate 영역을 n-type 으로 도핑함으로서 채널 저항을 근본적으로 줄이는 구조이다. 물론 이 경우 기본적으로 반전층 직전의 공핍층이 substrate 영역 전체가 되기 때문에 전류는 항상 흐르게 되며 문턱 전압도음의 값을 가지게 된다. 일반적인 논리 소자의 경우 이런 형태의 사용이 불가능하지만 Flash memory는 문턱 전압을 쓰기 동작을 통해서 인위적으로 조정할 수 있기 때문에 충분히 양의 값까지 문턱 전압을 조절해서 사용할 수 있다. 이럴 경우 지금까지 설명한 구조의 공통적인 문제점인 높은 채널 저항을 단번에 해결할수 있는 것이다.

그림 9. 'Φ' gate 구조

그림 9는 실제 제작된 소자의 단면을 전자현미경으로 촬영한 사진으로서 보다시피 gate 층이 폴리실리콘 채널을 약간 감싸고 있는 형태인 것을 알 수 있다. 이렇게 함으로써 삼성의 VG-NAND 구조와 비교하면 소자 특성을 좀 더 향상시킨 것을 발표하였다. 하지만, 이 구조 역시 완전한 surround gate 구조인 BICS, TCAT에 비해서는 gate 제어 능력이 떨어질 것이며 이를 보완하기 위한 추가적인 도핑공정이 요구되지만, 기존 메모리 소자에서는 비교적 자유로운 수직 방향의 도핑이 VG-NAND에서는 채널 자체가 적층되기 때문에 구조적으로 매우 불가능한 단점을 가지고 있다.

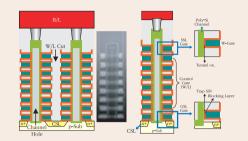

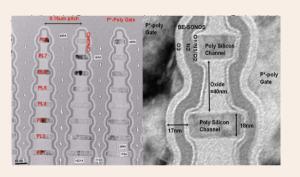

## SONOS(Silicon-Oxide-Nitride-Oxide-Silicon) 구조의 문제점과 플로팅 게이트 구조

현재까지 개발 중인 3-D NAND Flash memory의 대부분은 전하 저장구조로서 SONOS 구조를 사용하고 있다. 이 구조는 3-D 구조 개발 이전에 기존의 2-D 구조에서도 적용되는 것이 유력시된 구조로서 원래는 단순히 Gate 절연막 층의 효율성을 높이기 위해서 기존의 실리콘 산화물(SiO<sub>2</sub>)층 중간에 에너지

IDEC | 특집기사

배리어 대역이 좀 더 낮은 실리콘 질화물(Si<sub>3</sub>N<sub>4</sub>)층을 삽입함 으로써 트랜지스터 동작 속도를 좀 더 빠르게 할 수 있는 것으로 알려졌었다. 하지만, 이 실리콘 질화물층에 충분한 양의 Charge trap이 존재할 경우 전자를 포획하는 것이 가능함으로써 이 구조 자체로도 전하 저장층 기능을 할 수 있다는 것이 알려졌다. [7]

Floating Gate

SONOS

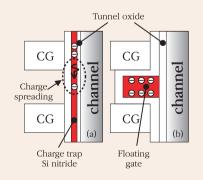

그림 10. 플로팅 게이트 구조와 SONOS 비교도

그림 10은 현재 사용 중인 플로팅 게이트 구조와 연구 중인 SONOS 구조를 비교한 것으로서 그림에서는 구조를 제대로 표시하기 위해서 Oxide-Nitride-Oxide 구조가 두껍게 묘사 되어 있지만 실제로는 플로팅 게이트의 하단부의 빈 공간만큼의 두께에도 충분히 구현할 수 있다.

이는 기본적으로 절연체인 실리콘 질화물의 trap에 의한 전자 포획 능력 때문이며 또한 이 절연체라는 특성 때문에 도전체인 플로팅 게이트가 cell마다 전부 단절되어 있어야 하는 것과는 달리 전부 연결되어 있더라도 저장된 전하의 분산이 없을 것 으로 기대되어졌다.

이러한 장점 때문에 구조적으로 복잡해지고 많은 제조 공정이 요구되는 3-D 구조에서 최적의 구조로 예상되고 있었다. 하지만. 최근의 연구 동향을 살펴보면 실제로는 실리콘 질화물층을 사용 하더라도 플래쉬 메모리 구조의 높은 쓰기 전압과 지우기 전압 때문에 저장된 전자의 이동이 많이 이루어질 수 있다고 알려 졌다. [2],[8] 더불어 기본적으로 전기가 통하지 않는 것을 전제 로 하는 절연체 층의 Trap들에 전자를 저장하는 것 때문에 저장 된 전자를 유지하는 시간(retention time)이 플로팅 게이트 구조 와 비교하면 떨어지는 문제점이 대두되고 있다.

이렇게 발견되는 많은 문제점으로 말미암아서 과연 SONOS 구조가 새로운 플래쉬 메모리 구조로서 적합한 것인가에 대한 회의론이 제기되고 있으며 이러한 경향의 한 줄기로서 기존의 플로팅 게이트 구조를 다시 3-D 구조에 적용하려는 연구가 발견되고 있다. [8]

그림 11. 하이닉스가 발표한 3차원 플로팅 게이트 플래쉬 메모리 구조

그림 11는 2010년에 하이닉스에서 IDEM(International Electron Devices Meeting)에 발표한 3차원 플로팅 게이트 플래쉬 메모리 [8]의 구조도이다. 플로팅 게이트를 두 개의 컨트롤 게이트 사이에 위치시킴으로써 게이트의 제어 능력을 극대화 시켰으며 이를 통해서 각 플로팅 게이트 간의 간섭을 상당 부분 줄일 수 있도록 설계된 것이 특징이다.

그림 12. SONOS 구조와 하이닉스 구조의 비교

특히 기존 SONOS 구조에서 문제가 되었던 저장된 전자의 분산 문제를 Cell마다 단절되어 있는 플로팅 게이트 구조를 적용함 으로써 원천적으로 해결한 것은 매우 유효한 구조라고 예상된다. 여기에 전하 저장을 위해서는 도전체라는 특성상 일정 두께가 요구되는 플로팅 게이트를 컨트롤 게이트 사이에 위치시킴으 로써 SONOS 구조에 비교할 경우 대두될 수 있는 집적도 문제 를 해결하려는 구조로 되어 있다. 따라서 이 구조가 실제 양산 단계까지 진행될 경우 기존 SONOS 구조에 대한 강력한 대항마가 될 수 있을 것이다.

지금까지 2부에 걸쳐서 2010년도까지의 3-D NAND Flash memory 개발 동향에 대해서 알아보았다. 현 시점에서는 도시바 의 P-BICS, 삼성의 TCAT, Macronix사의 VG-NAND 구조가 가장 활발하게 진행되고 있다고 할 수 있다. 또한, 여기에 SONOS 구조의 문제점에 대한 대안으로서 3-D 구조에 최적 화된 플로팅 게이트 구조가 하이닉스에서 발표되어서 연구가 진행되고 있다.

하지만, 모든 소자에서 아직은 양산단계로 진행하기에는 많은 문제점을 가지고 있기 때문에 이를 보완하기 위한 연구가 앞으로 활발히 이루어질 것이다. 또한, 위 구조들뿐만 아니라 BICS에 적용되는 ReRAM 구조와 같이 현재 연구 중인 차세대 저항 변화 메모리의 3차원 구조 또한 예상할 수 있으며 더 나아가서 전혀 새로운 구조와 동작 방식의 메모리 구조의 출현 또한 충분히 가능한 시나리오가 될 것이다.

## Reference

- [1] Jaehoon Jang et al, 2009 Symposium on VLSI Technology Digest of Technical Papers, PP 192-193

- [2] Won-seok Cho et al, 2010 Symposium on VLSI Technology Digest of Technical Papers, PP 173-174

- [3] 국내출원번호 : 10-2007-0113535 "수직형 반도체 소자 및 그 제조 방법" 삼성전자

- [4] 국내출원번호 : 10-2010-0006475 "수직 구조의 비휘발성 메모리 소자" 삼성전자

- [5] Wonjoo Kim et al, 2009 Symposium on VLSI Technology Digest of Technical Papers, PP 188-189

- [6] Hang-Ting Lue et al, 2010 Symposium on VLSI Technology Digest of Technical Papers, PP 131-132

- [7] J. Bu and M. H. White, Solid State Electronics 45, 113 (2001).

- [8] SungJin Whang et al, 2010 International Electron Devices Meeting, PP 668-671

## 한양대학교 융합전자공학부

이승백 교수 연구분야: CNT소자, MEMS, 3D CTF(Charge Trap

Flash), MRAM등

E-mail: sbl22@hanyang.ac.kr http://ndl.hanyang.ac.kr

#### 한양대학교 전자컴퓨터통신공학과

최선준 연구분야: 3D CFT

E-mail: msz009@hanyang.ac.kr

http://ndl.hanyang.ac.kr