## (A)아이앤씨테크놀로지 산학장학생 모집으강

㈜이이앤씨테크놀로지는 모바일 TV용 SoC, NFC, WiFi, LTE 등 을 사업영역으로 하는 코스닥상장 팹리스업체입니다. 국내 지상파 DMB 분야의 시장 점유율 80%이상을 차지하고 있으며, 국내 유수의 휴대폰, 자동차, 네비게이션, PMP, 각종 이동형 기기에 아이앤씨테크놀로지의 제품이 사용되고 있습니다.

- 1. 지원서 접수 2. 서류전형 3. 면접실시(서류합격자) 4. 기본 신체검사 5. 선발 및 장학금지급

- □ 지원자격

- 1. 반도체, 전자, 전기, 전산, 제어, 컴퓨터 관련학과 3~4학년 학부 재학생, 석/박사 재학생

- 2. 학부 재학생: 평균학점 4.5만점 기준 3.2 이상

- 3. 석/박사 재학생 : 평균학점 4.5만점 기준 3.5 이상

### 💶 지원내역

- 1. 산학장학금 지급

- 학부 재학생: 등록금 전액

- 석/박사 재학생: 등록금 등 개인별 장학금 책정

- 2. 학점: 학부 재학생 3.2, 석/박사 재학생 3.5이상 유지 의무

- 3. 장학생 과정 중 인턴쉽 기회 부여

- 4. 졸업 후 당사 입사 조건

### 📧 지원방법

- 1. 지원시기 : 상시모집

- 2. 문의: 경영지원본부 인사담당자 (02-2142-3322) hr@inctech.co.kr

### **In-Design Physical Verification** with IC Validator and IC Compiler

- 100 Tapeouts 1 Year After Introduction

- Standardized at Top Semiconductor Manufacturers

- Proven to Accelerate Time to Tapeout

A New World for Physical Verification

IDEC Newsletter | 통권:제170호 발행일 | 2011년 7월 30일 발행인 | 경종민 편집인 | 김이섭 제 작 | 푸울디자인 기획|전항기 전화|042) 350-8535~6 팩스|042) 350-8540 http://idec.or.kr E-mail | jhg0929@idec.or.kr 발행처 | 반도체설계교육센터(IDEC)

Vol.170

IDEC NEWS | 02 매니코어 Lifetime 신뢰성 연구 동향 | 04 A/D 변환기 기술동향 | 08 반도체 기반테라헤르츠 이미징 기술 연구 동향 | 12 미래의 지능형 SoC 시대를 대비하다 | 16

반도체설계교육센터 사업은 지식경제부, 반도체산업협회, 반도체회사(삼성전자, 하이닉스반도체, 매그나칩반도체, 동부하이텍, 앰코테크놀로지코리아, KEC, 세미텍, TowerJazz)의 지원으로 수행되고 있습니다.

### 매니코어 Lifetime 신뢰성 연구동향

공정이 발달하면서 하나의 칩에 여러 개의 코어를 집적하는 멀티코어가 마이크로프로세서의 일반적인 구조로 자리 잡고 있다. 멀티코어 구조는 전통적인 싱글코어에서 프로세서의 동작 주파수를 지속적으로 증가시키면서 심화하여온 전력 소모 및 발열 문제에 대한 솔루션이 되고 있다. 본 고에서는 매니코어 Lifetime 신뢰성 연구동향에 대해 소개하고자 한다. (관련기사 P04~06참조)

### A/D 변환기 기술동향

반도체 공정기술의 발달로 회로의 집적도가 증가함에 따라 복잡하고 다양한 기능을 갖는 디지털 신호처리 회로의 구현이 가능해졌으며, 저전력 동작 특성 및 재설계의 용 이함 등으로 말미암아 다양한 시스템이 디지털 신호처리 회로를 이용하여 구현되고 있다. 그러나 아날로그로 이루어진 자연계의 원 신호를 디지털 신호로 변환시켜주기 위해서는 아날로그 전기 신호를 디지털 신호로 변환해 주는 A/D 변환기가 시스템 구성에 반드시 필요하며, 제품의 성능을 결정하는 매우 중요한 역할을 하고 있다. 본 고에서는 A/D 변환기의 성능 동향에 대해 다루고자 한다. (관련기사 P08~11참조)

### 반도체 기반 테라헤르츠 이미징 기술 연구동향

테라헤르츠 파는 플라스틱, 종이, 옷 등과 같은 다양한 포장성 물질에 대해 투과성이 우수한 반면 수분을 포함한 물질에 대해서는 투과성이 크게 떨어지는 경향이 있어 다른 주파수 대역과는 대별되는 고유한 특성을 지니고 있다. 따라서 이러한 특성을 적절히 활용하는 경우 타 이미징 기술과는 다른 측면에서의 응용 가능성을 보일 수 있다. 본 고에서는 이러한 테라헤르츠 이미징 기술에 대한 개요와 함께 그중에서도 반도체 전자소자에 기반을 둔 연구의 최근 동향을 <u>살펴보기로 하겠다.</u> (관련기사 P12~15 참조)

### 미래의 지능형 SoC 시대를 대비하다.

지능형 차량용 SoC 플랫폼 센터는 한양대학교 에리카캠퍼스에 지식경제부, 정보통신산업진흥원, 반도체설계교육센터의 지원으로 2011년 6월 설립됐다. 미래에 고성장이 예상되는 지능형 SoC 산업을 이끌어 갈 우수 전문 인력을 양성하고, 플랫폼을 구축 보급하고, 산학연의 network를 형성하여, 다양한 정보 교류 및 협력의 중심이 될 것 입니다. 본 고에서는 한양대지능형 차량용 SoC 플랫폼 센터의 소개 및 포부를 신현철 CEO를 통해 들어보고자 한다. (관련기사 P16~P18)

# August | 2011

|                 |                   | IVIF VV (IV               | Iuiti    | FI       | oject war                                                                          | <del>2</del> 1) |                |                 |

|-----------------|-------------------|---------------------------|----------|----------|------------------------------------------------------------------------------------|-----------------|----------------|-----------------|

| 신청              | 현황                | 1                         |          |          |                                                                                    |                 |                |                 |

| 구분              | 공정                | 제작가능면적<br>(mm2 x 칩수)      | 신청<br>팀수 | 채택<br>팀수 | 설계면적<br>(mm2 x 칩수)                                                                 | DB<br>마감        | Die<br>-out    | 비고              |

| 103회<br>(11-06) | TJ<br>CIS<br>0.18 | 5x5mm² x 1                | 5        | 4        | 25x25mm² x 4                                                                       | 2011.<br>6.21   | 2011.<br>9.21  |                 |

|                 | TJ<br>BCD<br>0.18 | 5x5mm <sup>2</sup> x 1    | 1        | 1        | 5x5mm <sup>2</sup> x 1                                                             | 2011.<br>8.29   | 2011.<br>11.15 |                 |

| 104회            | M/H<br>0,35       | 5x4mm² x 20               | 20       | 20       | 5x4mm² x 20                                                                        | 2011.<br>8,29   | 2011.<br>12,20 |                 |

| (11–07)         | M/H<br>0.18       | 4.5x4mm <sup>2</sup> x 20 |          | 20       | 4.5x4mm² x 20                                                                      | 2011.<br>8.29   | 2011.<br>12.20 |                 |

|                 | 삼성<br>65n         | 20개 서버<br>(4x4mm² x 48)   | 23       | 23       | 4x4mm² x 23                                                                        | 2011.<br>8.19   | 2012.<br>1.15  |                 |

|                 | TJ<br>0.18<br>CIS | 5x5mm <sup>2</sup> x 2    | 6        | 5        | 5x2,5mm <sup>2</sup> x 3<br>2,5x2,5mm <sup>2</sup> x 2                             |                 | 2012.<br>1.11  |                 |

| 105회<br>(11-08) | 동부<br>0.35<br>BCD | 5x5mm² x 3                | 12       | 5        | 5x5mm <sup>2</sup> x 1<br>5x2,5mm <sup>2</sup> x 4                                 | 2011.<br>10.13  | 2012.<br>1.18  |                 |

|                 | 동부<br>0.11        | 5x5mm² x 13               | 30       | 30       | 5x2.5mm <sup>2</sup> x 22<br>2.5x2.5mm <sup>2</sup> x 8                            |                 | 2012.<br>1.10  |                 |

| 106회<br>(11-09) | 삼성<br>0.13        | 4x4mm² x 48               | 32       | 32       | 4x4mm <sup>2</sup> x 31<br>8x4mm <sup>2</sup> x 1                                  | 2011<br>11.5    | 2012<br>3.9    | 후기모집<br>8.15~   |

| 107회<br>(11-10) | M/H<br>0.18       | 4.5x4mm² x 20             | 25       | 25       | 4.5x4mm <sup>2</sup> x 16<br>4.5x2mm <sup>2</sup> x 6<br>2.25x2mm <sup>2</sup> x 3 | 2011<br>12.15   |                | 설계설명<br>회: 7.28 |

| 71717           | La                | ਨੀ. ।                     |          |          |                                                                                    |                 |                |                 |

MPW (Multi-Project Wafer)

### |칩제작 현황 |

| 구분                                             | 공정                   | 제작가능면적<br>(mm2 x 칩수)                                              | 제작<br>칩수                        | 제작면적<br>(mm2 x 칩수)                                                                | Die-out<br>예정일        | 현재<br>상태         | 비고                |

|------------------------------------------------|----------------------|-------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------|-----------------------|------------------|-------------------|

| TIIOO ƏI                                       | TJ<br>SiGe<br>0.18   | 5x5mm² x 1                                                        | 3                               | 5x2,5mm <sup>2</sup> x 1<br>2,5x2,5mm <sup>2</sup> x 2                            | 2011.<br>5.24         | 제작<br>완료         |                   |

| 제98회<br>(11-01)                                | M/H<br>0.35<br>M/H   | 5x4mm <sup>2</sup> x 20                                           | 19                              | 5x4mm² x 19                                                                       | 2011.<br>6.7<br>2011. | PKG<br>제작중<br>배포 | - PKG<br>: 8.8 예정 |

|                                                | 0.18                 | 4.5x4mm <sup>2</sup> x 20                                         | 20                              | 4.5x4mm <sup>2</sup> x 20                                                         | 5.11                  | 완료               |                   |

|                                                | TJ RF<br>0.18<br>동부  | 5x5mm <sup>2</sup> x 2                                            | 5                               | 5x5mm <sup>2</sup> x 1<br>2,5x2,5mm <sup>2</sup> x 4                              | 2011<br>5.11          | 배포<br>완료         |                   |

| 제99회<br>(11-02)                                | BCD<br>0.35          | 5x5mm² x 3                                                        | 6                               | 5x2,5mm² x 6                                                                      | 2011.<br>6.1          | 제작<br>완료         |                   |

|                                                | 동부<br>0.13           | 5x5mm² x 23                                                       | 30                              | 5x5mm <sup>2</sup> x 18<br>5x2,5mm <sup>2</sup> x 8<br>2,5x2,5mm <sup>2</sup> x 4 | 2011.<br>7.6          | 제작<br>완료         |                   |

| 제100회                                          | 동부<br>BCD<br>0.35    | 5x5mm <sup>2</sup> x 3                                            | 6                               | 5x2.5mm <sup>2</sup> x 6                                                          | 2011.<br>7.12         | 제작<br>완료         |                   |

| (11–03)                                        | 산성<br>0.13           | 4x4mm² x 48                                                       | 37                              | 4x4mm² x 35<br>4x8mm² x 2                                                         | 2011<br>8.25          | 칩제<br>작중         |                   |

| 제101회                                          | TJ RF<br>0.18        | 5x5mm <sup>2</sup> x 2                                            | 8                               | 25x2,5mm² x 8                                                                     | 2011<br>7.19          | 칩제<br>작중         |                   |

| (11–04)                                        | 0.18                 | 4.5x4mm <sup>2</sup> x 20                                         | 20                              | 4.5x4mm <sup>2</sup> x 20                                                         | 2011<br>9.5           | 칩제<br>작중         |                   |

| 제102회<br>(11-05)                               | 동부<br>BCD<br>0.35    | 5x5mm² x 3                                                        | 5                               | 5x2,5mm <sup>2</sup> x 6                                                          | 2011<br>8,31          | 칩제<br>작중         |                   |

| 제103회<br>(11-06)                               |                      | 5x5mm² x 3                                                        | 5                               | 5x5mm <sup>2</sup> x 1<br>5x2,5mm <sup>2</sup> x 4                                | 2011<br>10,12         | 칩제<br>작중         |                   |

| * M/H = I<br>* 우선/정규<br>* Die-out<br>* 2011년 N | 7모집에<br>일정은<br>MPW 참 | /하이닉스, TJ = Tow<br>서 마감될 경우 후기도<br>Diechip 제작완료 기<br>여 일정 및 방법은 홈 | /erJaz<br>!집은 7<br>준임, F<br>페이지 | z<br>진행되지 않음.<br>Package는 Die-out후<br>(www.idec.or.kr) 참조                         | 3주 이상 소!              | 요됨.              |                   |

\* 위의 내용은 7/28 기준임. \* 문의 : 이의숙(042-350-4428, yslee@idec.or.kr)

### 제5회 동부IP설계공모전 모집 마감

- 모집마감: 2011, 7, 24(일)

- 지원공정

| 공정                         | 제작칩수 | Chip size     | Package 지원  |

|----------------------------|------|---------------|-------------|

| 0.11um Mixed-Signal/RF     | 40   | 2,35mmx2,35mm | 80 pin LQFP |

| 0.35um High Voltage(BD350) | 16   | 2,35mmx2,35mm | 80 pin LQFP |

### ■ IP 찬여 혀화

| - " = " 100      |                                               |      |                |  |  |  |

|------------------|-----------------------------------------------|------|----------------|--|--|--|

| Biz              | IP List                                       | 참여팀수 | Target Process |  |  |  |

| A discovered     | Low Jitter PLL                                | 4    |                |  |  |  |

| Mixed<br>Foundry | 8 to 1 10-bit SAR ADC                         | 1    | 0.11µm MS      |  |  |  |

| 1 Ouriury        | LDO                                           | 9    |                |  |  |  |

| Analog           | Output Power Stage IP for Digital Amp.        | 1    | 0.35µm BCD     |  |  |  |

| Foundry          | Charge Pump Regulator for LED Driver          | 5    | (5060BD35)     |  |  |  |

| Display          | Spread Spectrum Clock Generator               | 2    | 0.11µm MS      |  |  |  |

| Display          | 3Gbps High Speed Transceiver                  | 2    | 0.11μ111 1010  |  |  |  |

|                  | Wide band LNA for Ultra sound System          | 2    | 0.11µm MS      |  |  |  |

|                  | 50~450MHz Low Jitter Fractional-N PLL         | 2    | 0.11µm MS      |  |  |  |

| APDC             | Fractional-N PLL Sigma-Delta ADC for TV tuner | 3    | 0.11µm MS      |  |  |  |

|                  | RF Power Amp for Mobile communication         | 4    | 0.11µm MS      |  |  |  |

|                  | NTSC/PAL (Analog TV)용 DAC/ADC                 | 3    | 0.11µm MS      |  |  |  |

|                  | 합계                                            | 38   |                |  |  |  |

### ■ 공모전 진행 일정

| 진행 내용          | 0.35µ m              | 0.11µm       |

|----------------|----------------------|--------------|

| 제안서 평가 결과 발표   | 2011.                | 8. 10        |

| DB 접수(IDEC) 마감 | 2011. 11. 16         | 2011. 12. 22 |

| Fab out        | 2012. 2. 29          | 2012. 5. 3   |

| 논문 접수 마감       | 2012.                | 6. 30        |

| 발표평가 및 시상식     | 2012.                | 7월 중순        |

| л П A] *       | 회 하 사 (0.40 250 4400 | 1 @'1 1)     |

### \* 문의 : 이의숙(042-350-4428, yslee@idec.or.kr)

### 채용 안내

● KAIST 반도체설계교육센터(IDEC)를 이끌어 갈 젊음과 열정을 가진 인재를 찾습니다.

### 1. 모집 분야

- 모집인원 : 연구직 (신입 · 경력), 0명

- 자격조건 : 대졸 이상, 반도체설계 관련 전공자, 영어 능통자 우대,

- 주요업무: 국·내외 Fab을 통한 칩 설계, 제작 지원

- Digital, Analog 칩 TEST기술 지원 EDA tool 교육 및 기술 지원

- 당사 입사지원서(홈페이지에서 다운로드)

- 최종학교 성적증명서 1부 / 졸업(예정) 증명서 1부

### 3. 접수 기간 및 접수처

- 접수기간 : 2011년 8월 31일(수)

- 접 수 처 : (305-701) 대전광역시 유성구 구성동 373-1 한국과학기술원

- 반도체설계교육센터 104호

- 접수방법 : 우편접수, 이메일 접수

- •문의처: 042-350-4045, shchoi@idec.kaist.ac.kr

- 홈페이지: www idec or kr

### 4. 기타

- 기타 자세한 사항은 홈페이지(www.idec.or.kr) 참조

- 접수된 서류는 인비 처리하며 반환하지 않음.

### 2011년 8월 교육 프로그램 안내

수강을 원하는 분은 IDEC홈페이지(www.idec.kaist.ac.kr)를 방문하여 신청하시기 바랍니다.

### 본 센터 강좌 일정 |

| 강의 일자     | 강의 제목                           | 분 류    |

|-----------|---------------------------------|--------|

| 8월 10-12일 | AMS Designer Simulator Training | Tool강좌 |

| 8월 16-18일 | Power Management IC 설계 및 응용     | 설계강좌   |

| 8월 30-31일 | NC-Simulator                    | Tool강좌 |

- 강좌일: 8월 10일-12일

- 강좌 제목: AMS Designer Simulator Training

- 강사: 이상철 차장(Cadence Korea)

### [ 강좌개요 ]

본 강좌는 Analog-Mixed Signal Circuit Simulator Tool인 AMS Designer 사용방법에 대하여 교육 예정입니다.

### [ 수강대상 ]

· Analog-Mixed Signal Circuit Engineer

### [ 강의수준 ]

[ 강의형태 ]

· 고급과정

· 이론 + 실습

### [ 사전지식, 선수과목 ]

- · 사전지식: Analog/Digital Design simulation

- ·경험 필수 선수과목: Verilog Language/NC-Verilog Simulator /Spectre Simulator/Analog Design Environment/Schematic Editor

- 강좌일: 8월 16-18일

- 강좌 제목: Power Management IC 설계 및 응용

- 강사: 구용서 교수(단국대) / 노정진 교수(한양대) / 최문호 박사 (페어차일드 코리아)

### [ 강좌개요 ]

Power management IC 의 기본 이론 및 동작원리를 학습한다. 이 를 바탕으로 Buck, Boost 변환기를 학습하고, ESD 등 PMIC 신뢰성 관련 사항 등을 학습한다. 기본 사항을 바탕으로 PMIC 의 응용분야로 써 LED backlight 구동용 회로의 개발에 대해 강의한다. 실습을 통해 이론을 실제 설계와 연계시켜 학습할 예정입니다.

### [ 수강대상 ]

· 관련 분야 대학원생 및 엔지니어

[ 강의수준 ]

[ 강의형태 ]

[ 사전지식, 선수과목 ]

· 전자회로

· 이론 + 실습

■ 강좌일: 8월 30-31일

■ 강좌 제목: NC-Simulator ■ 강사: 김일중 부장(Cadence Korea)

### [ 강좌개요 ]

- · 교육목표: Cadence IUS simulator를 이용해서 Verilog simulation을 수행하고 debugging을 자유롭게 할 수 있도록 하고자 합니다.

- · 강의 개요: Cadence NC-verilog tool을 사용한 verilog simulation 전체 flow에 대한 설명 및 Lab을 진행할 예정입니다.

### [ 수강대상 ]

· Analog-Mixed Signal Circuit Engineer

[ 강의수준 ]

[ 강의형태 ]

[ 사전지식, 선수과목 ]

· 중급

· 이론 + 실습

· Verilog Language

\* 문의 : 서소현 (042-350-8534, seosh@idec.or.kr)

### Chip Design Contest (CDC)

- International SoC Design Conference(ISOCC) 2011 Chip Design Contest 개최

- \*\* Chip Design Contest(CDC)는 ISOCC 2011 프로그램의 한세션으로 진행되나 제출한 paper는 프로시딩(Proceedings)에는 포함되지 않음.

- 1. 일정 및 장소

- 가. 전체 진행 일정 : 2011년 11월 17일(목)

- 나. 장 소 : 제주 라마다호텔

- 다. CDC 주요 일정

|   | 논문 제출 마감    | 논문 채택 통보    | Chip Design Contest |

|---|-------------|-------------|---------------------|

| Ξ | 2011. 8. 21 | 2011. 10. 1 | 2011. 11. 17        |

- \* 일정은 사정에 따라 다소 변경될 수 있습니다.

- 2. 논문 접수 분야: ASIC, FPGA(Altera, Xilinx)

### 3. 시상내역

|             | 시         | 내역             |                |

|-------------|-----------|----------------|----------------|

|             | 일반        | 최우수상(1팀)       | 상장 및 상금 100만원  |

| Best Design | 부문        | 우수상(2팀)        | 각 상장 및 상금 50만원 |

| Award       | 특별상<br>부문 | SSCS 서울챕터상(1팀) | 상장 및 상금 100만원  |

|      | 최우수상(1팀)                     | 상장 및 상금 50만원   |  |

|------|------------------------------|----------------|--|

| FPGA | 우수상(1팀)                      | 각 상장 및 상금 30만원 |  |

|      | * 참여팀 수에 따라 시상팀 수는 조정될 수 있음. |                |  |

### 제19회 학술반도체학술대회 Chip Design Contest 개최

- 1. 일정 및 장소

- 가. 전체 진행 일정 : 2012년 2월 16일(목)

- 나. 장 소 : 고려대학교내

- 다. CDC 주요 일정

| 논문 제출 마감    | 논문 채택 통보     | Chip Design Contest |

|-------------|--------------|---------------------|

| 2011. 11. 1 | 2011. 12. 20 | 2012, 2, 16         |

- \* 일정은 사정에 따라 다소 변경될 수 있습니다.

- 2. 논문 접수 분야: ASIC, FPGA(Altera, Xilinx)

- 3. 시상내역: ISOCC CDC와 동일함.

\* 문의 : 이의숙(042-350-4428, yslee@idec.or.kr)

### 매니코어 Lifetime 신뢰성 연구동향

연세대학교 전기전자공학과

강성호 교수

연구분야: SOC설계, SOC테스트 E-mail: shkang@yonsei.ac.kr http://soc.vonsei.ac.kr

연세대학교 전기전자공학과

홍혜정 박사 과정

연구분야: reliable multiprocessors, low-power design E-mail: hjhong@soc.yonsei.ac.kr

http://soc.vonsei.ac.kr

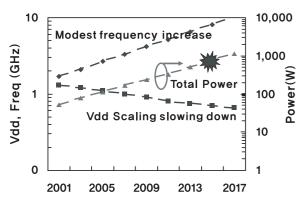

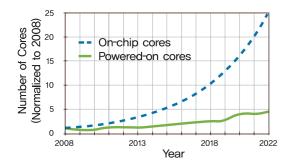

공정이 발달하면서 하나의 칩에 여러 개의 코어를 집적하는 멀티 코어가 마이크로프로세서의 일반적인 구조로 자리 잡고 있다. 멀티코어 구조는 전통적인 싱글코어에서 프로세서의 동작 주파수를 지속적으로 증가시키면서 심화하여온 전력 소모 및 발열 문제에 대한 솔루션이 되고 있다. 그러나 지금과 같은 추세로 멀티코어의 processing power가 발달할 것임을 가정하고 예측하였을 때, 2015년에는 300mm² 크기의 멀티코어에서 1,000W의 전력이 소모될 것이라고 한다 (그림 1). 이는 실제 구현이 불가능한 수치로써 증가하는 멀티코어의 전력 소모에 대비하는 새로운 솔루션의 필요하다.

그림 1. 멀티코어의 동작 주파수와 전력 소모 예측 [1]

Out-of-order execution, branch prediction과 같은 복잡한 기능을 제외하여 멀티코어 상의 코어보다 훨씬 단순한 형태의 코어를 만들고, 멀티코어에 집적하는 것에 비해 훨씬 많은 숫자의 코어를 하나의 칩에 집적하는 구조를 매니코어(manycore)라고한다. 멀티코어가 싱글코어 대비 성능은 향상하면서 전력 소모 및 발열 문제를 해결하였던 것처럼, 매니코어는 멀티코어보다 더 적은 전력을 소모하면서도 병렬성을 극대화하여 보다 좋은 성능을 낼 것으로 받아들여지고 있다. 본래 그래픽 처리를 위한 특수 프로세서인 graphics processing unit (GPU)는 최근 general-purpose로의 활용성이 높게 평가되어 다양한 분야에서 활발히 연구되고 있는데, 이 GPU가 매니코어 구조의 대표적인 예이다.

한편으로 공정 미세화가 급격히 진행되면서 디바이스의 wearout 이 심화하여 칩의 aging이 심각한 신뢰성 문제로 떠오르고 있다.

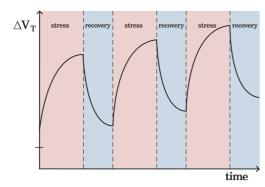

현재 칩의 lifetime을 감소시키는 가장 주된 원인으로 알려진 것은 negative bias temperature instability(NBTI)에 의한 효과이다 [2]. Bias temperature instability (BTI)란 트랜지스터에 바이어 스가 걸리는 동안 시간이 흐르면서 점차 트랜지스터의 특성이 변화되는 현상을 말한다. 이 현상은 회로 온도와 동작전압이 높을수록 촉진된다. BTI는 NMOS에서 발생하는 PBTI, BMOS에서 발생하는 NBTI, 이렇게 두 가지 형태로 나타나는데, 이 중에 크게 문제가 되는 것은 PMOS에 negative bias가 걸리면서 발생하는 NBTI이다.

그림 2에 나타낸 것과 같이 PMOS에 bias가 걸리는 stress 상황에서는 V<sub>7</sub>가 점차 높아지고, recovery 상황에서는 V<sub>7</sub>가 낮아지기는 하지만 완전히 회복되지는 않는다. 회로는 이와 같은 과정을 반복하면서 V<sub>7</sub>는 점차 높아지고 이로 말미암아 칩의 동작주파수가 낮아지고, 궁극적으로는 칩의 lifetime을 다하게 하는 결과를 낳는다.

그림 2. NBTI에 의한 PMOS에서의 Vr 변화

기존의 멀티코어 및 매니코어에 대한 연구는 병렬성을 극대화하여 코어 사용의 효율성을 높이고 결과적으로 성능을 높이는 데에 초점을 맞추고 있다. 그러나 공정 발달과 함께 프로세서의 lifetime 신뢰성 문제들이 심화하면서, 최근에는 멀티코어 및 매니코어의 코어를 관리할 때에도 NBTI에 의한 영향을 고려하는 연구들이 많이 진행되고 있다. 특히, 앞으로 매니코어에 집적되는 코어의 수는 수백에서 수천에 이를 것으로 예측되고 있어, 매니코어에서의 코어관리 기법에 대한 연구의 중요성 및 필요성은 점차 증가하는 추세이다. 이미 언급한 바와 같이 NBTI의 영향은 온도가 높을수록 심화한다. 만약 매니코어 상의 수많은 코어 중에 특정 코어에 다른

코어보다 많은 workload가 배치된다면, 그 코어는 다른 코어에 비해 더 많은 열에 노출되게 되고, 그 결과 NBTI에 의한 영향을 많이 받아 다른 코어에 비해 일찍 고장에 이르게 된다. 특별한 관리방식이 적용되지 않은 매니코어에서라면 하나의 코어가 고장 나면이는 전체 시스템의 고장을 의미할 수 있다. 따라서, 매니코어의 코어들에 workload를 배치할 때에는 매니코어의 성능뿐만 아니라NBTI에 의한 aging이 진행되는 속도까지도 고려해야 한다 [3]. 기본적으로 이러한 방식은 코어에 round-robin 방식으로 workload를 배치하여 모든 코어에서 골고루 aging이 진행될 수 있도록한다.

좀 더 심화된 방식에서는 degradation이 진행된 정도를 탐지하여 degradation이 많이 진행된 코어에는 다른 코어들보다 적은 workload를 배치하여 매니코어 시스템의 lifetime을 연장하고자한다. NBTI 모델에 기반을 두어 degradation을 예측하고, 코어가 workload를 처리할 수 있는 정도를 수치로 나타내어 load balancing에 활용하는 연구도 있다 [4]. 이를 capacity rate (CR)이라고 정의하고 있으며, NBTI로 인한 delay의 변화를 사용해서 0에서 1 사이의 확률값으로 나타낸다. 이 값은 각각의 코어에대해 주기적으로 계산하여 업데이트되고, workload를 배치할 때 CR에 의해 양을 결정한다.

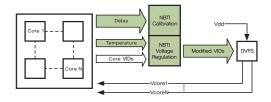

Dynamic voltage frequency scaling (DVFS) 기법은 프로세서의 전력소모를 낮추기 위한 기본적인 방식의 하나로 현재 많은 상용 프로세서에서 지원하고 있다. DVFS는 계산량이 많을 때에는 전압 및 주파수를 높이고, 계산량이 적을 때에는 전압 및 주파수를 낮춰서 필요 이상으로 소모되는 전력을 없애는 방식이다. 이 방식이 도입된 본 의도와는 무관하지만, DVFS는 프로세서의 lifetime 신뢰성 측면에서도 유리한 결과를 가져올 수 있다. NBTI는 회로의 동작전압에 의해서도 가속화되기 때문에 동작전압을 낮추는 DVFS 기법을 적용하면 NBTI에 의해  $V_7$ 가 높아지는 것은 지연시킬 수 있다.

처음 NBTI가 알려지고 이론적으로 정리되던 시기에는 동작전압의 변화에 대해 전혀 고려하고 있지 않기 때문에 전통적인 NBTI 모델에는 전압의 변화는 반영되어 있지 않다. 따라서, DVFS를 지원하는 매니코어에서 NBTI모델을 사용하기 위해서는 모델을 변형해야한다. 예를 들어, V·과 V·2가 지원되는 (V·1 〉 V·2) 매니코어에서 초기에 V·에서 동작하다가 일정 시간 후에 V·2로 변경된다고 하자. 기존의 NBTI 모델을 사용하면 동작전압이 V·2로 변경되는 순간, V·2에

맞추어 degradation을 새롭게 계산한다. 즉, 이전에 V·로 동작하면서 발생한 degradation은 고려하지 못하는 것이다. 최근에는 이전에 동작전압을 시간에 대해 변경이 가능한 값으로 수정하여 새로운 모델을 제시하고 이를 적용하여 연구하고 있다 [5].

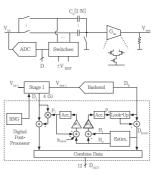

일반적인 DVFS 지원 멀티코어 또는 매니코어 구조에 몇 개의 유 닛을 추가함으로써 NBTI로 인한 회로의 degradation을 반영하여 전압 및 주파수를 scaling하는 구조를 구현할 수 있다 (그림 3). NBTI에 의한 V-의 degradation은 모델링된 수식을 바탕으로 예 측한다. 일반적인 NBTI 모델링에서는 회로 내의 모든 PMOS에 지 속적으로 bias가 걸린다고 가정하기 때문에 실제 degradation 정 도보다 더 나쁘게 예측하는 경향이 있다. 그러나 회로 내의 실제 상황은 이 가정과는 다르므로 단순히 NBTI 모델에 의한 예측값으 로 회로의 고장 여부를 판단하는 것은 지나치게 보수적이다. 그림 3의 NBTI calibration은 이를 보완하기 위한 부분으로, 실제 코어 들로부터 critical path의 delay를 주기적으로 측정하여 이 실제 측정값을 바탕으로 현재 적용하고 있는 NBTI degradation 에 반 영하여 예측값을 수정한다. 이 밖에도 일반적인 회로 내의 PMOS 에서 stress 상황만 지속하는 것이 아니라 stress와 recovery 상 황이 반복된다는 것을 추가로 고려해 넣은 모델을 사용하는 연구 도 진행되고 있다

그림 3. NBTI-aware DVFS framework [5]

위의 방식보다 거시적인 관점에서 동작전압을 관리하여 aging의 진행을 늦출 수도 있다. 일반적으로 프로세서를 설계할 때에는 실 제 필요한 성능보다 높은 성능을 가지게 하여 추후에 회로에 degradation이 발생해도 정상적으로 동작할 수 있도록 한다.

즉, lifetime의 초기에는 프로세서의 성능이 필요 이상으로 높다. 이에 근거하여, lifetime 초기에는 동작전압을 낮추어 aging이 천천히 일어나도록 하고, 일정 시간이 지난 후에는 동작전압을 높여 degradation이 이미 진행된 상황에서도 프로세서가 좀 더 오래 정상적으로 동작할 수 있도록 관리하는 기법들이 있다 [6].

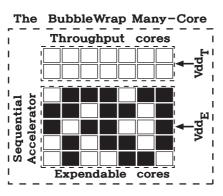

보다 적극적으로 NBTI에 의해 감소하는 매니코어 프로세서의 lifetime을 연장하는 연구들도 있다. 일반적으로 프로세서의 lifetime 신뢰성을 향상하는 방법은 시스템에 redundant 회로를 포함시켜 설계하고 고장이 나는 유닛을 redundant 회로로 대체시키는 것 이다. 이 방법은 일반적으로 같은 형태의 코어를 많이 가지고 있는 매니코어 환경에 적용하기에 적합하다. 이러한 방식은 처음부터 매 니코어 상의 모든 코어를 사용하는 것이 아니고 일부만 사용하다 가, 고장 나는 코어가 발생하면 그 코어를 아직 사용하지 않은 새 로운 코어로 대체시키는 것이다 [7].

공정은 지속적으로 발달하여 하나의 칩에 집적할 수 있는 코어의 수는 꾸준히 증가하는 반면, 칩에 공급할 수 있는 전력에는 한계가 있기 때문에 동시에 on 될 수 있는 코어의 수는 그에 미치지 못할 것이라는 예측이 있다 (그림 4). 이 예측에 근거하면 이와 같은 적 극적은 redundant 코어의 사용이 적절한 방식임을 알 수 있다.

그림 4. ITRS projection에 근거한 매니코어에 공급 전력 부족으로 한 번에 모든 코어가 on될 수 없으며, on되지 않는 코어의 수가 점차 늘어날 것이라는 예측 [8]

관련 연구 중 가장 대표적인 구조로 BubbleWarp 매니코어라는 구조가 있다 (그림 5), 이 구조는 기본적으로 homogeneous매니 코어이며, 코어를 두 개의 그룹으로 나누어 사용한다. Throughput 코어는 어플리케이션에서 parallel 부분을 담당하고, expandable 코어는 어플리케이션의 sequential 부분을 담당한다. Throughput 코어는 비교적 낮은 전압에서 동작하게 하여 NBTI로 인한 degradation을 지연시켜. 오랜 시간 안정적으로 사용할 수 있다.

Expendable 코어들은 NBTI에 의해 aging이 촉진되는 것을 고 려하지 않고 단지 sequential 부분이 빨리 계산되는 것을 목표로 하기 때문에 높은 전압에서 동작하게 하여, 쉽게 고장 날 수 있다. 고장 난 expendable 코어는 그림에서 검게 표시된 것처럼 더 이 상 사용되지 않고, 고장 나지 않고 남아 있는 다른 expendable 코어 중의 하나를 선택하여 추가적으로 사용한다. 이 구조는 공정 의 발달을 최대로 활용하여 가능한 한 많은 수의 코어를 집적하고 코어를 두 그룹으로 나누어 별개의 목적으로 사용함으로써 주어진 전력을 최대한 활용하여 매니코어의 성능을 향상하면서 lifetime도 증가시키고 있다.

그림 5. 일부 코어를 redundant 코어로 사용하여 lifetime 신뢰성을 향상시키는 대표적인 매니코어 구조, BubbleWrap 매니코어 [8]

이제 멀티코어는 마이크로프로세서 분야의 대세가 되었고. 그 발전 의 흐름은 매니코어로 이어지고 있다. 이는 지속적인 공정의 발전 덕분에 가능한 일이지만, 한편으로 공정의 미세화로 말미암아 예전 에는 간과할 수 있었던 NBTI와 같은 문제들이 부각되어, 프로세서 의 lifetime에 크게 영향을 미치고 있다. 따라서 매니코어의 수많 은 코어를 적절히 관리하여 최적의 성능을 제공하면서 일정 정도 의 lifetime을 보장할 수 있는 기법들에 대한 연구가 필수적이다. 나아가 멀지 않은 시기에 일반화될 것으로 여겨지는 3D IC에서는 발열이 가장 심각한 문제로 알려졌으며, 발열은 NBTI 영향을 더욱 심화시킬 것이다. 아직까지 3D IC 구조까지 고려하는 연구가 많지 않지만, 계속되는 공정의 발달과 맞물려 NBTI 영향을 고려하는 매 니코어 신뢰성 연구의 중요성은 계속해서 높아질 것으로 보인다.

### Reference

- [1] Shekhar Borkar, "Thousand Core Chips-A technology Perspective". DAC 2007. pp. 746-749.

- [2] "Intel's 45nm CMOS Technology", Intel Technology Journal, vol. 12, issue 2, pp. 130-145, 2008.

- [3] Lin Huang, Feng Yuan and Qiang Xu, "Lifetime Reliability-Aware Task Allocation and Scheduling for MPSoC Platforms." DATE, 2009.

- [4] Jin Sun et al., "Workload Capacity Considering NBTI Degradation in Multi-core Systems," ASP-DAC, 2010.

- [5] Mehmet Basoglu et al.. "NBTI-Aware DVFS: A New Approach to Saving Energy and Increasing Processor Lifetime." ISLPED, 2010.

- [6] A. Tiwari and J. Torrellas, "Facelift: Hiding and Slowing Down Aging in Multicores." In Int. Symp. on Microarchi-

- [7] Lin Huang and Qiang Xu, "Characterizing the Lifetime Reiliability of Manycore Processors with Core-Level Redundancy." ICCAD, 2010.

- [8] Ulya R. Karpuzcu et al., "The BubbleWrap Manycore Popping Cores for Sequential Acceleration," MICRO, 2009.

### **IDEC** Distinguished Lecturer

### About the Program

IDEC에서는 반도체 관련 분야 저명한 강사님들을 모시고 IDLP를 시작하게 되었습니다. 전국 대학, 기업체, 연구소 등 다양한 기관에서 훌륭한 초청 강연을 보다 손쉽게 접할 수 있는 기회가 되기를 희망합니다. 기술 세미나, 워크샵 등에 본 프로그램의 강사님들을 초청하시어 그 분들의 생각, 비젼, 지식을 공유하시기를 기대합니다. 더불어, 본 프로그램에 강사님으로 활동하실 분들의 적극적인 관심과 참여를 부탁드립니다.

### Current Lecturers

A Path Towards Efficient Design and Verification of Analog /Mixed-Signal Systems

Lecture 2 Lecture 3

Noise and Aperture Analysis of Clocked Comparators What Designers Want from Analog Circuit Optimizers

Lecture 4 Equalizer Design and Performance Trade-offs in ADC-

Signal Integrity Design of TSV Based 3D IC

김정호 교수

Understanding electrical detection of Bio molecule using Nano MOSFET Modeling(From drift- diffusion to quantum)

박영준 교수

Lecture 1 High-Performance and Low-Power ASIC Design Using Pulsed-Latches Low-Power Low-Leakage VLSI Design: Circuits, Design Lecture 2

Methodologies, and Best Practice Lecture 3 Heterogeneous Array of Programmable Logic: Push The Limit of Programmable Device

(KAIST)

홍성철 교수

CMOS RF Power amplifier

강연자와 직접 연락하셔서 강연에 관한 사전 협의(날짜, 장소, 강연 내용)를 해주시기 바랍니다. 강연 관련 비용은 IDEC에서 지불하니, 강연 신청 기관에서는 지불하실 필요가 없습니다.

신청관련 및 자세한 사항은 홈페이지(http://idlp.idec.or.kr)을 참고 바랍니다. 문의: 전항기 (042-350-8535, ihg0929@idec.kaist.ac.kr)

### A/D 변환기 기술동향

서강대학교 전자공학과

안길초 교수 연구분야 : Low-voltage/low-power/high-resolution/high -speed data converters, integrated sensors, analog-front-end for video applications, analog-front-end & back-end for audio applications

E-mail: jaeha@snu.ac.kr http://mics.snu.ac.kr/jaeha

서강대학교 전자공학과

이승훈 교수

연구분야 : 고속 고해상도 CMOS ADC 및 DAC, CMOS Ato-D 인터페이스, integrated sensors 및 혼성모드 집적시스템

E-mail: hoonlee@sogang.ac.kr http://eeic7.sogang.ac.kr

### 서론

반도체 공정기술의 발달로 회로의 집적도가 증가함에 따라 복잡하고 다양한 기능을 갖는 디지털 신호처리 회로의 구현이 가능해 졌으며, 저전력 동작 특성 및 재설계의 용이함 등으로 말미암아 통신 및 멀티미디어 기기 등과 같은 다양한 시스템이 디지털 신호처리 회로를 이용하여 구현되고 있다. 그러나 아날로그로 이루어진 자연계의 원 신호를 디지털 신호로 변환시켜주기 위해서는 그림 1과 같이 아날로그 전기 신호를 디지털 신호로 변환해 주는 A/D 변환기(Analog—to—Digital Converter: ADC)가 시스템 구성에 반드시 필요하며, 제품의 성능을 결정하는 매우 중요한 역할을 하고 있다. 특히 CMOS 공정기술의 발달로 시스템 온 칩(System On a Chip: SoC)의 구현이 보편화하면서 시스템 사양에 필요한 A/D 변환기 기술의 확보는 경쟁력 있는 시스템 설계를 위해 가장 중요한 부분이 되고 있다.

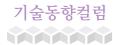

A/D 변환기는 최근 수요가 급증하는 개인 휴대용 통신 기기를 비롯한 광대역 모뎀, Set-Top Box 등과 같은 통신 분야, HDTV, 디지털 캠코더, 디지털카메라, MP3 player, LCD 모니터, 컬러스캐너와 같은 음성 및 영상 신호처리 분야, MRI (Magnetic Resonance Imaging), CT (Computed Tomography), 심박동기(Pacemaker), 보청기 등의 의료기기 분야 등 제반 집적 시스템 산업 전반에 다양하게 사용되고 있으며, 각각의 응용 분야에따라 다양한 성능이 필요하다. 그림 2는 A/D 변환기의 세부 응용분야에따라 다양한 성능이 필요하다. 그림 2는 A/D 변환기의 세부 응용분야에따라 요구되는 해상도와 처리 속도를 보여주고 있으며 이동통신 및 휴대용 멀티미디어를 비롯한 시스템반도체 기술의 발달과 더불어 더 높은 사양의 A/D 변환기에 대한 수요가 지속적으로증가하고 있는 추세이다. 최근에는 다양한 센서를 이용한 인터페이스회로가 시스템에 광범위하게 사용되면서 A/D 변환기의 또 다른 중요 응용분야로 떠오르고 있다.

그림 1. 데이터 변환기 설계 기술의 필요성

이처럼 다양한 응용분야에서 사용되는 A/D 변환기는 해상도와 처리속도 외에도 소비전력, 안정성, 생산 단가 등 시스템에서 중요하

게 요구되는 기준에 의해 사양이 결정된다. 휴대용 기기의 급증과함께 전력 효율은 시스템의 성능을 평가하는 중요 지표가 되고 있으며, 집적도의 증가로 단위면적당 소비전력이 높아지면서 발생하는 발열 문제는 시스템의 안정성 및 생산단가에 큰 영향을 주게 되므로 최근 가장 중요한 평가지표로 여겨지고 있다. 본 고에서는 A/D 변환기의 성능 동향에 대해서 다루고자 한다. 우선 A/D 변환기의 성능 평가 기준에 대해 알아보고 논문을 통해 발표된 A/D 변환기의 사양을 정리하여 해상도, 동작속도, 전력 효율 및 공정 기술 등의 상호 연관 관계를 살펴보기로 하겠다 [1]. 그리고 공정 미세화에 따른 회로설계 제한 요소 및 A/D 변환기 성능과의 관계, 그리고 전력 효율과 성능의 한계 극복을 위한 설계기법 동향 등을살펴보기로 한다.

그림 2. 행상도 및 처리속도에 따른 A/D변환기 세부 응용 분야

### A/D변환기 성능 동향

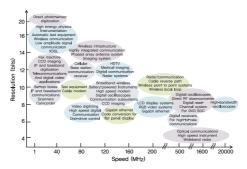

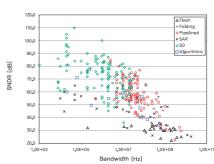

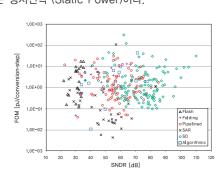

A/D 변환기 설계를 위해서는 샘플링 속도와 해상도 외에도 사용되는 전원전압, 공정, 칩 면적 그리고 시스템에서 요구되는 중요한특성 등에 대한 고려가 이루어져야 하며 이를 통해 최적화된 구조를 선택하게 된다. 그림 2와 같이 다양한 응용분야의 시스템에 요구되는 A/D 변환기 중 상당부분은 축차근사형 (Successive Approximation), 시그마델타 (Sigma-Delta) 그리고 파이프라인 (Pipeline) 구조로 설계되고 있으며, 그 외에도 사양에 따라 플래쉬 (Flash), 인터폴레이팅 (Interpolating), 폴딩 (Folding), 적분형 (Integrating), 2단 (Two-Step), 타임-인터리브드 (Time-Interleaved) 등과 같이 다양한 구조가 사용되고 있다. 그림 3은 1997년에서 2011년 사이 IEEE International Solid-State Circuits Conference (ISSCC)와 VLSI Circuit Symposium에 발표된 A/D 변환기의 사양을 입력신호의 주파수 영역 (Band

Width: BW)에 따른 신호대 잡음비 (Signal to Noise and Distortion Ratio: SNDR)로 사용된 A/D 변환기의 구조에 따라 도시한 그래프이다.

그림 3. A/D 변환기 성능 데이터 (ISSCC, VLSI Circuit Symposium 1997-2011): 입력신호 BW에 따른 SNDR

목표 해상도에 따른 A/D 변환기의 구조를 살펴보면, 높은 SNDR 성능을 갖는 경우 시그마델타 구조의 A/D 변환기가 주로 사용되고 있으며 10비트에서 12비트 해상도의 경우는 파이프라인 구조의 A/D 변환기, 그리고 저해상도에서는 플래쉬 구조의 A/D 변환기가 주로 사용되고 있음을 확인할 수 있다. 또한, 입력 신호의 BW에 따른 A/D 변환기의 구조를 살펴보면 낮은 주파수 영역에서는 시그마델타 구조가, 10MHz~1GHz의 경우 파이프라인 구조, 그리고 1GHz 이상의 고속 동작에서는 플래쉬 구조가 주로 사용되고 있음을 확인할 수 있으며, 이러한 경향은 각각의 동작 영역에서 사용된 구조가 최적의 효율을 보여주고 있음을 나타낸다고 하겠다.

이처럼 다양한 구조와 샘플링 속도, 해상도 그리고 소비전력을 갖도록 설계된 A/D 변환기의 성능을 비교하기 위해 (1)과 같이 전체소비 전력을 샘플링 속도와 해상도를 이용하여 정규화한 성능지수 (Figure Of Merit: FOM)를 일반적으로 사용하고 있다 [2].

$$FOM = \frac{P}{f_S \cdot 2^{ENOB}} \tag{1}$$

$$ENOB = \frac{SNDR(dB) - 1.76}{6.02}$$

(2)

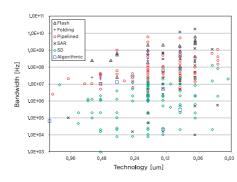

최근 A/D 변환기의 신호대잡음비가 주로 회로의 열잡음(Thermal 도 회로 및 구조의 최적 Noise)에 의해 제한되면서 해상도 증가에 따른 소비전력의 증가 A/D 변환기의 파워 온/S율이 기존 양자화 잡음에 의해 결정되던 경우보다 증가하고 있다. 가 진행되고 있다 [5-9].

그림 4는 A/D 변환기의 SNDR에 따른 FOM을 나타낸 그래프이 다. SNDR이 높아질수록 해당 성능을 보이는 FOM의 최저값이 점 차 증가하는 경향을 보이고 있으며 이는 1비트의 해상도를 증가시 킬 때 2배의 전력소모를 가정하는 기존의 FOM과 달리 A/D 변환 기의 성능이 열잡음에 의해 제한되어 1비트의 해상도를 높일 때마 다 4배의 전력소모가 추가적으로 필요하기 때문에 생기는 현상이 다 [2], 이처럼 잡음에 의한 전력효율 저하의 문제를 해결하기 위 해 단위소자의 열잡음 특성 개선 및 저잡음 특성이 있는 A/D 변 환기 구조 개발에 대한 연구가 진행되고 있다. A/D 변환기를 포함 한 아날로그 회로의 전력 소모는 일반적으로 다음의 네 가지에서 기인한다. 첫째는 회로의 커패시터성분이 스위칭 동작에 의해 충 방전되면서 발생하는 다이나믹 소비전력이며, 둘째는 CMOS 디지 털 회로의 출력신호가 변할 때 발생하는 단락회로 전류(Short-Circuit Current)에 의한 소비전력, 셋째는 회로상에서 발생하는 누설전류(Leakage Current)에 의한 소비전력, 그리고 마지막으 로 증폭기 등과 같은 회로에서 바이어스 제공 등을 위해 항상 사 용되는 정지전력 (Static Power)이다.

그림 4. A/D 변환기 성능 데이터 (ISSCC, VLSI Circuit Symposium 1997-2011): SNDR에 따른 FOM

이와 같은 소비전력 요인들을 기존의 A/D 변환기 회로에서 분석 하여 최적화함으로써 전력 효율을 높이기 위한 연구가 활발히 진 (1) 행되고 있다. [3]은 SAR A/D 변환기의 새로운 스위칭 방법을 제 안하고 있으며 이를 통하여 구동되는 커패시터의 크기를 줄임과 (2) 동시에 충방전에 필요한 전력을 최소화하였다. [4]는 증폭기 공유 및 커패시터를 재사용하는 방법으로 소비전력을 줄였으며 그 외에 제외 도 회로 및 구조의 최적화와 시스템에서의 동작 타이밍에 따른 증가 A/D 변환기의 파워 온/오프를 통하여 전력 소모를 최적화는 연구 가 지해되고 있다 [5-0]

### CMOS 공정 스케일링에 따른 영향

CMOS 공정 기술의 발전과 그에 따른 단위 소자의 미세화 및 고속화는 다양하고 복잡한 기능의 디지털 신호처리 회로 집적을 통해 단일 칩 시스템 (SoC) 설계를 가능하게 하였으며, 디지털 회로의 소비전력과 면적을 감소시킴으로써 생산원가 절감과 함께 자원의 효율적인 이용을 통한 친환경적 시스템을 구현할 수 있게 하였다. 그러나 미세 소자의 신뢰성 확보를 위한 낮은 전원 전압의 사용 및 소자 특성의 열화 등으로 말미암아 아날로그 회로 설계는 점점 더 어려워지고 있다.

저전압 동작은 스위치커패시터(Switched Capacitor: SC) 회로에 사용되는 플로팅 스위치의 동작 문제, 신호의 크기가 작아지면서 상대적으로 커지게 되는 노이즈 문제, 그리고 증폭기의 출력 범위가 제한되면서 발생하는 신호의 왜곡현상 등이 해결해야할 주요 문제가 되고 있으며, 고유이득(intrinsic gain: gm/gds) 감소로 인한 다단 증폭기의 사용 및 스트레스 효과 (Stress Effect), 월 근접효과 (Well Proximity Effect) 등은 회로의 효율 및 성능을 제한하는 요소가 되고 있다 [10].

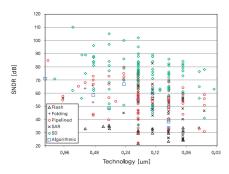

그림 5는 CMOS 공정기술에 따라 다양한 구조로 설계된 A/D 변환기의 SNDR을 나타낸 그래프이다. CMOS 공정 기술이 미세화되면서 각 공정에서 동일한 구조로 구현된 A/D 변환기의 최대 SNDR이 점차 감소함을 확인할 수 있다. 이러한 성능의 저하는 앞서 설명하였듯이 저전압 동작에 따른 신호 크기의 감소로 말미암아 상대적인 잡음이 증가하면서 발생한 문제이며 높은 전력효율을 갖는 고해상도의 A/D 변환기 설계에 걸림돌이 되고 있다.

그림 5. A/D 변환기 성능 데이터 (ISSCC, VLSI Circuit Symposium 1997-2011): CMOS 공정기술에 따른 SNDR

반면에 단위 소자의 고속 동작은 A/D 변환기의 샘플링 속도를 향상시키는데 큰 역할을 하였다. 그림 6은 CMOS 공정기술에 따라다양한 구조로 설계된 A/D 변환기의 입력 신호 BW를 나타낸 그래프이다. CMOS 공정 기술이 미세화되면서 각 공정에서 구현된 A/D 변환기의 최대 BW가 점차 증가함을 확인할 수 있다. 단, 45nm 이하의 CMOS 공정에서 신호의 BW가 증가하지 못한 이유는 아직 공정이 보편화하지 않아 A/D 변환기의 개발이 완료되지 않은 상태이기 때문으로 해석할 수 있다.

그림 6. A/D 변환기 성능 데이터 (ISSCC, VLSI Circuit Symposium 1997-2011): CMOS 공정기술에 따른 입력신호 BW

단위 소자의 미세화에 따른 고속 동작 특성은 입력 신호의 BW뿐만 아니라 A/D 변환기의 구조에도 큰 변화를 일으키고 있다. 단위회로의 동작 속도가 높아지면서 전통적으로 낮은 샘플링 속도에서 동작하던 SAR나 시그마델타 구조의 A/D 변환기가 점차 비디오나통신 시스템에 응용 가능한 수준으로 동작 속도가 향상되고 있다[3][11-13]. 특히 SAR 구조의 A/D 변환기는 증폭기를 사용하지않고 최소의 아날로그 회로만을 이용하여 구현 가능하므로 높은 전력효율 특성을 얻을 수 있으며, 증폭기 이득 등과 같이 CMOS 공정 스케일링에 따른 회로의 성능 제약으로부터 받는 영향이 다른 구조의 A/D 변환기보다 적기 때문에 최근의 공정 트렌드에 적합한 구조라고 할 수 있다.

델타시그마 구조의 경우도 비교적 낮은 사양과 최소한의 아날로그 단위 회로를 사용하여 오버샘플링과 잡음변형을 통해 높은 해상도를 구현하므로 최근의 나노 CMOS 공정을 사용한 시스템에서 응용범위를 넓혀가고 있다. 특히 이동통신 시스템의 사양이 높아지면서 요구되는 고해상도의 SNDR 구현을 위해 시그마델타 구조의 A/D 변환기에 대한 관심이 증가하고 있다. 또한, 오버샘플링으로 프론트엔드에 필요한 필터의 요구사양을 낮출 수 있어 전체적으로 시스템 설계를 용이하게 하고 소비전력을 낮추는 장점이 있다.

### 디지털 보정기법을 이용한 A/D 변환기

CMOS 공정 기술의 미세화로 디지털 회로의 크기 및 소비전력이 급격히 감소하면서 이러한 장점을 A/D 변환기 설계에 이용하고자하는 다양한 연구가 활발히 진행되고 있다. 아날로그 회로의 사용을 최소화하여 소비전력 및 면적을 줄이고 이때 발생하는 성능 저하를 디지털 신호처리를 이용하여 보정함으로써 전체적인 전력 효율을 개선하게 된다.

그림 7은 디지털 보정을 이용하여 전력효율을 개선한 대표적인 사례라고 할 수 있다 [14]. 스위치커패시터 회로로 구현된 CMOS A/D 변환기는 전통적으로 피드백을 이용한 연산증폭기 (Operational Amplifier: op-amp)를 기반으로 동작하며 연산증폭기의 성능에 따라 전체 변환기의 성능이 결정된다. 이때 피드백 구조는회로의 선형성을 개선하는 매우 중요한 역할을 하지만 증폭기의 동작속도를 감소시키게 되며 결과적으로 소비전력을 증가시킨다.

그림 7. 디지털 보정기법을 이용한 A/D 변환기 [14]

[14]는 open-loop 구조의 간단한 증폭기회로를 사용하여 BW에 대한 소비 전력을 크게 감소시켰으며 그에 따른 회로의 선형성 저 하를 디지털 영역에서 보상함으로써 전체적인 A/D 변환기의 성능 을 유지하였다. 다만, 목표로 하는 해상도가 높아질수록 선형성 개 선을 위해 필요한 디지털 회로의 보정 계수를 구하기 위한 시간이 증가하게 되어 동작 조건의 변화 시 즉각적으로 대응하기 어려운 문제가 발생하게 되며 이러한 문제를 개선하기 위한 다양한 연구 가 진행되고 있다 [15-17]. 그림 8과 같이 A/D 변환기를 병렬로 연결하는 타임-인터리브드 구조는 주어진 공정에서 샘플링 속도를 증가시키기 위해 가장 보편적으로 사용되는 구조이다 [18]. 그러나 채널 간에 발생하는 오프셋, 이득, 및 타이밍 부정합 등에 의해 A/D 변환기의 성능이 제한되는 문제점이 발생하며 이러한 부정합 을 제거하기 위해 디지털 영역에서 보정기법들이 사용되고 있다. [19]는 16개의 6비트 SAR A/D 변환기를 이용한 타임-인터리브 드 구조의 A/D 변환기로 채널 간에 발생하는 부정합을 디지털 영 역에서 보상하여 40GS/s의 고속 동작 성능을 구현한 예이다.

그림 8. 타임-인터리브드 구조의 A/D 변환기

### 맺는밀

이상으로 A/D 변환기의 응용분야 및 요구사양에 따른 구조와 중요한 성능지표가 되고 있는 전력효율의 개선을 위한 회로 설계 동향 등을 발표된 논문 자료들을 이용하여 정리하여 보았다. 살펴본 바와 같이 CMOS 공정기술의 발전과 더불어 A/D 변환기의 성능 또한 지속적으로 향상되고 있으며 다양한 응용분야에서 새로운 시스템의 개발 및 성능 개선에 큰 역할을 하였다. 최근 CMOS 공정기술이 미세화함에 따라 발생하는 아날로그 회로 설계의 문제점들이 부각되면서 이를 해결하고자 하는 다양한 연구가 이루어지고 있으며, 궁극적으로는 아날로그 회로의 사용을 최소화하고 이때 발생하는 성능 저하의 문제들을 저전력 소면적의 디지털회로를 통해 개선하는 구조의 A/D 변환기가 주류를 이룰 것으로 예상한다.

### **Reference**

- [1] B. Murmann, "ADC Performance Survey 1997–2011," [Online]. Available: http://www.stanford.edu/~murmann/adcsurvey.html.

- [2] R. H. Walden, "Analog-to-digital converter survey and analysis," IEEE J. Select. Areas Commun., vol. 17, no. 4, pp. 539–550, Apr. 1999.

- [3] C. Liu, et al., "A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure," IEEE J. Solid-State Circuits, vol. 45, no. 4, pp. 731-740, Apr. 2010.

- [4] N. Sasidhar, et al., "A low power pipelined ADC using capacitor and opamp sharing technique with a scheme to cancel the effect of signal dependent kickback," IEEE J. Solid-State Circuits, vol. 44, no. 9, pp. 2392–2401, Sep. 2009.

- [5] Young-Ju Kim, et al., "A 12bit 50MS/s CMOS Nyquist A/D converter with a fully differential class-AB switched op-amp," IEEE J. Solid-State Circuits, vol. 45, no. 3, pp. 620–628, Mar. 2010.

- [6] D. Kasha, et al., "A 16-mW, 120-dB linear switched-capacitor delta-sigma modulator with dynamic biasing," IEEE J. Solid-State Circuits, vol. 34, no. 7, pp. 921–926, Jul. 1999.

- [7] H. Choi, et al., "A 52mW 0.56mm2 1.2V 12b 120MS/s SHA-free dual-channel Nyquist ADC based on mid-code calibration," IEEE International Symposium on Circuits and Systems (ISCAS), pp. 9–12, May 2008.

- [8] H. Choi, et al, "A 14b 150MS/s 140mW 2,0mm2 0,13um CMOS A/D converter for software defined radio systems," International Journal of Circuit Theory and Applications, vol. 39, pp. 135–147, Feb. 2011.

- [9] M. Kim, P. Hanumolu, and U. Moon, "A 10MS/s 11-b 0,19mm2 algorithmic ADC with improved clocking scheme," IEEE J. Solid-State Circuits, vol. 44, no. 9, pp. 2348–2355, Sep. 2009.

- [10] G. Ahn, et al., "A 0.6V 82dB delta-sigma audio ADC using switched-RC integrators," IEEE J. Solid-State Circuits, vol. 40, no. 12, pp. 2398-2407, Dec. 2005

- [11] W. Liu, P. Huang, and Yun Chiu, "A 12b 22,5/45MS/s 3.0mW 0.059mm2 CMOS SAR ADC achieving over 90dB SFDR," IEEE Int. Solid-State Circuits Conf., pp. 166–167, Feb. 2005.

- [12] R. Schreier, et al., "A 375–mW quadrature bandpass  $\Delta \Sigma$  ADC with 8.5–MHz BW and 90–dB DR at 44 MHz," IEEE J. Solid–State Circuits, vol. 41, no. 12, pp. 2632–2640, Dec. 2006.

- [13] Y. Fujimoto, et al., "A 100 MS/s 4 MHz bandwidth 70 dB SNR Δ Σ ADC in 90 nm CMOS," IEEE J. Solid-State Circuits, vol. 44, no. 6, pp. 1697–1708, Jun. 2009.

- [14] B. Murmann and B. E. Boser, "A 12-bit 75-MS/s pipelined ADC using open-loop residue amplification," IEEE J. Solid-State Circuits, vol. 38, no. 12, pp. 2040-2050, Dec. 2003.

- [15] J. Li and U. Moon, "Background calibration techniques for multistage pipelined ADCs with digital redundancy," IEEE Trans. Circuits Syst. II, vol. 50, no. 9, pp. 531–538, Sep. 2003.

- [16] J. McNeill, et al., "Split ADC" architecture for deterministic digital background calibration of a 16-bit 1-MS/s ADC," IEEE J. Solid-State Circuits, vol. 40, no. 12, pp. 2437-2445, Dec. 2005.

- [17] K. Hsueh, et al, "A IV 11b 200MS/s pipelined ADC with digital background calibration in 65nm CMOS," ISSOC Dig. Techn. Papers, pp. 547–548, Feb. 2008.

- [18] C. Conroy, D. Cline, and P. Gray, "An 8-b 85-MS/s parallel pipeline A/D converter in 1-um CMOS," IEEE J. Solid-State Circuits, vol. 28, no. 4, pp. 447-454, Apr. 1993.

- [19] Y. Greshishchev, et al, "A 40GS/s 6b ADC in 65nm CMOS," ISSCC Dig. Techn, Papers, pp. 390-391, Feb. 2010.

# 반도체 기반테라헤르츠이미징 기술

연구 동향

고려대학교 전기전자전파공학부

이재성 교수

연구분야: 밀리미터파 초고속 소자 및 회로 연구 E-mail: jsrieh@korea.ac.kr

http://hsisl.korea.ac.kr/

서론

테라헤르츠 대역의 정의는 여러 연구진 및 문헌마다 약간의 차이를 보이지만, 비교적 관대한 관점에 의한다면 0.1THz - 10THz의 영역을 지칭하게 된다. 파장으로 환산하여 볼 때 3mm 에서 30μm에 이르는 이 대역은 전통적 파장 대역 분류에 의거할 때 밀리미터 파(millimeter wave), 서브밀리미터파 (submillimeter wave), 그리고 원적외선(far infrared)의 일부에 걸쳐 있게 된다. 이 테라헤르츠 대역은 양 인접 대역인 마이크로파 및 광파 대역에 비해 상대적으로 연구 개발 및 그 응용이 미진했는데, 그 이유로서는 이대역에서 신호를 발생시키고 처리할 수 있는 소자의 부재가 그 큰원인으로 지목된다. 그러나 최근 들어 다양한 소자의 성능 향상에따라 이러한 장벽이 많이 낮아졌을 뿐 아니라, 테라헤르츠 대역만이 가진 특성에 대한 관심의 증대에 힘입어 이 대역을 활용하려는연구가 활발하게 진행되고 있다.

테라헤르츠 대역의 응용 영역으로서는 천문/기상 관측, 시간영역 분광(time-domain spectroscopy, TDS), 보안 검색(security), 제품 품질 관리(product quality control), 각종 생물/의학 (bio/medical) 응용, 그리고 최근 들어 부각되고 있는 광대역 통 신 등을 들 수 있겠다. 이 중 보안 검색, 제품 품질 관리, 생물/의 학 응용 등은 많은 경우 테라헤르츠 영상 기술에 기반을 두고 있으 며, 현재 테라헤르츠 응용 분야의 큰 부분을 차지하고 있다고 할 수 있겠다.

테라헤르츠 파는 플라스틱, 종이, 옷 등과 같은 다양한 포장성 물질에 대해 투과성이 우수한 반면 수분을 포함한 물질에 대해서는 투과성이 크게 떨어지는 경향을 보여주고 있어 다른 주파수 대역 과는 대별되는 고유한 특성을 지니고 있다. 따라서 이러한 특성을 적절히 활용하는 경우 타 이미징 기술과는 다른 측면에서의 응용 가능성을 보일 수 있다. 본 고에서는 이러한 테라헤르츠 이미징 기술에 대한 개요와 함께 그중에서도 반도체 전자소자에 기반을 둔연구의 최근 동향을 살펴보기로 하겠다.

### 이미징 기술의 개요

이미징 기술은 어떤 물체에 반사되거나 투과된, 혹은 물체로부터 자연 방사된 전자기파를 2차원적으로 mapping함으로써 그 물체 에 대한 영상 정보를 얻는 기술을 의미한다. 테라헤르츠 기술이 널 리 활용되는 TDS가 일반적으로 해당 물체의 평균적인 특성을 보 는 것이라면 이미징은 부위별 특성을 볼 수 있다는 면에서 차별성 이 있다고 할 수 있겠다. 이미징 기술은 다시 그 방식에 따라 능동이미징(active imaging)과 수동 이미징(passive imaging)으로 나누어 볼 수 있다. 능동 이미징은 전자기파 신호를 인위적으로 발생, 방사시켜 특정 물체 조사를 한 후, 반사 혹은 투과된 신호를 검출하여 영상화하는 방식을 의미한다. 이에 반해 수동 이미징은 특정 물체가 자연 방사하거나 혹은 자연광을 반사시킨 신호를 검출하여 영상화하는 방식을 지칭한다.

능동 이미징은 신호 발생을 위한 시스템이 부가적으로 요구된다는 면에서 좀 더 복잡하고 비용이 든다는 단점이 있지만 검출단에서 요구되는 신호대잡음비(SNR)의 조절할 수 있다는 면에서 높은 품 질의 영상을 얻기에 용이한 점이 있다. 이와 함께 특정 주파수를 선택할 수 있다는 점도 장점이 될 수 있으며, 가장 대표적인 능동 이미징 시스템으로서 레이더를 들 수 있다.

수동 이미징은 검출단의 구현만으로 시스템이 완성된다는 간편성이 있으나, 높은 SNR을 얻기에 상대적인 어려움이 있고, 이에 따라 가능하면 더 넓은 주파수 범위의 신호를 검출해야 신호의 감도를 높일 수 있으므로 광대역 검출이 이루어져 한다는 부담도 있다. 일반적인 사진 기술이 대표적인 수동 이미징 기술이라 할 수 있겠다. (단, 플래쉬를 사용하는 경우는 그 정의에 따라 능동 이미징으로 볼 수 있다.)

또한, 이미징 기술은 영상을 구현하는 방식에 따라 스캔 이미징 (scanned imaging) 방식과 실시간 이미징 (real-time imaging) 방식으로 나누어 볼 수도 있다. 스캔 이미징은 하나의 검출소자를 사용하되 대상 물체(혹은 검출기)를 x 및 y축 방향으로 순차적으로 스캔하면서 데이터를 축적하여 2차원 영상을 구현하는 방식을 일 반적으로 가리킨다. 혹은 일렬로 배열된 1차원 검출소자 array를 사용하면서 x 혹은 y축 한 방향으로 스캔하여 2차원 영상을 얻는 방식도 스캔 이미징 방식으로 볼 수 있다. 이에 반해 실시간 이미징은 2차원으로 배열된 검출소자 array를 사용하여 스캔 없이 한 번의 노출로 전체 2차원 영상을 구현하는 방식을 말한다.

디지털카메라에 사용되는 CCD(Charge-Coupled Device)나 CIS(CMOS Imaging Sensor)가 실시간 이미징 검출소자의 좋은 예라 할 수 있겠다. 스캔 이미징은 작은 면적과 적은 전력을 소모한다는 장점이 있는 반면 실시간 이미징은 전체 영상을 획득하는 시간이 짧고 물체의 정지 여부에 상관없이 실시간으로 영상 추적할 수 있다는 장점이 있다.

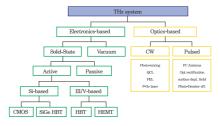

그림 1. 테라헤르츠 시스템 구현을 위한 다양한 접근 방식 [1]

이미징 기술은 사용하는 전자기파의 대역에 따라서도 여러 가지로 대별이 될 수 있다. 광 기술에 기반을 둔 이미징 기술의 예로서는 상당히 짧은 파장을 활용하는 x-ray 영상을 비롯하여 가시광선을 사용하는 일반 사진 기술, 어두운 환경에서의 물체 식별에 활용되는 적외선 사진 기술 등을 들 수 있다. 한편, 전자 기술에 기반을 둔 이미징 기술의 예로는 앞서 언급한 마이크로파 레이더가 그 좋은 예라 할 수 있겠다. 테라헤르츠 이미징 기술은 이 두 가지 방식의 중간에 있는 기술로서 광파와 마이크로파의 사이에 있는 테라헤르츠 대역 전자기파에 기반을 두고 있다. 이에 대한 내용을 다음절에서 보다 자세히 알아보도록 한다.

### 테라헤르츠 이미징 기술의 개요

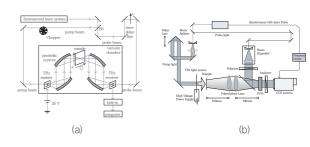

광 기술과 전자 기술은 각기 오랜 기간을 거치면서 고도의 기술 축적을 이루어 왔으며, 따라서 테라헤르츠 시스템의 구현은 일반적 으로 그림 1에서 보이는 바와 같이 광 소자 또는 전자 소자에 기반 을 두어 이루어진다. 테라헤르츠 이미징 기술도 따라서 광 기술에 기반한 방식과 전자 기술에 기반을 둔 방식으로 대별되어 발전해 오고 있다. 이 가운데 상대적으로 먼저 테라헤르츠 시스템의 구현 에 적용된 기술은 광 기술이며, 따라서 테라헤르츠 이미징 기술도 광 기술에 기반을 두어 먼저 개발되고 활용됐다. 광 기술은 다시 펄스에 기반을 둔 기술과 연속파(Continuous Wave, CW)에 기 반을 둔 기술로 대별이 되는데. femto-second 레이저를 일반적 으로 활용하는 펄스 기반 기술이 그 구현의 상대적 용이성으로 말 미암아 특성상의 열세에도 불구하고 보다 널리 적용되어 오고 있 다. 펄스 기술을 사용한 이미징 시스템의 예가 그림 2에 나타나 있 다. 그림 2 (a)는 스캔 방식의 예를, 그림 2 (b)는 실시간 방식의 예를 보이고 있다. 두 경우 모두 매우 짧은 광 펄스를 제공하는 femto-second 레이저에 기반을 두어 테라헤르츠 펄스를 발생시 키고 이를 대상 물체에 투과시켜 그 투과된 펄스에 기반을 두어 영 상을 구현한다는 공통점을 지니고 있다. 단 스캔 방식은 그림에 나타난 바와 같이 대상 물체를 2차원적으로 스캔해 가면서 영상을 획득한다는 점이 그 차이라고 할 수 있다.

한편, 테라헤르츠 시스템 구현에 사용되는 전자 소자 기술은 그림 1에서 보여지는 바와 같이 다시 진공 소자(vacuum device) 및 고체 소자(solid-state device)로 나누어 볼 수 있다. 진공 소자 로는 일반적으로 테라헤르츠 신호의 발생에 사용되며, klystron, TWT(Traveling Wave Tube), BWO(Backward Wave Oscillator), gyrotron 등이 그 대표적인 예라 할 수 있겠다. 이들 진공소자는 100GHz 이상의 대역에서 수 W - 수 MW급의 출력을 낼수 있다는 장점이 있으나 크기가 커서 작은 공간에 집적하기 힘들다는 단점이 있다. 이에 반해 주로 반도체에 기반을 둔 고체 소자는 진공 소자에 비해 작은 면적에 구현할 수 있고 적은 전력을 소모하며, 다른 전자소자들과의 집적이 용이하기 때문에 실용적인 면에서 큰 장점을 지니고 있다.

그림 2. 광 펄스 기반 테라헤르츠 이미징 시스템

(a) 스캔 이미징 (b) 실시간 이미징

고체 전자 소자는 다시 다이오드 계열과 트랜지스터 계열로 나누어 볼 수 있다. 다이오드 계열은 동작 속도가 상대적으로 높다는 장점이 있는 반면, 증폭 기능이 없으므로 기본적인 신호의 발생 및 검출은 가능하나 그 성능이 상대적으로 떨어지고 또한 일반적으로 트랜지스터에 기반을 둔 타 회로 블록과의 집적이 용이하지 않다. 반면 트랜지스터 계열은 잘 알려진 바와 같이 증폭과 스위칭 특성을 제공하므로 다양한 기능과 우수한 성능을 가진 시스템을 구현할 수 있다. 단지 동작속도가 충분하지 못해 테라헤르츠 대역에의 적용이 어려웠던 것이 사실이나, 최근 들어 크게 향상된 속도에 힘입어 이미징을 비롯한 각종 테라헤르츠 시스템에 활발하게 적용되어 가고 있다.

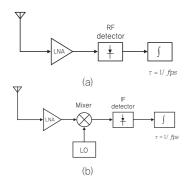

그림 3. 전자소자 기반 이미징 시스템 (a) 직접 검출 (direct detection) 방식 (b) 헤텔다인 검출 (hetetodyne detection) 방식

이와 같은 전자소자에 기반을 둔 테라헤르츠 이미징 시스템은 (능 동 이미징에 사용되는) 신호 발생단은 다양한 소자에 기반을 두고 구현이 되나, 검출단은 대개 다이오드 혹은 트랜지스터에 기반을 두어 구성이 된다. 이러한 검출단은 다시 두 가지 방식으로 대별될수 있다. 직접 검출(direct detection) 방식과 헤테로다인 검출 (heterodyne detection) 방식이 그것이다 (그림 3). 직접 검출 방식은 검출된 신호의 주파수 대역을 그대로 유지한 상태에서 신호의 세기를 DC 신호로 변환하여 영상 신호로 처리하는 반면, 헤테로다인 검출 방식은 검출된 신호를 보다 낮은 주파수로 낮춘 후 신호의 세기를 DC 신호로 변환하는 방식이다. 헤테로다인 방식은 주파수의 변환을 위해 혼합기(mixer) 및 이를 구동하기 위한 LO(local oscillation) 공진기가 필요하므로 회로의 복잡도가 증가하고 전력 소모가 커진다는 단점은 있으나, 전반적으로 더 뛰어난 검출 특성을 보이는 것으로 나타난다.

그림 4. (a) Dicke radiometor (b) Total power radiometer

전자소자 기반 검출단은 Dicke 스위치를 사용한 방식(Dicke radiometer)와 사용하지 않은 방식(total power radiometer)으로 나누어 볼 수도 있다 (그림 4). Dicke 스위치는 검출단 회로 내에서 안테나와 기준저항 사이를 주기적으로 스위칭하는 기능을 수행하며, 검출단에서 발생하는 1/f 잡음의 영향을 제거하여 잡음 특성을 향상시키게 된다. Dicke 스위치는 mechanical chopper 등을 사용하여 외부적으로 구성할 수도 있으나, 집적된 반도체 기반

스위치는 여러 가지 방식으로 비교적 용이하게 구현 가능하므로 이러한 Dicke 스위치를 칩 상에 구현할 수 있다는 점도 반도체 기반테라헤르츠 이미징 시스템의 장점 중의 하나라고 할 수 있겠다.

### 반도체 기반 테라헤르츠 이미징 연구동향

반도체 소자의 동작 속도가 크게 향상됨에 따라 최근 들어 100GHz 이상의 대역에서 동작하는 반도체 기반 테라헤르츠 이미 징 회로를 연구한 결과가 많이 발표되고 있다. 본 절에서는 이들연구 결과를 소개하고 분석을 하고자 한다.

그림 5, UT Dallas 연구진의 SBD 기반 280GHz 이미징시스템

(a) 검출단 회로도 (b) 지갑 외부 및 THz 이미징으로 얻은 지갑 내의 물체 영상 [2]

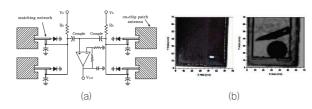

상용 Si CMOS 공정에서 제공하는 Schottky barrier diode (SBD)에 기반을 둔 이미징 회로에 대한 연구가 최근 University of Texas at Dallas에서 활발히 진행되고 있다 [2]. 이 연구진에서 개발한 검출단은 UMC의 130nm CMOS 공정에 기반을 둔 SBD를 사용하여 직접 검출 방식으로 설계되었으며, 그림 5(a)에 보이는 바와 같이 칩 상에 구현된 패치 안테나와 함께 4개의 채널로 구성이 되어 있고 증폭기를 통하여 신호가 출력되도록 구현이되었다. 검출기의 감도를 나타내는 responsivity는 21kV/W로 측정되었고, 잡음 특성을 나타내는 NEP(Noise Equivalent Power)는 40pW/Hz<sup>0.5</sup>의 값을 보였다.

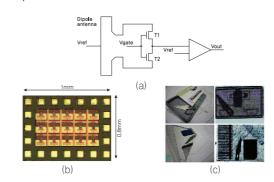

그림 6. Univ. of Wuppertal 연구진의 CMOS 기반 1 THz 이미징시스템

(a) 검출단 회로도 (b) 칩 사진 (c) 1 THz 투과 영상 [5]

제작된 검출기 회로와 VDI 사의 상용 280GHz 테라헤르츠 신호 발생기를 결합하여 능동 이미징 시스템이 구성되었으며 82uW의 신호 방사에 의한 가죽 지갑 내 금속 물체의 테라헤르츠 이미지가 이 시스템을 통해 획득되었다 (그림 5(b)).

그림 7. UCLA 연구진의 CMOS TRR 기반 THz 이미징시스템

(a) 검출단 회로도 (b) 칩 사진

(c) 종이 박스로 가려진 플로피 디스크의 183GHz 투과 영상 [6]

독일의 University of Wuppertal에서는 상용 CMOS 소자를 passive resistive mixer로 활용하여 테라헤르츠 검출단을 구성 하는 연구가 수년 전부터 활발히 이루어지고 있다. 250nm 소자에 기반을 둔 600GHz 검출단에 대한 회로 특성 및 이를 활용한 능 동 이미징 시스템에 대한 연구가 2008년에 처음 발표된 이래 [3] 유사한 관련 연구가 계속되어 진행되어 오고 있으며, SiGe HBT에 기반을 둔 검출단도 역시 개발이 된 바 있다 [4]. 최근 발표된 65nm CMOS 소자에 기반을 둔 검출단은 1THz에서의 이미징을 획득하는데 성공하였다 [5], 그림 6에 나타난 바와 같이 loop형 다 이폴 안테나와 집적된 게이트 공통 차동 믹서단을 활용한 이 회로 는 1THz에서 800V/W의 responsivity 및 66pW/Hz<sup>0,5</sup>의 NEP 특성을 보여 주었으며, 특히 칩 하단에 실리콘 렌즈를 부착함으로 써 SNR 을 7-15dB 가량 향상시킬 수 있었다. 이 검출단 회로는 x54 주파수 체배기에 기반을 둔 1 - 10uW 출력 1THz 신호 발생 기와 결합하여 능동 이미징 시스템의 구현에 적용되었으며, 이로부 터 얻어진 이미지가 그림 6(c)에 나타나 있다. 그림에서 보듯 이미 지는 해상도 및 명암 대비가 상당히 뛰어나며, 이는 최적화된 회로 및 안테나 설계, 그리고 칩에 부착된 실리콘 렌즈에 기인한 것으로 사료된다.

최근 UCLA에서는 65nm CMOS 기반 time-encoded regenerative receiver(TRR)를 활용한 테라헤르츠 검출단을 개발하였다 [6]. 그림 7에 나타난 바와 같이 칩 상에 패치 안테나가 집적된이 회로는 183GHz 에서 1.51fW/Hz<sup>0.5</sup>의 NEP를 나타내었으며 TRR 특성상 13.5mW에 불과한 매우 작은 전력 소모를 보여주었다는 점이 특기할 만하다. 이 검출기는 상용 부품으로 꾸며진 183GHz 신호 발생기와 함께 테라헤르츠 능동 이미징 시스템의 구현에 사용되었으며 그림 7(c)는 이 시스템에 기반을 두고 얻어진종이 박스 아래에 가려진 플로피 디스크의 영상이다. 그림에서 보듯이 이미지의 품질은 좀 더 개선될 여지가 있으나,역시 새로운검출 topology가 사용되었다는 점과 검출기의 전력 소모가 작다는점은 의미가 있는 연구 결과라할 수 있겠다.

이상으로는 주로 능동 이미징 시스템에 대한 최근 연구 결과를 살펴보았다. 수동 이미징 시스템에 대한 연구도 근래 들어 매우 활발하게 이루어지고 있다. UCSD, UC Irvine, University of

Toronto 등에서 최근 Si CMOS 및 SiGe HBT 공정에 기반을 둔 주목할만한 결과들이 나오고 있다 [7-9]. 그러나 이들은 대부분 아직까지 94GHz 응용에 초점을 맞추고 있어 테라헤르츠 이미징에 주제를 국한하는 본 고에서는 더는 자세히 다루지 않도록 하겠다.

### 맺는말

이상으로 이미징 시스템에 대한 전반적인 개요 및 테라헤르츠 이미징의 다양한 접근 방식을 살펴보고, 특히 IDEC 의 독자들이 관심을 가질 반도체 기반 테라헤르츠 이미징 시스템 연구 개발 동향에 대해 간단히 정리해 보았다. 테라헤르츠 이미징은 근래 꾸준한 관심 및 연구의 대상이었으나 최근 몇 년간 반도체에 기반한 테라헤르츠 이미징에 대한 관심이 크게 증가하는 추세이다. 반도체 기반 기술은 여러가지 장점으로 상용화의 가능성이 매우 크기에 이러한 추세는 주목할만하다 할 수 있겠다. 국내에서도 이 분야의 원천 기술이 개발될 수 있는 환경이 조성되기를 바라며 글을 맺는다.

### Reference

- [1] J.-S. Rieh, S. Jeon, and a. M. Kim, "An Overview of Integrated THz Electronics for Communication Applications," presented at the IEEE International Midwest Symposium on Circuits and Systems, 2011.

- [2] R. Han, Y. Zhang, C. D., H. J., V. H., K. W., B. E., and K. K. O., "280-GHz schottky diode detector in 130-nm digital CMOS," in IEEE Custom Integrated Circuits Conference (CICC), 2010, pp. 1-4.

- [3] U. R. Pfeiffer and E. Ojefors, "A 600-GHz CMOS focal-plane array for terahertz imaging applications," in 34th European Solid-State Circuits Conference, 2008, pp. 110-113.

- [4] E. Ojefors and U. R. Pfeiffer, "A 650GHz SiGe receiver front-end for terahertz imaging arrays," in IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2010, pp. 430-431.

- [5] R. Al Hadi, H. Sherry, J. Grzyb, N. Baktash, Y. Zhao, E. 'Ojefors, A. Kaiser, A. Cathelin, and U. Pfeiffer, "A Broadband 0.6 to 1 THz CMOS Imaging Detector with an Integrated Lens," presented at the IEEE International Microwave Symposium, 2011.

- [6] A. Tang and M.-C. F. Chang, "Advantages of the CMOS Receiver for Millimeter and Sub-millimeter Wave Imaging," presented at the IEEE International Microwave Symposium Workshop, 2011.

- [7] J. W. May and G. M. Rebeiz, "Design and Characterization of W-Band SiGe RFICs for Passive Millimeter-Wave Imaging," IEEE Transactions on Microwave Theory and Techniques, vol. 58, pp. 1420-1430, 2010.

- [8] C.-C. Wang, Z. Chen, H.-C. Yao, and P. Heydari, "A Fully Integrated 96GHz 2×2 Focal-Plane Array with On-Chip Antenna," presented at the IEEE International Microwave Symposium, 2011,

- [9] A. Tomkins, P. Garcia, and S. P. Voinigescu, "A Passive W-Band Imaging Receiver in 65-nm Bulk CMOS," IEEE Journal of Solid-State Circuits, vol. 45, pp. 1981–1991, 2010.

미래의 지능형 SoC 시대를 대비하다

# 미래의 지능형 SoC 시대를 대비하다

한양대 지능형 차량용 SoC 플랫폼 센터 (IDEC Platform Center) 미국의 석유 시장 대부분을 지배했던 록펠러가 10년 일찍 또는 10년 늦게 석유 사업을 시작했다면 크게 성공하기 어려웠을 것이라는 이야기가 있습니다. 세계적인 기업 마이크로 소프트를 설립한 빌 게이츠, 그리고 애플을 설립한 스티브 잡스도 적절한 시기에 유망한 분야의 사업을 시작한 점이 성공의 주원인 중의 하나라고 볼 수 있을 것입니다. 미래에 중요한 기술을 적절한 시기에 개발하는 것은 중요한일입니다. System on Chip (SoC) 분야에서의 현재 큰 시장은 휴대폰, 디지털 TV 등입니다. 미래의 큰 시장으로는 자동차와 로봇 등이 다가오고 있습니다. 자동차는 현대인에게 필수적인 도구입니다. 교통은 일상생활에 매우 유용하지만, 점점 복잡해지고 위험해지면서해결해야할 문제도 증가하고 있습니다. 환경오염 문제, 에너지 문제, 교통사고 문제 등입니다. 센서와 제어부를 개선하면, 환경 에너지 문제를 크게 감소시킬 수 있습니다.

World Health Organization (WHO) 2004 보고서에 따르면, 2002년에 1백20만 명이 교통사고로 사망했고 (평균 매일 3,242명이 사망), 2천만에서 5천만 명이 교통사고로 다치거나 장애인이 된다고 합니다. 이러한 비극은 새로운 예방조치가 없다면 앞으로 20년에 걸쳐서 65% 증가할 것으로 예측하고 있습니다. 사람의 부주의나 실수에 의한 사고를 줄여야겠으나, 지능형 자동차가 사고 감소에 크게이비지할 것으로 예상합니다. 지능형 차량에서 주변의 차량 보행자장애물 등을 감지하여 운전자에게 정보를 제공하면 보행자 사고의 85%까지 감소 가능하다는 보고도 있습니다. 야간이나 기상 악화로시야가 제한될 때 운전자를 도와주는 기능, 나아가서는 자동 무인 운전의 상용화도 머지않아 가능할 것으로 보입니다. 이러한 기술은 자연스럽게 지능형 로봇 산업, 그리고 멀티미디어 등 여러 다른 산업분야에 사용 가능합니다.

한양대학교 에리카캠퍼스에 지식경제부, 정보통신산업진흥원, 반도체설계교육센터의 지원으로 2011년 6월 설립한 지능형 차량용 SoC 플랫폼 센터는 미래에 고성장이 예상되는 지능형 SoC 산업을 이끌어 갈우수 전문 인력을 양성하고, 플랫폼을 구축 보급하고, 산학연의 network를 형성하여, 다양한 정보 교류 및 협력의 중심이 될 것입니다.

인력양성을 위해서는 산업체와 협의하여 필요 분야를 파악하고 이에 적합한 교육과정과 교재 개발을 할 계획입니다. 지능형 SoC는 미래의 기술이기 때문에 적절한 교재의 개발도 필요합니다. 본 센터에서는 다음과 같은 5개의 새로운 융합 과목 교재를 개발하고 있습니다.

| 신규 융합 과목명    | 주요 내용                           |

|--------------|---------------------------------|

|              | 영상신호처리, 컴퓨터 비젼, 패턴인식영상 및        |

|              | 비전시스템 분야의 기본적인 이론과 실제 차         |

| 지도권 리카이되요 이런 | 량안전을 위한 영상 및 비젼 시스템에서 사         |

| 지능형 차량안전을 위한 | 용되는 다양한 알고리즘들을 배우고 이를           |

| 영상 및 비전시스템   | OpenCV 라이브러리를 이용하여 C 프로그        |

|              | 래밍으로 구현하는 실습을 통해 수강생들의          |

|              | 이해도를 높이도록 한다.                   |

|              | 본 과목에서는 SoC 설계 방법에 대한 소개        |

|              | 와 함께 하드웨어 설계, 소프트웨어 설계,         |

|              | Embedded Processor, Embedded OS |

| 시스템 설계 및     | 등의 시스템 반도체 설계 전반에 걸쳐 공부         |

| 근거리 통신용 SoC  | 한다. 또한 이동 중인 차량 간의 운전자 안전       |

| 설계 기법        | 정보 및 상업적 서비스를 제공하기 위한 무         |

|              | 선 전송기술로 채택된 IEEE 802.11p WAVE   |

|              | 모뎀 기술에 대해 공부하고 설계 실습을 수         |

|              | 행한다.                            |

| Core-A 기반<br>차량용 임베디드<br>시스템 | 차량용 임베디드 소프트웨어 플랫폼인 AUTOSAR 4.0의 구조, 차량용 임베디드 운영체제(OSEK, 차량용 임베디드 리눅스)의 개요 및 특징에 대하여 학습하고, Micro-Controller Abstraction Layer (MCAL) 및 Basic Software (BSW)의 작성에 대하여 실습한다. 전자식 dashboard 구현에 필요한AUTOSAR 응용소프트웨어(SWC) 구현을실습한다. |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 고신뢰성 자동차<br>전자시스템 설계기술       | 자동차의 다양한 계층적 네트워크에 연결된<br>시스템 IC의 고장을 효율적으로 점검하고 진<br>단할 수 있는 핵심기술을 소개한다. 자동차<br>전자 시스템의 신뢰성을 정의하고 MOST 등<br>네트워크를 살펴본 후 반도체 소자에서부터<br>시스템에 이르는 다양한 테스트 설계기술을<br>공부한다.                                                        |

| 차량용 센서 설계 및<br>응용            | 자동차 센서를 위한 기본적인 반도체 설계지식을 시작으로 하여, 차량 안전과 환경을 위한 각종 센서 설계 기술과 응용, 배기가스, 타이어 센서 등의 핵심 기술을 학습한다. 자동차와 같은 노이즈에 강하고 신뢰성이 높은회로 설계 기술이 필요한 시스템의 특성을이해하고, 설계 능력을 갖춘다.                                                                |

|                              | 이해야고, 설계 등덕들 것준다.                                                                                                                                                                                                             |

위의 교재들은 본 IPC 센터에서도 교육에 사용하고, 대학/대학원/산업체/연구소 등에서도 활용하도록 출판하여 제공할 예정입니다.

플랫폼 사업에서는 핵심적으로 필요한 기술 기반 (시스템, 소프트웨어, SoC 포함)을 구축하여 여러 산업체에 적합하게 최적화하여 제공하는 것을 목표로 합니다. 플랫폼 사업은 아직 성공적인 사업 모델도 정립되지 않았기 때문에, 잘 성장할 수 있는 생태계 및 business model도 창의적으로 만들어가야 합니다. 대학에서 개발한 연구 결과가 효과적으로 산업체에서 널리 쓰이기 위해서는 우선 다음 두 가지가 필요하다고 생각합니다.

첫째는 산업체와의 밀접한 정보교류입니다. 기획 단계에서부터 산업체 수요 파악, 자세한 사양 결정, 성능 및 cost 등 논의, 실험/응용에서의 현실적인 점검 등 지속적인 협의가 필요할 것입니다.

두 번째는 여러 연구실이 연합하여 synergy 효과를 내고 큰 규모의 플랫폼을 개발하는 것입니다. 본 IPC에서 구축 보급할 플랫폼은 다 음과 같이 세 그룹으로 나눌 수 있습니다.

| Platform명                         | 주요 내용                                                                                                                                                                                                                   |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 영상 및 통신정보를<br>활용한 차량 안전<br>운행 시스템 | · 영상 정보를 이용한 차량/보행자/장애물 인식 및 충돌방지 안전 운행 시스템 개발 - Blind Site Detection /Warning 기술 개발 · 물체 인식률을 높이기 위한 이미지 왜곡 보정 · Panoramic vision을 이용한 주변 물체 인식 · 실시간 물체 인식을 위한 회로 구조 개발 · 다양한 환경에서 차선, 차량, 보행자 인식 및 주변 환경 정보 취득 기술 개발 |

| Core-A 기반 차량용<br>임베디드 SW          | <ul> <li>Core-A 기반의 AUTOSAR 4.0 구현</li> <li>Core-A 기반의 차량용 실시간 운영체제 구현</li> <li>전자 통합 dashboard동 AUTOSAR용 응용 S/W 모듈 IP 개발</li> </ul>                                                                                    |

### IDEC | 기획칼럼

고신뢰성/친환경 자동차 시스템

- 이더넷 기반 인터넷을 통해 원격으로 자동차 전장시스템과 접속하는 system platform 개발

- IEEE 1149,X 경계스캔을 통해 고장 모듈을 제어/관측할 수 있는 표준화된 기술 개발

- 온라인 모니터링 가능한 Diagnostic Function Test (DFT) 기술로 고장을 실시간으로 모니터링하고, 자동 결함 검증/수리기술 개발

- 온도 변화 및 시스템 파워 변화에 강인한 Design For Reliability (DFR) 설계기법 개발

인력 양성과 플랫폼 구축 보급 모두 많은 정성과 노력이 필요한 중요 한 부분이지만 관련 산학연의 협력 네트워크의 구축도 이에 못지않 게 중요한 부분입니다. 현재 15개 대학에서 28분의 교수님과 31개 산업체/연구소가 본 IPC에 참여하고 있습니다. 그리고 IPC의 문은 항상 열려 있습니다. 관심 있는 교수님 또는 산업체에서는 추가로 참 여 가능합니다.

### 참여대학 (총 15개)

참여기업 (총 31개)

대학교 등

한양대학교, 건국 삼성전자, LG전자, 하이닉스, 동부하이텍, 전 대학교, 경북대학 자부품연구원 (KETI), 한국전자통신연구원 교, 군산대학교, 동 (ETRI), 자동차부품연구원 (KATECH), 현대 국대학교, 부산대 자동차 상용차개발센터, 광전자, 비스코, 오디 학교. 서울대학교. 텍 , 코아로직, 트란소노, 아날로그칩스, 대우 숭실대학교, 아주 전자부품, 타타대우상용차, ㈜HSL, ㈜KNJ, ㈜ 대학교. 연세대학 TLI, ㈜휴인스, Itronics, MDS Tech, Ima-교, 울산대학교, 인 genext, Radio Pulse, Nexus chips, CNS 하대학교, 전북대 Technology, 와이즈오토모티브, ㈜실리콘마 학교, 한국외국어 이터스, 아이브스테크놀러지, KETI-차세대자 대학교, 한국항공 동차전장센터, KETI-전북임베디드시스템연구 센터 등

지능형 SoC 사업의 활동은 다음 그림과 같이 나타낼 수 있습니다.

산학연 협력 네트워크 구축

- 산업체 요구에 맞는 전문 설계 인재 양성 처랑용 SoC 플랫폼 기술 공동 개발 및 활용에 대한 지원 강화 우수 연구 인력의 산업체와 인턴 프로그램 제공 및 취업지원

Platform 통합 platform

### 플랫폼 보급 및 확산

맞춤형 현장 방문교육 platform 개발 및 수행 정기적인 기술교류 및 workshop 개최 통한 연구 교류

지능형 SoC 분야의 시스템 설계, 소프트웨어 설계, 하드웨어 설계를 리드할 전문 인력 양성, 경쟁력 있는 기술 개발에 기초한 플랫폼 구 축. 플랫폼 보급 및 확산. 산학연 협력 네트워크 구축 등의 주요 사 업을 연계하여 유기적인 협력 체제로 키워나갈 계획입니다.

본 IPC는 고객 중심으로 운영하고자 합니다. 고객의 관점에서 본 IPC의 역할은 다음 표와 같이 정리할 수 있습니다.

### 고객 중심의 IPC요 내용

- 미래 기술 및 산업 비전 - 이해하기 쉬운 강의 1. 수강생 (학생) 고객 - 핵심 기술 정보 - 산업체 연계 (기술 교류, 취업 정보) - 우수 전문 인력 양성 공급 - 기술 정보 교류 2. 산업체/연구소 고객 - 플랫폼 제공 - 기술이전 산학협력 - 기술 정보 교류 - 연구 결과를 플랫폼으로 3. 교수 고객 보급 확산 - 산학연 network - 기술이전 산학협력

지능형 차량용 SoC 플랫폼 센터는 지능형 SoC가 널리 사용될 10 년. 20년, 30년 후에 우리 산업의 중요한 부분을 이끌고 나갈 리더 를 양성하고, 관련 분야 교육과정과 교재를 개발하고, 핵심 기술을 풀 랫폼으로 구축하여, 다양한 응용 분야에 최적화하여 효과적으로 사용 하도록 하며, 이 모두를 가능하게 할 산학연 협력 체제를 구축할 것 입니다.

한양대 지능형 차량용 SoC 플랫폼 센터 http://idec.hanyang.ac.kr)

소 : 경기도 안산시 상록구 사3동 한양대학교 에리카캠퍼스 3공학관 321호

C E O : 신현철 교수

shin@hanyang.ac.kr

행정팀 : 윤진은 행정원

jeyun@idec.hanyang.ac.kr 031-400-4079

IDEC Newsletter • 18 | 19

특허청과 반도체설계교육센터는 우수한 Core-A 프로세서 기반 기술을 발굴·포상함으로써 동 분야의 연구· 창작의 활성화와 Core-A 프로세서를 사용하는 반도체 설계 인력의 저번 확대를 통해 Core-A 프로세서의 활용 확산을 도모코자 다음과 같이 2011 Core-A 응용 경진대회를 개최합니다.

### 공모부문

1. Core-A 기반의 하드웨어 설계 2. Core-A 기반의 소프트웨어 설계

내국인으로서 반도체설계 관련 기업·연구소·대학의 개인 또는 팀 • 복수작 응모 및 단체 응모 가능

9.16.(금) 까지

응모양식(www.core-a.or.kr에서 다운로드)을 작성하여 세부 첨부파일과 함께 직접, 우편 또는 E-mail로 제출

• 반도체설계교육센터 주소

대전광역시 유성구 과학로 335 반도체설계교육센터(N26) (우편번호:305-701)

### • 이메일 주소 ejkim@idec.kaist.ac.kr

- 신청기간 2011.6.13(월) ~ 7.22(금)

- 출품작 제출 2011.10.4(화) ~ 10.21(금)

- 1차 평가 2011.10.24(월) ~ 11.4(금) • 2차 평가 및 시상식 2011 11 24(목)

- (본 일정은 주관 기관의 사정에 따라서 변경될 수 있습니다.)

### 시상내역

- 특허청장상(최우수상 1팀) 상금 300만원

- 우수상(1팀) 상금 200만원

- 장려상(3팀) 각 상금 100만원

반도체설계교육센터 (☎ 042-350-8533) 자세한 내용은 홈페이지 www.care-a.or.kr을 참조

### 기타사항

Core-A 보드 무상 임대 지원 호페이지(www core-a or kr)에서 응용보드신청서를 다운받아 제출

후원 다이나릿시스템, 실리콘마이터스, 실리콘웍스, 아이앤씨테크놀로지, 에이디칩스