IDEC Newsletter I 통권 제219호

● 발행일 2015년 08월31일 ● 발행인 박인철 ● 편집인 남병규 ● 제작 푸울디자인

● 기획 김하늘 ● 전화 042/350-8535 ● 팩스 042/350-8540 ● 홈페이지 http://idec.or.kr

● E-mail kimsky1230@idec.or.kr

● 발행처 반도체설계교육센터(DEC)

# newsletter

VOL. 219 September 2015

### MPW (Multi-Project Wafer) 2015년 MPW 진행 내역

- 6개 공정 16회 진행, 2015년 MPW 모집 마감

- 2016년 진행 일정은 11월 이후 공지 예정

- 2015년 MPW 진행 일정 및 진행 내역

| 공정        | 회차구분<br>(공정_년도순서) | 모집팀수<br>((mmxmm)x<br>칩수)/회별 | 정규모집<br>신청마강 | 참여팀수<br>((mmxmm)x칩수)         | DB 마감      | Die-out    | 비고             |

|-----------|-------------------|-----------------------------|--------------|------------------------------|------------|------------|----------------|

|           | S65-1501          | (4x4)<br>x48                | 2014.12.29   | (4x4)x 39                    | 2015.06.15 | 2015.12.14 | 제작중            |

| 삼성 65nm   | S65-1502          |                             | 2015.04.20   | (4x4)x 32                    | 2015.10.19 | 2016.04.19 | 설계중            |

|           | S65-1503          |                             | 2015.06.22   | (4x4)x 34                    | 2016.01.18 | 2016.07.18 | 설계중            |

|           | MS18-1501         | (3.8x3.8)<br>x25            | 2014.12.29   | (3.8x3.8)x17<br>(3.8x1.9)x16 | 2015.03.02 | 2015.08.03 | 제작완료           |

| MS 0.18um | MS18-1502         |                             | 2015.01.26   | (3.8x3.8)x20<br>(3.8x1.9x7   | 2015.05.11 | 2015.10.12 | package<br>제작중 |

|           | MS18-1503         |                             | 2015.02.23   | (3.8x3.8)x19<br>(3.8x1.9)x5  | 2015.07.13 | 2015.12.14 | 제작중            |

|           | MS18-1504         |                             | 2015.03.23   | (3.8x3.8)x22<br>(3.8x1.9)x6  | 2015.09.07 | 2016.02.01 | 설계중            |

|           | MS18-1505         |                             | 2015.05.26   | (3.8x3.8)x24<br>(3.8x1.9)x2  | 2015.12.18 | 2016,05,09 | 설계중            |

|           | MS35-1501         | (5x4)x20                    | 2015.01.26   | (5x4)x18<br>(5x2)x3          | 2015.06.08 | 2015.09.29 | 제작중            |

| MS 0.35um | MS35-1502         |                             | 2015.07.20   | 5x4)x19<br>(5x2)x2           | 2016.01.11 | 2016.04.30 | 제작대기중          |

| TJ SiGe   | TJS18-1501        | (2.35x2.35)x4               | 2014.12.29   | (2.35x2.35)x1                | 2015.04.27 | 2015.09.15 | 제작대기중          |

| TLOIC     | TJC18-1501        | (2.35x2,35)<br>x4           | 2015.01.26   | (2,35x2,35)x4                | 2015.06.15 | 2015.10.23 | 제작지연           |

| TJ CIS    | TJC18-1502        |                             | 2015.05.26   | (2.35x2.35)x4                | 2015.11.23 | 2016.03.28 | 설계중            |

| TJ BCD    | TJB18-1501        | (2.35x2.35)<br>x12~16       | 2014.12.29   | (5x2.5)x2<br>(2.35x2.35)x8   | 2015.03.02 | 2015.07.06 | 제작완료           |

|           | TJB18-1502        |                             | 2015.03.23   | (5x2.5)x1<br>(2,35x2.35)x8   | 2015.08.24 | 2015.12.28 | DB 검토중         |

|           | TJB18-1503        |                             | 2015.05.26   | (2.35x2.35)x9                | 2015.11.30 | 2016.04.04 | 설계중            |

\* 문의:이의숙 (042-350-4428, yslee@idec.or.kr)

- \* 일정은 사정에 따라 다소 변경될 수 있음.

- \* 회차 표기 방법 변경 : 공정코드-년도 모집순서 (예시) 삼성65nm 2015년 1회차 : S65-1501)

- \* TowerJazz 공정은 sub chip(2,35mm)(으로 분리하여 모집

- \* 모집기간 : 모집 마감일로 부터 2주전부터 접수

- \* Package 제작은 Die out 이후 1개월 소요됨

- \* 기준일 : 2015.08.24

#### ○ 2015년 8월 교육프로그램 안내

수강을 원하는 분은 IDEC 홈페이지(www.idec.or.kr)를 방문하여 신청하시기 바랍니다.

#### KAIST 개설 강좌 안내

|  | 센터명 | 강의일자         | 강의제목                                            | 분류     |

|--|-----|--------------|-------------------------------------------------|--------|

|  |     | 8월 31일-9월 3일 | Mixed Analog Layout (2차)                        | 설계강좌   |

|  |     | 9월 7-10일     | [IDEC 연구원 교육]IDEC MPW 설계를 위한 교육                 | 설계강좌   |

|  | 본센터 | 9월 11일       | 고속 인터커넥트 설계를 위한 Signal Integrity<br>이론 및 등화기 이론 | 설계강좌   |

|  |     | 9월 14-16일    | Design Compiler 사용법 및 활용예                       | Tool강좌 |

|  |     | 9월 17-18일    | Calibre xRC                                     | 설계강좌   |

|  |     | 9월 21-23일    | PrimeTime 사용법 및 활용예                             | Tool강좌 |

|  | 충북대 | 9월 12일       | OpenCL 프로그래밍                                    | 설계강좌   |

|  |     |              |                                                 |        |

• 강좌일 : 8월 31일-9월 3일

• 강좌 제목 : Mixed Analog Layout (2차)

• 강사 : 박의근 이사 (㈜ 파인스)

강좌개요 LAYOUT 수행을 위한 기초 학습 및 연계성 인식 IC 특성 저해 요인 고찰 및 특성 향상을 위한 방안 고찰.

LAYOUT 실습을 통해 학습 내용을 적용.

수강대상 수강 신청자 ( 아래의 사전지식 및 선수과목 참조 요망 )

**강의수준** 중급 강의형태 이론+실습

사전지식, 선수과목

Mixed Analog Circuit 의 간단한 동작 특성 해석 가능 (필수) Virtuso Layout Editor이용 작업 가능 및 실무 경험 (필수) Calibre Verification Too 사용 및 검증 가능 ( 필수 )

• 강좌일 : 9월 7-10일

• 강좌 제목: TFT-LCD 구동 기술의 이해 및 구동 회로 설계

• 강사 : 최병덕 교수 (한양대학교)

강좌개요 TFT-LCD data driver IC의 설계는 기본적으로 디지털 회로 및 아 날로그 회로 설계 지식을 바탕으로 하지만 이에 못지 않게 TFT-LCD system및 구동 기술에 대한 이해도 중요하다. 따라서, 본 강의에서는 구동 기술과 구동 회 로 설계에 대한 내용을 함께 강의한다.

수강대상 전자공학 전공 대학원생 또는 해당 산업체 근무자 **강의수준** 중급

**강의형태** 이론

사전지식, 선수과목

회로이론, 전자회로, 디지털 논리설계, 전자기학

• 강좌일 : 6월 5일

• 강좌 제목 : [IDEC 연구원 교육]IDEC MPW 설계를 위한 교육

• 강사 : 김연태 연구원, 선혜승 연구원 (IDEC)

강좌개요 디지털 설계자들을 위한 IDEC MPW 진행 방식을 소개하고 설계부 터 레이아웃. 검증 과정까지 실재 설계과정과 동일한 FLOW 로 교육과 실습을 진행합니다

수강대상 대학원, 회사원

**강의수준** 중급

**강의형태** 이론+실습

사전지식, 선수과목

디지털 논리회로, Verilog Language

• 강좌일 : 9월 11일

• 강좌 제목: 고속 인터커넥트 설계를 위한 Signal Integrity이론 및 등화기 이론

• 강사 : 김병섭 교수 (포항공과대학교)

강좌개요 본 강의에서는 고속 컴퓨팅 시스템에서 사용되는 고속 인터페이스 회 로설계에 필요한 이론적인 배경을 설명합니다. 전반부에서는 인터커넥트의 종류 와 트랜드를 설명합니다. 후반부에서는 인터페이스회로 구성에 필요한 수학적인 모델을 설명한 뒤. 설명한 이론을 바탕으로 대표적인 고속 인터페이스 회로에 대 해서 설명합니다.

**수강대상** 대학교 4학년생, 대학원생 및 직장인

**강의수준** 중급 **강의형태** 이론

사전지식, 선수과목

회로이론, 전자회로, 아날로그 회로 설계

• 강좌일 : 9월 14-16일

• 강좌 제목 : Design Compiler 사용법 및 활용예

• 강사 : 신용승 차장 (Synopsys)

- This course covers the ASIC synthesis flow using Design Compiler Topographical / Graphical — from reading in an RTL design (Verilog and VHDL) to generating a final gate-level netlist. You will learn how to read in your design file(s), specify your libraries and physical data, constrain a complex design for timing and floorplan, apply synthesis techniques using Ultra, compile to achieve timing closure and an acceptable congestion, analyze the synthesis results for timing and congestion, and generate output data that works with downstream layout tools.

- · You will verify the logic equivalence of synthesis transformations (such as Datapath optimizations and Register Retiming) to that of an RTL design using Formality. The course includes labs to reinforce and practice key topics discussed in lecture. All the covered commands and flows are printed separately in a 5-page Job Aid, which you can refer to back at work,

수강대상 ASIC digital designers who are going to use Design Compiler, to synthesize Verilog or VHDL RTL designs to generate gate-level netlists enabling timing closure

**강의수준** 초급

VOL. 219 September 2015

#### ○ 2015년 9월 교육프로그램 안내

강의형태 이론

사전지식, 선수과목

- 1. Basic digital logic design concepts and terminology, including:

- RTL, gates, netlist, boolean/combinational/sequential logic, pipelines, data path, scan chains, buffering

- Register-to-register timing: Setup and hold

- Clock network: Skew, insertion delay or latency

- Design hierarch

- Effects of interconnect parasitics and PVT on timing

- 2 LINIX and X-Windows

- 3. A Unix text editor, for example: emacs, vi, pine

• 강좌일 : 9월 17-18일

- 강좌 제목 : Calibre xRC

- 강사 : 한정무 과장 (한국멘토그래픽스)

강좌개요 본 교육은 Calibre xRC를 사용하여 Layout상의Parasitic 저항 및 캐패시터를 추출하는 방법 및 Rule file generation에 대하여 교육을 합니다. Calibre xRC의 다양한 기능적인 부분에 대하여 실습과 병행하여 교육 합니다.

수강대상 Calibre xRC User

**강의수준** 초급

**강의형태** 이론+실습

사전지식, 선수과목 Calibre nmDRC/nmLVS에 대한 경험이 필요하나, 기본적인 내용이 포함되어 있어 처음 Tool을 사용하시는 분도 가능

• 강좌일 : 9월 21-23일

• 강좌 제목 : Calibre xRC

• 강사 : 최병덕 교수 (한양대학교)

강좌개요 TFT-LCD data driver IC의 설계는, 기본적으로 디지털 회로 및 아날로그 회로 설계 지식을 바탕으로 하지만, 이에 못지 않게 TFT-LCD system및 구동 기술에 대한 이해도 중요하다. 따라서, 본 강의에서는 구동 기술과 구동 회로 설계에 대한 내용을 하게 가이하다

**수강대상** 전자공학 전공 대학원생 또는 해당 산업체 근무자

**강의수준** 중급

**강의형태** 이론

사전지식, 선수과목 회로이론, 전자회로, 디지털 논리설계, 전자기학

\*문의: KAIST IDEC 이한나 (042-350-8536, Ihn1224@idec.or.kr)

• 강좌일 : 9월 12일

• 강좌 제목 : OpenCL 프로그래밍 • 강사 : 류관희 교수 (충북대학교)

강좌개요 병렬처리 프로그래밍인 OpenCL(Open Computing Language)의 기능을 공부하고, 예제를 통한 실습 교육을 통해 실무적용 능력을 배양한다.

수강대상 학부생 및 대학원생, 관련기업 임직원

강의수준 초급 강의형태 이론+실습

\*문의: 충북대 IDEC 라해미 (043-261-3572, idec@chungbuk.ac.kr)

ω/

# 1DEC SoC Congress

일시: 2015, 09,22(화) 09:30~19:00

장소: KAIST KI빌딩 1층

대학에 설계 연구 환경 지원에 대한 결과를 소개·전시하고 대학과 관계자 분들과 함께 SoC 설계 인력 양성의 현안과 발전 방향에 대해 논의하고자 IDEC SoC Congress(ISC)를 개최합니다. 본 행사를 통해 산업의 근간인 인력양성에 대한 의견를 수렴하여 더욱 나아진 연구 및 교육 환경이 구축될 수 있도록 관계자 여러분의 많은 관심과 참여 부탁 드립니다.

#### > 진행 프로그램

- 성과전시: MPW 설계 결과 전시(CDC)

- 최신 동향 세미나 : SoC 및 차량용 반도체의 기술 동향과 비전

- 포럼: SoC 전문인력양성의 확대를 위한 대학 교육 방향 논의

- IDEC 수행 사업 보고 및 관련 시상

#### > 진행 일정

| 구분          | Session1(강당,1F)                                                   | Session2 (로비,1F)              |  |

|-------------|-------------------------------------------------------------------|-------------------------------|--|

| 09:30~10:00 | Registration                                                      | 10:00 10:00                   |  |

| 10:00~10:30 | Opening<br>- 축사(강성모 총장 , KAIST)                                   | 10:00 ~ 16:00<br>[IDEC 성과 전시] |  |

| 10:30~11:50 | [최신 동향 세미나] 차량용 반도체의 기술 동향 및 비전<br>(Kent,chon 사장, ㄲ코리아)           | CDC참여팀<br>설계 우수팀              |  |

| 11:50~13:00 | 점심식사                                                              |                               |  |

| 13:00~14:20 | [최신 동향 세미나] SoC 산업의 기술동향과 비전<br>(이손석 부사장, 어보브반도체㈜)                |                               |  |

| 14:20~15:00 | Break Time_관람전시                                                   |                               |  |

| 15:00~15:30 | [사업내용 보고 및 시상]<br>- IDEC 사업 수행 내용 및 성과 발표<br>- CDC 우수팀 및 우수 강사 시상 |                               |  |

| 15:30~17:30 | [포럼]<br>- 참석: 대학-기업-정부<br>- 주제: SoC 인력양성을 위한 대학 교육 방향, IDEC 역할    |                               |  |

| 17:30~19:00 | 저녁식사(영빈관)                                                         |                               |  |

• 주 최:미래창조과학부, 산업통상자원부

● 주 관: 반도체설계교육센터(IDEC), KAIST

• 문의처: 042-350-4428, http://idec.or.kr, yslee@idec.or.kr

# 지능형 차량용 레이더 부품 개발 동향

#### 1. 서론

최근 차량 분야에서 차량의 구동, 제동 및 조향 등이 전자화 되면서 차량주행 중 주변 환경을 인식하여 운전자의 편의와 안전을 증진시키는 지능화 개발이 본격화되고 있다. 차량 사고를 미연에 방지할 수 있는 각종 첨단 전기 전자 통신 제어 기술을 차량에 적용하여 운전자의 주행 안전성, 편의성 및 주행 효율성을 극대화시킨 지능형 차량 (ASV, Advanced Safety Vehicle, 첨단안전 차량)에 충돌 방지 레이더 시스템을 탑재하는 실정이다. 전후방 차간거리 감지 레이더로 앞차와 뒷차의 거리를 감지하여 충돌할 가 능성이 생길 경우 이를 운전자에게 알려주는 차량 충돌 경보 시스템에 대한 연구가 국내외적으로 상당히 활발히 진행 중이다.

이러한 레이더 센서에는 대략 30m 이내의 물체의 거리 및 움직이는 물체의 속도 등을 감지하기 위한 측후방 추돌 방지 단거리 레이더 (SRR, Short Range Radar)와 대략 150m까지 물체를 감지하기 위한 전방 충돌 방지 장거리 레이더 (LRR, Long Range Radar)가 있다. 특히 77GHz 주파수를 이용한 차량 레이더 시스템은 차세대 안전 장비 중에서 가장 핵심적인 시스템이며, 미래 차량 안전 산업 기술에 있어서 필수적이라 할 수 있다. 본고에서는 이러한 차량용 레이더 부품 기술의 소개와 최신 연구 개발 동향 및 앞으로의 전망을 예측하고자 한다.

#### 2. 차량용 레이더 부품 기술 개요

#### 2.1. 레이더 동작 원리

차량 안전 시스템은 지능형 교통시스템을 구현하기 위한 필수 기술로서 열악한 기상조건 또는 부주의로 인해 발생 가능한 사고를 미연에 방지할 목적으로 개발된 차량의 안전 운행 시스템이다. 최근 차량 안전 시스템의 핵심 부품인 차량용 레이더 센서는 순항제 어, 긴급제동 등에 적용되는 핵심기술이며, 향후 교차로 차량감지 및 보행자 감지가 가능한 안전수준을 위해 수 cm급 고해상도 레이더의 개발이 요구되고 있다. 또한 차량용 레이더는 다양한 차량 충돌방지 시스템의 응용분야에 적용 가능하며 각각의 응용분야 별로 다양한 탐지 거리, 거리 해상도, 탐지 각도 등이 요구되지만, 단일 레이더로 이러한 성능을 동시에 만족시키기는 매우 어렵다. 따라서 그림 1과 같이 장거리 레이더 (LRR)와 단거리 레이더 (SRR)를 조합하여 차량 안전 시스템의 개발이 진행되고 있다.

차량용 레이더는 송신기에서 안테나를 통해 방사된 전자파가 표적에 의해 반사되어 돌아오는 수신신호를 측정한다 [1].

레이더 방정식이라 부르는 수신신호의 전력 Pr은 식 (1)과 같이 나타낸다. 수신신호의 송신신호에 대한 지연시간 △t를 측정함으로써 표적까지의 거리를 식 (2)와 같이 구할 수 있다. 또한 점차 멀어지는 표적에 의해 반사된 신호는 송신 주파수에 비해 주파수가 낮아지고, 점차 다가오는 물체는 주파수가 높아지는 도플러 주파수편이 현상을 이용하여 표적의 상대속도를 식 (3)과 같이 측정할 수 있다 [1]. 여기에서 √는 전파의 이동속도이며, fa는 도플러 주파수편이, fc는 송신신호의 중심 주파수를 각각 나타낸다.

레이더의 동작 방식은 송신신호의 파형에 따라 크게 펄스 레이더 (Pulse Radar)와 연속파 레이더 (Continuous Wave Radar)로 구분 할수 있다. 펄스 레이더는 레이더의 송수신에 펄스 신호를 이용하는 방식으로 펄스폭이 작아질수록 우수한 거리 분해능을 얻을 수 있다. 연속파 레이더는 송신신호가 시간에 대해 끊김 없이 연속적으로 출력되며 동시에 수신이 이루어지는 방식이다. 차량용으로는 속도와 더불어 거리를 측정해야 하므로 FMCW (Frequency -Modulated Continuous Wave) 변조 방식이 주로 사용되고 있다.

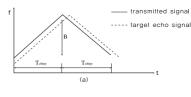

그림 2는 FMCW 레이더 신호 검지 원리를 나타낸 것이다. FMCW 레이더는 시간에 따라 선형적으로 주파수가 변조된 연속파를 송신하여, 전방 차량과의 거리, 상대속도 등을 추정한다 [1]. 물체로부터 반사된 수신신호와 송신신호를 서로 곱하여 주파수의 합 성분은 버리고 차 성분을 구하게 되는데 이것이 비트 (beat) 신호이다. 비트 신호의 주파수 fb는 | fTX-fRX | 이며, Up-chirp (주파수가 선형적으로 증가하는 구간)에 의한 비트 주파수를 fb-, Down-chirp (주파수가 선형적으로 감소하는 구간)에 의한 비트 주파수를 fb-라 한다.

▲ 여기서, Pr: 수신신호 전력, Pt: 송신신호 전력,

Gt: 수신안테나 이득, Gr: 송신안테나 이득,

σ: 레이더 유효 단면적, λ: 자유공간상의 신호의 파장,

R: 표적까지의 거리, Ls: 레이더시스템 손실

그림 2. FMCW 레이더 신호 검지 원리

#### 2.2. 기타 레이더 신호 처리 기술

레이더 신호처리란 레이더의 수신신호에서 원하는 정보를 얻기 위한 다양한 알고리즘을 적용하는 과정을 말한다. 차량용 레이더는 거리와 상대속도 추정과 더불어 수평방향의 도래각 (DOA, Direction of Arrival) 추정이 동시에 구현되어 반사체의 위치를 좀 더 정밀하게 탐지할 수 있다. 즉 차량용 레이더에서는 신호처리를 통하여 표적의 거리, 상대속도, 도래각 정보를 추출한다. 도래각 추정 방식에는 빔스캔, 모노펄스 방식, 디지털 빔포밍 방식 등이 존재하나 최근에는 고해상도의 도래각 추정 알고리즘의 요구에 맞추어 디지털 빔포밍 방식이 주로 차량에 구현되고 있다 [1]. 또한 최근 차량용으로 가장 많이 사용되고 있는 것은 MUSIC 알고리즘으로, 이는 고유치 분해 (Eigen Value Decomposition)를 통해 타깃 신호 부공간의 고유 벡터와 잡음 부공간의 고유 벡터를 분리하여 생성함으로써 타깃 신호에 대한 DOA를 추정하는 방법이다 [1]. 신호처리 결과로 추정된 거리, 모든 사람들은 작업된 기리, 조건경에 대한 다음 경점 기리, 모든 사람들은 보임 기리, 조건경에 대한 다음 기리를 들었다.

신호처리 결과로 측정된 거리, 속도, 각도 정보는 잡음 성분을 포함하므로 오인식 결과를 초래하기도 한다. 측정 정보에 대한 잡음 제거 및 그 신뢰도를 높이기 위하여 과거 측정값에 대해 트랙 정보에 기반한 타깃 추적 과정이 필수적으로 요구되고 있다.

#### 3. 차량용 레이더 부품 개발 동향

본고에서는 차량용 레이더 부품에 대해 최신 국내 연구개발 동향에 대해 살펴보고자 한다.

(개발 예1)

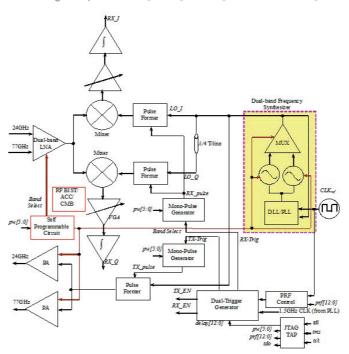

2012년 한국전자통신연구원은 CMOS 다중 레이더 센서 기반 차량 안전 시스템을 개발하였다 [그림 3 참조]. CMOS 기반 다중 레이더 센서 플랫폼을 기반으로 하여 차량안전시스템에 적용한 것으로 이러한 시스템은 안테나, CMOS로 구현한 레이더-온-칩 (RoC, Radar on a Chip) 및 다중 레이더 신호처리를 위한 DSP로 구성되어 있다. DSP를 통해 처리된 신호는 CAN 등 통신 프로토콜로 자동차의 ECU에 전달되어 설계된 여러 가지 응용으로 활용된다.

$$f_{b+} = \frac{2RB}{cT_{chip}} - f_{d}$$

(4)

$$f_{b-} = \frac{2RB}{cT_{chip}} + f_{d}$$

(5)

$$f_{\rm d} = \frac{2v}{\lambda}$$

(

$$R = \frac{(f_{b+} + f_{b-}) c T_{chip}}{4RR}$$

(7)

$$V = \frac{(f_{b+} + f_{b-}) cT_{chip}}{4} \lambda \qquad (8)$$

▲ 여기서, fb+, fb-: 순시 캐리어 (carrier) 주파수, R: 물체 간 거리, B: 시스템 대역 폭, c: 광속, Tchirp: chirp 지속 (duration) 시간, fd: 이동 물체에 의한 Doppler 주파수, V: 위상 속도, λ: 캐리어 신호 파장 대형 승용차의 차량안전시스

템으로는 Smart Cruise Control

(SCC), Stop & Go, Pre Crash System

(PCS), Blind Spot Detection (BSD), Lane Change

Assist (LCA) 등을 들 수 있다. 차량용 안전 시스템 중 [2]에

서 제안한 "다중 센서 기반 자동차 레이더 시스템"은 근거리용 레이

더 (SRR)와 장거리용 레이더 (LRR)를 통합하여, 77GHz 대역에서 동작하는 단

일형 멀티모드 레이더 센서 시스템이다. 넓은 방위각 범위를 갖는 SRR과 좁은 안테나

빔 폭의 고출력이 필요한 LRR이 동시 지원 가능하기 때문에 저속 근거리 구간 제어 기능, 차

간 거리 제어 시스템 (Traffic Jam Assist System) 기능, 충돌 위험 순간 감지 기능, 브레이크 보조 또

는 자동 브레이킹을 통한 충격 완화 시스템 (Collision Damage Mitigation System) 기능, 고속 장거리 구간

감지 기능, 차간 거리 제어시스템 (Adaptive Cruise Control Stop & Go) 기능, 전방차량과 충돌 시간 예측 기능 및

경고하는 시스템의 인터페이스 기능 등을 포함하고 있다. 특히 차세대 다기능 77GHz 레이더 시스템을 위한 핵심 센서

인 77GHz 레이더 센서는 전방감지용 밀리미터파 대역 안테나 및 고주파 트랜시버 하드웨어, 중장거리 감지를 위한 감

지 소프트웨어, 잡음이 많은 도로 환경에서 멀티 타깃 감지 성능 확보를 위한 트래킹 소프트웨어 및 이와 관련한 인터페

#### (개발 예2)

이스 기능 블록 등으로 구성되어 있다.

차량 안전 시스템과 관련한 중

만도는 국내 최초로 2014년 77GHz 차량용 전방 충돌 방지 레이더 센서 개발을 국산화하는데 성공했다 [3]. 지난 2008 년부터 독자 개발에 착수하여 6년에 걸친 연구개발 끝에 차량용 충돌 방지 레이더의 하드웨어 및 물체 감지 신호처리 원천 기술을 확보해 상용화에 성공했다. 이러한 제품은 2014년 말 국내 출시되는 완성차의 스마트 크루즈 컨트롤 (SCC) 시스템에 장착되었다.

개발된 이러한 센서는 전방 차량 또는 보행자와의 충돌 시점을 사전에 예측하여 운전자에게 경보해주거나 긴급자동제동 명령을 수행해 사고를 원천 예방하는 최첨단 지능형 안전 시스템이다. 야간 및 악천후, 운전자의 부주의 등 예상하지 못 한 돌발 상황 발생 시 레이더의 77GHz 대역 전자파 송수신 회로 제어와 물체 감지 신호처리 기술을 이용한다.

이번에 만도가 개발한 센서는 그 동안 해외 업체에 의존해 오던 차량용 레이더 기술을 국산화하고, 향후 자율주행 자동차 개발의 초석이 되는 핵심 기술을 확보했다는데 의미를 둘 수 있다. 이와 함께, 만도는 2018년 이후 전방 물체 감지외에 전측방 및 후측방 물체 감지까지 가능한 전방위 충돌 방지용 및 보급형 초소형 레이더 상용화를 추진 중에 있다. 또한 향후 완성차에 의무 장착 예정인 긴급 자동 제어 (AEB, Autonomous Emergency Braking) 기능이 포함된 저가형충돌 방지 레이더 센서 시스템뿐만 아니라 다양한 차종에 적용될 것으로 기대하고 있다.

#### (개발 예3)

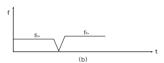

그림 4는 본 연구에서 개발 중인 지능형 자동차 레이더용 이중 대역 24GHz/T7GHz CMOS 시스템-온-칩 블록 다이어 그램을 나타낸 것이다. 본 연구에서는 5년간의 연구기간을 통해 저가 저전력 CMOS 공정을 이용하여 하나의 칩 안에 24GHz 측후방 감시용 단거리 레이더와 77GHz 충돌 방지용 전방 감시 장거리 레이더를 구현하고자 한다. TSMC 0.13 µm mixed signal/RF CMOS 공정 (ft/fmax = 120/140GHz)을 사용할 계획이다. 본 연구에서 개발 중인 이중 대역 차량 레이더 시스템-온-칩은 그림 4와 같이 직접 변환 (direct-conversion) 펼스형 레이더 구조를 가진다. 주파수 합 성기, 펄스 발생기 및 down-conversion chain이 24GHz와 77GHz 두 주파수 대역을 공유하도록 설계되어 있다.

그림 4에서 레이더는 펄스 반복 주파수 (pulse repetition frequency, prf)에 의해 정해진 율로 RF 펄스를 전송한다. 전방에 물체가 존재할 때 반사된 펄스와 전송된 펄스의 지연 성분 을 상관관계 연산을 통해 수신부에서 검출하도록 시스템을 구성하였다. 레이더가 0.15에서 40m의 넓은 범위에 걸쳐 목표물을 감지하고, 펄스 전송과 수신부 상호관계 연산 동작 간에 넓은 튜닝 지연 시간을 가지도록 CMOS 기저대역 펄스 발생기를 설계하였다. 또한 더 긴 거리 판단과 더 높은 거리 해상도를 향상시키기 위해 가변 prf와 펄스 폭이 혼합되도록 회로가 구성되어 있다. 온 칩 JTAG 인터페이스 회로는 펄스 발생기의 제어 비트를 입력하기 위해 사용한다.

개발 중인 레이더는 다음과 같은 기술을 포함하고 있다. • 저가 저전력 CMOS 공정을 이용하여 하나의 칩 안에 24GHz 측후방 감시용 단거리 레이더와 77GHz 충돌 방지용 전방 감시 장거리 레이더를 구현

- 시스템-온-칩화를 통해 칩의 저가격화, 초소형화, 경량화를 달성

- •최초로 Self 프로그램 가능한 회로 기술 적용: 주위 상황을 자동으로 인식하여 24GHz 레이더 또는 77GHz 레이더를 자동적으로 선택할 수 있도록 프로그램 회로 내장

- 최초로 BIST (Built-In Self-Test) 회로 내장 기술 적용: Core 칩 내에 S 파라미터, 이득, 잡음지수 및 third-order input intercept point (IIP3) 등을 자동으로 측정할 수 있는 회로 내장

- ACC (Automatic Compensation Circuit, 자동보상회로) 내장 기술 적용: 레이더 시스템의 오동작을 검출하여 정상동작 하도록 자동적으로 보상할 수 있는 회로 내장

- CMB (Capacitor Mirror Bank) 내장 기술 적용: 시스템-온-칩 제작 과정에서 흔히 발생하는 공정/ 전압/온도 (PVT, process/voltage/temperature) 변동을 자동으로 보정할 수 있는 회로 내장

▲ 그림 4. 본 연구에서 개발 중인 차량용 레이더 시스템-온-칩 블록 다이어그램

CNIOS Roc

CHIPTO LETT

FIFT

FAR

Velocity

extraction

Velocity

extraction

Forming

Waveform generator

Memory

ACC Stop & Go Bi

De

PARE < 60m. FoV: ±45°

Rydels < 200m. FoV: ±45°

Rydels < 200m

◀ 그림 3. 다중 센서 기반 차량 안전 시스템 개통도 [2]

#### 4. 결론 및 전망

본고에서는 차량용 레이더 개요, 레이더 동작 원리, 레이더 신호 처리 기술, 레이더 부품 개발 동향 등을 고찰하였다. 차량주행안전시스템으로서 초음파, 레이저, 카메라 등의 다양한 센서가 이용되어 왔지만, 차량용 레이더는 오염, 날씨 (우천/눈/안개) 등의 다양한 차량 주행 환경에서 가장 안정적인 성능 및 높은 가격 경쟁력을 가질 수 있을 뿐만 아니라 타깃의 거리, 각도, 속도 정보 등을 동시에 추출 가능하며, 상대적으로 먼 거리에 존재하는 타깃에 대해서도 상대적으로 안정적인 감지가 가능하다는 장점을 가진다. 또한 차량용 레이더 센서 제작에 있어서 CMOS 공정을 이용할 경우 기존의 레이더의 크기 및 가격을 획기적으로 개선할 수 있고, 현재 이용되고 있는 24GHz SRR과 77GHz LRR을 단일 센서로 통합할 수 있기 때문에 가격 문제로 인해 고급 차량에만 탑재되었던 차량 레이더 시스템을 일반 차량에도 탑재가 가능할 것으로 예상된다.

향후 국내에서도 SRR/LRR을 통합한 단일 송수신 칩 제작기술, 가변빔 안테나 기술, 이를 하나의 초소형 모듈로 실장하는 FEM 기술, SRR/LRR 통합 레이더에 적합한 고정밀/고속 레이더 신호처리 모듈 및 알 고리즘 기술 등의 꾸준한 개발을 통해 IT-자동차 강국의 면모를 보일 것으로 기대한다. 차량 레이더 센서 기술의 개발은 향후 미래 자동차 산업에서 꼭 필요한 기술이기 때문에 국가 차원에서 차량용 SoC 반도 체 분야를 특성화해서 관련 기술의 확보에 노력한다면 독자적인 우리 기술을 확보하리라 기대한다

류 지 열 교수 소속: 부경대학교 정보통신공학과

또 국 · 구 중에 목표 중포증권 중목되 주 연구분야 : System-on-chip, 고주파 회로설계, 임베디드 시스템 설계

E-mail: ryujy@pknu.ac.kr Homepage: http://myweb.pknu.ac.kr/org/user/ucsoc

성 명 우 박사과정 소속 : 부경대학교 정보통신공학과

주 연구분야 : System-on-chip, 임베디드 시스템 설계 E-mail : db6611@gmail.com

#### 참고문형

[1] 민경원, 손행선 "차량용 레이더 센서의 현황 및 연구개발 동향", 대한전자공학회지, 제40권 제6호, 2013년 6월.

[2] 박민, 박필재, 김동영, 김천수, 구본태, 정희범, 유현규, "77GHz 자동차 레이더 부품 기술동향" 전자통신동향분석, 제27권 제1호, 2012년 2월.

[3] 만도, 77GHz 車 충돌방지 레이더 센서 국산화, 전자신문, 2014년 11월 6일.

#### 1. Introduction

원자가 모여 물질을 만드는 과정과 만든 후의 모든 현상을 다루는 응집물질 물리학의 양자론적 연구는 20세기 초 이후에 발견된 다 수의 전도 관련 양자 현상, 즉 초전도 현상, 콘도 현상, 양자 홀효 과 등에 대한 성공적인 물리학적 해명을 통해 중흥기를 맞이했다. 특히, 양대 세계대전 중 첨단 과학기술의 선점이 생존과 직결되는 상황이 지속되면서 생존기술 차원에서 집중적인 지원을 받아 비약 적으로 발전한 과학기술은 고해상도 전자현미경 기술, X선과 중성 자선의 산란 및 광전자의 정밀 분석 기술 등 진보된 측정 기술을 낳았다. 또한, 트랜지스터와 집적회로의 발명으로 촉발된 전자공학 의 발달로 측정 제어기술이 고정밀화 되면서 이들 첨단 물성 측정 기술이 한층 고성능화되었다. 이로 인해 금속, 반도체, 절연체, 탄 소중합체 등 기존에 알려진 물질에서의 새로운 물리현상의 발견은 물론 각종 화합물 초전도체와 위상절연체등 새롭고 복잡한 물질에 대한 원자 규모에서의 양자론 수준의 이해가 가능해졌다. 또한, 첨 단 물성의 재료를 기반으로 하는 모든 종류의 산업에 걸쳐 이들 물 성 측정 기술의 활용도는 나날이 높아져 가고 있다.

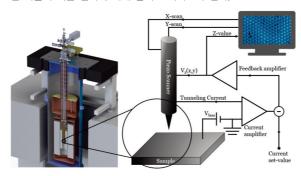

#### 2. Principles of Scanning Tunneling Microscopy

고해상도 전자현미경 기술 중의 하나인 주사 터널링 현미경은 1980 년대 초에 Binnig과 Rohrer에 의해 개발되었는데, [1] 그때까지 개 념적으로만 알려져 있던 원자의 존재를 대중에게까지 시각적으로 깊이 각인시켜준 최초의 기술로 잘 알려져 있다. 기본 구성은 그림 1 에서 볼 수 있다. 이 기술을 구현하기 위한 세부적인 물리적 원리 는 크게 양자 터널링 효과와 역압전 효과가 있으며, 전자 공학적인 핵심 기술에는 미소전류의 고속 측정 기술 및 네거티브 피드백 제 어 기술 등이 있다. 이 주사 터널링 현미경의 기본에서 출발하여 초 저온 기술, 초고자기장 기술, 초고진공 기술, 초미세 원자간력 측정 기술 등을 결합하여 첨단 물성 연구를 뒷받침할 수 있는 장비 개발 이 전 세계의 주요 대학 및 연구소를 위주로 활발히 진행되고 있 다. 그 중요성을 이해하기 위해 우선 각각의 물리 및 전자공학적 인 기술의 기본 원리에 대해 잠시 소개하고자 한다.

〈그림 1〉본 연구단의 초저온 고자기장 주사 터널링 현미경의 구조와 간략히 도식화된 제어 회로

#### 2.1. Quantum Tunneling Phenomenon

양자 터널링 현상은 그림 2와 같이 기본적으로 물질을 구성하는 원자의 전자가 발견될 확률 밀도 함수(파동함수)가 각 원자핵으로부터의 거리가 멀어짐에 따라 지수함수적으로 줄어드는 양자역학적인 원리로부터 설명된다. [2] 즉, 두 개의 도체가 구성 원자의 크기정도의 틈을 두고 떨어져 있을 때 한 도체의 전자가 다른 도체에서

발견될 확률, 다시 말해 두 도체 사이에 터널링 전류가 흐를 확률이 두 도체 사이의 틈의 크기에 대해 매우 민감하게 변화하는데, 도체의 일함수에 따라 다르지만 대략 매 0.1 nm 간격이 줄어들 때약 10 배의 비율로 전류의 크기가 커지는 현상을 보이게 된다. 따라서 편평한 시료와 뾰족한 탐침 사이의 간격을 원자 크기의 수 십분의 1 이내의 정밀도로 유지하기 위해서는 시료와 탐침 간 전압을 일정하게 주고, 그 사이의 양자 터널링 전류가 일정하게 흐르는 조건을 전자기계적으로 유지할 수 있어야 한다. 이 때 그 탐침을 표면상에서 2차원적으로 주사(scanning)할 경우 표면의 원자를 눈으로 볼 수 있는 주사 터널링 현미경이 완성된다.

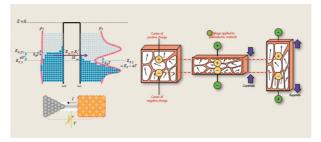

〈그림 2〉 양자 터널링 현상과 역압전 효과의 설명도. (a) 탐침의 전자 상태밀도가 균일할 경우 터널링 전류의 전압 미분으로 시료의 전자상 태밀도를 얻을 수 있다. (b) 결정 내 전하의 분극이 큰 압전체의 경우 가해진 전계에 비례하는 변위를 얻을 수 있어 전기기계적 제어소자로 활용된다.

#### 2.2. Inverse Piezoelectric Effect

이 전자기계적인 터널링 전류의 유지와 주사를 위해 초정밀 선형 모터로 활용되는 것이 압전체이며 이는 다음과 같은 역압전 효과로 동작한다. 우선 압전 효과란 어떤 물질에 특정 방향의 압력이 가해 졌을 때 그에 비례하는 특정 방향 전계가 내부에 발생하는 효과로 서, 주로 결정 격자 내부의 앙과 음의 전하 중심이 매우 비대칭적 인 물질(압전체)에서 그 효과가 크게 발생한다. 역압전 효과는 그 역의 효과 즉, 이와 같은 압전체에 외부의 전계를 가했을 때 그에 비례한 변형이 발생하는 효과로서, 대표적인 압전체인 PZT(lead zirconate titanate)는 상온에서 두께와 무관하게 1V 전압 인가에 대해 약 0.2 nm정도의 변위를 발생하는 물질이다. 이는 주사 터널 링 현미경의 제어를 위한 초정밀 선형 모터로 다양한 형태로 가공 되어 널리 활용되고 있다. 특히, 튜브형태로 가공되어 4분할 전극 을 형성한 튜브형 압전 스캐너는 매우 작고 단순한 일체형 구조로 3축 위치 제어가 가능한 이점으로 인해 원자를 볼 수 있는 초정밀 주사 터널링 현미경에 주로 사용되고 있다. [2]

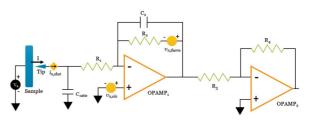

### 3. Design Considerations of Tunneling Current Amplifier for STM

주사 터널링 현미경에서 전압과 터널링 전류의 크기는 시료 및 탐침의 재질에 따라 다르나 표면의 원자를 열적 및 양자역학적으로 불안정하게 만들지 않는 1mV-1V 및 1 pA-1nA 수준에서 주로 설정하는데, 경우에 따라 표면의 원자를 조작하기 위해 이보다 큰 전압과 터널링 전류를 적극적으로 활용하기도 한다. 이처럼 1 pA 수준의 미세 터널링 전류를 전자기계적인 과정을 통해 정밀하게 제어하기 위해서는 저잡음 증폭회로 및 제어회로 설계의 다양한 노력이 요구된다. 우선적으로는 10<sup>9</sup>-10<sup>10</sup> V/A 수준의 전류—전압 변환

기를 제작해야 하는데, 대체로 FET 입력단을 가지는 고증폭도의 1 단 반전 연산증폭기 혹은 고증폭도와 저증폭도를 조합한 2단 반전 연산증폭기를 이용하여 제작되며 다양한 소스의 잡음 스펙트럼 분 포와 동작 주파수에 최적화하여 제작되어야 한다.

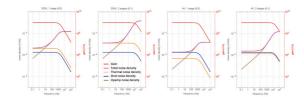

#### 3.1 Optimization of Noise Performance

예를 들어,  $10^9-10^{10}$  옴 가량의 높은 피드백 저항을 갖는 고증폭도의 반전 연산증폭기를 전류—전압 변환기로 사용할 경우 〈그림 3〉에서처럼 다음과 같은 잡음 소스들을 주로 고려하여야 한다.

〈그림 3〉 주사 터널링 현미경의 미세 전류 증폭 회로와 잡음 모델. 개별 전자 단위로 양자 터널링이 이루어짐으로써 발생하는 shot 잡음 과 큰 피드백 저항에 의한 열 잡음 그리고 연산증폭기의 입력 전압 잡음이 최종 출력의 잡음에 기여한다.

(1) 전자의 양자화 잡음 (shot noise): 시료와 탐침 사이에서 터널 링되는 전자가 단위 전하량을 가지고 터널링됨에 따른 백색 전류 잡음으로 √2ēA√로 주어진다.

(2) 피드백 저항의 열 잡음 (thermal noise, Johnson noise): 상 온 또는 유한한 온도에서 임의의 저항 양단에 발생하는 백색 전압 잡음으로  $\sqrt{4V_B} \mathrm{TR} A f}$ 로 주어진다. 이를 줄이기 위해 큰 피드백 저항을 낮은 온도에서 유지하는 것이 바람직하며, 초저온 연산증폭기의 필요성이 제기된다.

(3) 연산증폭기의 입력 전압 잡음 (input voltage noise of opamp): 연산증폭기 입력단에 차동으로 발생하는 전압 잡음으로  $1/f^a$ 형 잡음과 백색 잡음의 합으로 주어진다. 이 잡음의 실제 연산 증폭기 출력에의 효과는 주로 터널링이 일어나는 위치에서 증폭기 까지의 신호선과 그라운드 사이의 capacitance에 비례하여 그 정도가 강해지므로 연산증폭기의 위치를 실제 실험이 수행되는 위치에 가까이 가져갈 필요성이 제기된다.

#### 3.2. Optimization of Frequency Response

그리고 연산증폭기의 동작 주파수는 주로 높은 피드백 저항 R과 그에 병렬로 존재하는 shunt capacitance C (약 0.1pF)에 의해 RC 시정수로 결정되는 단일 pole 저주파 통과 필터의 cut-off 주파수로 결정된다. 이 RC 시정수를 줄이기 위해 2단계 연산증폭기 증폭기를 구성하여 1단의 증폭도를 예를 들어 10<sup>9</sup> 옴에서 10<sup>8</sup> 옴으로 1/10을 줄이고 2단의 증폭도를 10으로 할 경우 전체 cut-off 주파수는 10배 개선될 수 있다. 그러나 1단 증폭기의 피드백 저항의 열 잡음이 1단 출력에서 10배 감소하는 것 같지만 2단 출력에서 다시 10배로 증가하므로, shot 잡음과 연산증폭기 입력 잡음에 의한 출

력 잡음 수준이 열 잡음보다 작은 경우 최종 잡음이 전체적으로 크게 증가하는 결과를 얻게 된다. 따라서 그림 4에서 보이고 있듯, 주사 터널링 현미경을 위한 전류—전압 변환기는 낮은 잡음 수준이 매우 중요한 스펙트럼 측정 목적의 경우 1단으로 구성하되 입력 케이블의 capacitance를 가능한 줄이고 피드백 저항을 가능한 한 저온으로 유지하는 것이 가장 효과적일 수 있다. 변환기의 응답 속도가 중요한 고속 측정 응용의 경우 RC시정수를 줄이는 2단 구성을취하는 것이 바람직할 수 있으며, 이 경우에도 입력 capacitance의 감소와 피드백 저항의 저온화는 큰 잡음 성능 향상 효과를 줄수 있다.

〈그림 4〉 그림 3의 잡음 모델을 이용한 잡음 밀도 분포의 분석 결과. 상온과 초저온에서 각각 단일 증폭단( $10^9$  V/A)을 사용한 경우와 이중 증폭단( $10^8$ x10 V/A)을 사용한 경우를 가정하였다.

#### 3.3. Design of Cryogenic Operational Amplifier

액체 헬륨(대기압하의 기화온도 4.2 K)을 냉각원으로 하여 동작하 는 초저온 주사 터널링 현미경의 경우 연산증폭기와 피드백 저항을 모두 4.2 K에 가까운 저온으로 유지함으로써 위와 같은 장점들을 모두 도입하여 전체적으로 잡음을 1/10 수준으로 감소시킬 수 있 다. 그런데 고품질 산화막반도체 전계효과트랜지스터(MOSFET) 또 는 GaAs/GaN 화합물 기반의 금속-반도체 전계효과트랜지스터 (MESFET) 혹은 고전자이동도 트랜지스터(HEMT) 기술을 이용한 연산증폭기외에는 대체로 초저온에서 전자 또는 정공이 불순물에 포획되어 정상적인 반도체로서의 동작을 기대하기 어렵다. 본 연 구단에서는 위에서 열거된 기술들을 이용하여 초저온 주사 터널링 현미경에 필요한 수준의 입력 바이어스 전류, 증폭도, 입력전압 잡 음을 가지는 연산증폭기를 제작하기 위한 연구를 수행하고 있으 며, 그림5 및 그림6에 그 예를 보이고 있다. 1/10 수준의 잡음 감 소는 측정 시간의 1/100 감소와 통등한 효과인 만큼, 헬륨 용량과 소모율에 의해 제한된 시간 내에 10배 고품질의 측정 또는 100배 더 대량의 연관된 데이터 측정이 가능해지므로 초저온 주사 터널링 현미경은 물론 광전자 측정기, 질량 스펙트럼 분석기 등 초미세 전 류의 정밀 측정이 필요한 모든 첨단 장비에 큰 성능 개선을 가져올 수 있을 것으로 기대하고 있다.

〈그림 5〉(a) 고전자이동도 트랜지스터(HEMT)의 일반적인 구조.

(b) 상온에서의 일반적인 HEMT의 증폭 특성 및 저온에서의 양자효과로 인한 증폭 특성의 변화.

12 | 초저온 주사 터널링 현미경 연구를 위한 제어회로 개발 및 연산증폭기의 설계

〈그림 6〉본 연구단의 고전자이동도 트랜지스터(HEMT)를 이용한 단일칩 연산증폭기의 설계도(왼쪽) 및 증폭 단계별 개방회로 주파수 특성(오른쪽).

## 4. Research with Cryogenic High-Field Scanning Tunneling Microscope

본 연구단에서는 최근 그림 7과 같이 30톤급의 무진동 시설에 기초한 초저온 가변온도 고자기장 주사탐침 현미경 및 그 증폭 회로와 제어 회로를 자체 설계 제작하였다. 이를 이용하여 고온초전도체, 강상관계, 위상절연체 등 응용성이 뛰어나고 양자역학적인 새로운 물성이 발현되는 물질들을 위주로 온도와 자기장의 함수로고해상도의 원자 구조 측정 및 전자 스펙트럼 측정 연구를 수행하고있다. 특히 2차원 미세 그리드 상에서의 전자 스펙트럼 측정은 측정 표면의 2차원 전자의 밴드구조와 수명이 CDW/SDW 갭, Hybridization 갭, 초전도 갭 등에 의해 변하는 양상을 impurity에서의 산란 간섭에 의해 시각적으로 보여줄 수 있기 때문에 그 과학적인 가치가 크다. 그 세부적인 원리는 다소 복잡하나 기본적으로는전자의 터널링 스펙트럼이 표면의 2차원 전자의 다체계적 그린함수와 산란 포텐셜에 의해 다음과 같이 주어짐에 기인한다. [3]

$$\frac{d\delta I_{\alpha}(\mathbf{r}, V)}{dV} \sim -\frac{1}{\pi} \text{Im} \left[ \text{Tr}_{\sigma} \left[ \hat{\rho}_{\alpha} \delta \hat{G}_{\beta}(\mathbf{r}, \mathbf{r}, \omega = V) \right]_{11} \right]$$

$$\equiv \delta N_{\alpha\beta}(\mathbf{r}, \omega).$$

$\delta \hat{G}(\mathbf{r}, i\omega_n) = \hat{G}_0(\mathbf{r}, i\omega_n)\hat{t}(i\omega_n)\hat{G}_0(\mathbf{r}, i\omega_n).$

이 터널링 스펙트럼을 공간적으로 2차원 푸리에 변환하면 다음과 같이 다체계 그린함수에 포함된 운동량 공간에서의 밴드 구조를 deconvolution 과정을 통해 밝혀낼 수 있음을 알 수 있다.

〈그림 7〉본 연구단의 30톤급 무진동 시설 및 액체 헬륨 기반의 초저 온 고자기장 주사 터널링 현미경 및 증폭회로(오른쪽), 핵심 저온 측정 부(가운데) 및 네거디브 피드백 및 스캔 제어회로(왼쪽)

$$\begin{split} \delta N_{\alpha}(\mathbf{q},\omega) &= -\frac{1}{\pi} \mathrm{Im} \Big[ \hat{A}_{\alpha}(\mathbf{q},i\omega_n) \Big]_{i\omega_n \to \omega + i\delta}, \\ \hat{A}_{\alpha}(\mathbf{q},i\omega_n) &= \frac{1}{N} \sum_{\mathbf{k}} \mathrm{Tr}_{\sigma} \Big[ \hat{\rho}_{\alpha} \hat{G}(\mathbf{k},i\omega_n) \hat{t}(i\omega_n) \hat{G}(\mathbf{k}',i\omega_n) \Big]_{11}, \end{split}$$

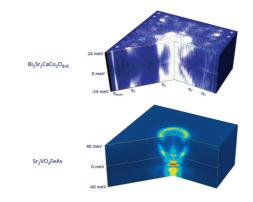

예를 들어, 초전도 FeAs 원자층과 Mott 절연체 VO3 원자층이 결합되어 있는 SrzVO3FeAs 물질에서 본 연구단의 제어회로를 이용해 고해상도 2차원 격자 터널링 스펙트럼을 얻을 경우 그림 8의 아래 그림과 같이 두 층간 전자 결합에 의해 밴드 구조가 크게 변화하고, 매우 질량이 큰 밴드와 질량이 작은 밴드가 새로이 생성되는 양상을 선명하게 볼 수 있다. 이 측정 기술 연구 결과는 코넬대학교의 선두 그룹에서 얻은 고온 초전도 물질인 BSCCO-2212 비교데이터에서 볼 수 있듯 기존 세계적인 그룹들이 가진 해상도의 한계를 뛰어넘는 것으로 한국 주도의 신물질 설계와 양자역학적 원리규명에 큰 기여를 할 수 있을 것으로 기대하고 있다. [4]

〈그림 8〉(a) 일반적인 초저온 주사 터널링 현미경으로 얻은 구리산화물계열 초전도체의 전자 스펙트럼. [4] (b) 본 연구단의 개선된 초저온 주사 터널링 현미경으로 얻은 철계열 초전도체의 전자 스펙트럼. [5]

#### 5. Conclusion

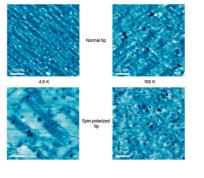

본 연구단에서는 지금까지 소개한 바와 같이 액체 헬륨 기반 가변 온도 고자장 주사탐침 현미경을 설계하고 저잡음 제어회로를 제작하여 연구에 활용하고 있다. 이 외에도 디지털 기술로 아날로그 증폭기의 응답 지연 효과를 실시간으로 개선하는 기술을 개발하고, 그림 9에서 보이고 있는 바와 같이 물질 표면의 스핀 구조 변화를 넓은 온도와 자기장의 함수로 원자수준 영상화가 가능한 기술을 세계 최초로 개발에 성공하였으며, 이를 활용하여 초전도 효과와 강상관 효과와 스핀궤도 효과가 복합적으로 나타나는 신물질 연구를 수행하고 있다. 본 연구 분야의 확대로 다양한 양자 신물질의 발견과 원리 규명 그리고 고도의 양자론적 설계에 기반한 양자 물질 합성과 응용이 가능한 날이 올 것으로 기대해 본다.

이 진 환 교수 소속 : 한국과학기술원 물리학과 주 연구분야 : 초저온 주사 탐침 현미경, 초저온 증폭 및 제어 회로의 설 계, 초전단체, 강상관계 및 위상철언체 연구, 마이크로파 대역의 초전도 공진기 연구 E-mail : jhinhwan@kaist.ac. kr Homepage: http://lispm.kaist.ac.kr/

정 진 오 박사과정 소속: 한국과학기술원 물리학과 주 연구분야: 초저운 주사 탐침 현미경, 초저운 중폭 회로의 설계, 고온 초천도 연구 및박막 증착 E-mail: jojo0333@kaist.ac.kr Homepage: http://ltspm.kaist.ac.kr/

최 석 환 막사과성

소속 : 한국과학기술원 물리학과

주 연구분야 : 초저온 주사 탐침 한미경, 초전도체 및 강상관계 연구

E-mail : j.choi@kaist, ac, kr

Homepage: http://lispm.kaist, ac, kr/

#### 〈참고 문헌〉

- 1. G. Binnig, H. Rohrer, Ch. Gerber, and E. Weibel, "Surface Studies by Scanning Tunneling Microscopy", Physical Review Letters 49, 57 (1982)

- 2. C. J. Chen "Introduction to Scanning Tunneling Microscopy," 2nd Ed., Oxford University Press (2007)

- 3. A. Akbari, P. Thalmeier, "Full t-matrix approach to quasiparticle interference in non-centrosymmetric superconductors", European Physical Journal B 86: 495 (2013)

- 4. J. Lee, K. Fujita, A. R. Schmidt, C.-K. Kim, H. Eisaki, S. Uchida, and J. C. Davis, "Spectroscopic Fingerprint of Phase-Incoherent Superconductivity in the Underdoped Bi2Sr<sub>2</sub>CaCu<sub>2</sub>O<sub>8+0</sub>", Science 325, 1099 (2009)

- 5. S. Choi, W. J. Jang, H. W. Choi, H. J. Lee, J. M. Ok, J. J. Yu, S. J. Kahng, J. S. Kim, Y. K. Semertzidis, J. Lee, "Variable temperature and magnetic field quasiparticle interference study in Sr<sub>2</sub>VO<sub>3</sub>FeAs", in preparation

- 6. S. Choi, W. J. Jang, H. W. Choi, H. J. Lee, J. M. Ok, Y. Kuk, H. S. Suh, J. S. Kim, Y. K. Semertzidis, J. Lee, "Variable temperature spin-polarized STM study revealing CDW and SDW phase transitions in Sr<sub>2</sub>VO<sub>3</sub>FeAs", in preparation

◀〈그림 9〉본 연구단에서의 세계 최초 가변온도 스핀감도 주사 터널링 현미경 측정의 예. 오른쪽 두 이미지와 같이 Neel 온도 위(160K)에서는 일반 탐침과 스 핀분극 탐침이 동일한 양상의 이미지를 주나 왼쪽 두 이미지와 같이 초저온(4.6 K)에서는 탐침의 스핀분극 여부에 따라 표면의 전하밀도파와 스핀밀도파로 나뉘 어 다르게 관찰된다. [6]

# Mentory Flovent & ICanalyst

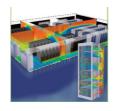

#### Mentor사 FloVENT

HVAC (Heating, Ventilation and Air Conditioning) Analysis Solution

모든 종류의 건물 내부 또는 주변의 유동 및 열전달, 오염물질 분포, 쾌적지 수 등의 예측용 CFD

#### C. Supported Platform and O/S System

- Windows XP Professional 32/64bit

- Windows Server 2003 & 2003 R2 (Standard and Enterprise) 32/64bit

- Windows Server 2008 & 2008 R2 (Standard and Enterprise)

- Windows Vista (Business, Enterprise and Ultimate) 32/64bit

- Windows 7 (Professional, Enterprise and Ultimate) 32/64bit

#### D. 특성 및 기능

- FloVENT의 빠르고 사용하기 쉬운 메뉴 시스템은 HVAC 설계 및 최 적화 업무를 수행하는 엔지니어들에게 특화되어 있다. FloVENT는 다 음과 같이 모든 형태와 크기의 건물에 적용할 수 있다.

- 아트리움, 쇼핑몰, 사무실, 극장, 공항터미널, 창고

- 통신 교환실 및 Data Center, 운송수단 내에서의 승객 편의도

- 연구소, 병원, 지하 주차장 내에서의 공기 오염도 분석 및 오염 물질 제어

유동 모델을 통해 설계자는 다양한 설계 옵션들을 최소한의 시간 내에 검토할 수 있다. 결국, 최종 설계를 직관으로 도출하는 것이 아니라 다양한 옵션들에 대한 전문적인 접근 방법으로 획득한 최적 안을 선택할 수 있다. 이를 통해 설 계 비용뿐 아니라 운용 비용을 단축하고 전체적인 시간을 줄일 수 있다.

FloVENT는 건물 내외의 유동을 모델링하기 위하여 기술적으로 가장 발전 된 지능형 모델 생성 매크로를 제공하고 있다. SmartParts를 이용하여 디퓨

저, 열교환기, 그릴, CRAC 유닛, Rack 등을 쉽고 빠르게 만들 수 있다. 이 모든 SmartParts는 Mentor Graphics Mechanical Analysis Division의 20년 이상의 노하우가 축적된 산물로 계산 시간은 최소화하고 결과의 정확 도는 높일 수 있도록 특화되어 있다.

FloVENT는 CAD 소프트웨어와의 연동 기능 역시 제공하고 있다. FloM-CAD Bridge를 사용하여 Pro/ENGINEER, Autodesk Inventor, Solidworks 등의 Native Data를 비롯하여 DXF를 포함한 다양한 중립 포맷의 MCAD Data를 불러오는 것이 가능하다.

FloVENT의 Grid는 가장 안정적이고 효율적인 Structured-Cartesian Method에 기반을 두고 있다. Localized Grid를 이용하여 필요한 곳에는 더 많은 Grid를 사용하면서도 계산시간을 단축시키고 전체적인 Mesh 품질 을 향상시킬 수 있다. FloVENT의 Grid는 SmartPart와 연결되어 있으며 모 델의 한 부분처럼 동작한다. 이 직관적인 Grid 방법은 사용자로 하여금 해석 그 자체보다는 설계에 더욱 더 집중할 수 있도록 해 준다. Mesh 작업에 많 은 시간과 경험이 필요한 다른 Tool들과 비교해 FloVENT의 Grid 작업은 즉 각적이고 쉽다. FloVENT는 모델이 변경될 때마다 다시 Grid를 할 필요가 없는 유일한 해석 Tool이다.

FloVENT만이 가진 고유한 "Automatic Optimization" 은 SmartPart 기 반의 모델과 Structured Cartesian Grid의 조합으로 인하여 가능한 최적화 기능이다. 실험계획법에 따라 설계 변수 (예를 들어 디퓨저의 풍량, 벤트의 위치 등)와 결과 (쾌적 지수, 오염 물질 제거 효율 등) 사이의 관계를 결정한 다. FloVENT의 실험 계획법은 최소한의 해석 수행으로 최적의 설계 변수의 조합을 찾아낼 수 있도록 도와주며, 반응표면법이나 Sequential Optimization Tool을 사용 할 수 있다.

20년 이상 FloVENT solver는 HVAC 분야에 특화되어 개발되어 왔다. Cartesian Gridding System에 기반을 둔 Solver는 가장 정확하며 빠르다. Localized Grid 및 Multi Grid 테크닉을 이용하여 가장 이른 시간 안에 정확

FloVENT의 Post Processor는 해석 결과를 분석하는 작업의 효율성을 최 대화시켜 준다. 랜더링 모델, 3D Flow Animation, 온도 및 유동장에 대한 동적 계량 등의 기능을 이용하여 문제가 되는 부분이나 설계 효과를 쉽고 빠 르게 시각화하여 확인할 수 있다. Texture Mapping이나 동영상 저장 등의 기능으로 기술자가 아닌 동료와의 협의도 가능하다.

FIOVENT를 사용할 수 없는 환경에서는 별도로 제공되는 모든 기능을 포함한 Post-Processor인 FloVIZ를 이용하여 결과를 공유하는 작업에 이용할 수 있다.

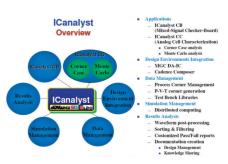

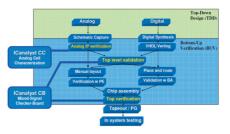

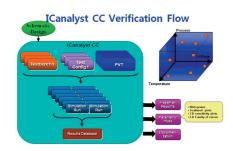

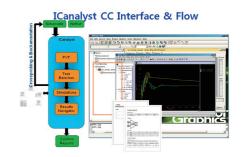

#### Mentor사 ICanalyst

#### **A.** 목적

DVACC (Design Verification and Analog Cell Characterization)

Mentor 사의 ICanalyst는 Circuit 검증을 위한 Test Bench에 Automation화 와 그 결과를 Graphic화 또는 Data화 줌으로써 효과적이고 쉬운 분석 가능

#### C. Supported Platform and O/S System

- RedHat 7.8.9

- Red Hat Enterprise (32/64bit) Linux 4.5.6

- •Linux SLES 10/11 (32/64bit) Linux

- Window 7/ Vista/ XP 32bit

#### D.특성 및 기능

#### 1. What is ICanalyst?

#### 2. ICanalyst Example for SoC Design

### **ICanalyst**

#### 3. ICanalyst CC Flow

#### 4. ICanalyst CC Flow

회사명: Mentor Graphics

웹 주소: http://www.mentorkr.com/

한국지사 : 한국멘토

전 화: 031) 8061-0790

주 소: 경기도 성남시 분당구 판교역로 192번길 12 (삼평동) 판교 미래에셋센터 7층

# 차세대 VLSI를 위한 광전자 집적회로 기술(3)

# 전자 및 광학소자 기술

3회에 걸쳐 차세대 VLSI를 위한 광전자 집적회로 기술에 관한 내용을 연재하고 있으며 반도체 기술의 발전과 차세대 배선 기술로서의 광학 배선 기술, 실리콘 기반의 광학 집적회로 구현을 위한 공정 및 물질 기술에 대하여 소개하였다. 금회의 마지막 기고에서는 광학 집적회로를 구성하는 전자 및 광학 소자의 요소 기술을 소개하고자 한다.

#### 1. 광학 배선을 구성하는 요소들

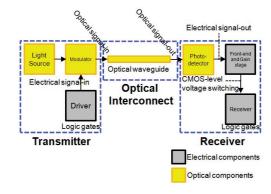

광학 배선은 금속을 기반으로 하는 기존의 전기적 배선(electrical interconnect)의 문제점을 해결하기 위해 제시되는 차세대 배선 기술임을 살펴보았다. 그러나 단순히 금속 배선(metallic wire)를 광도파로(optical waveguide)로 대체한다고 해서 해결되는 것은 아니며, 전기 및 광학 신호 간의 변환을 담당하는 요소들이 기술 개발의 대상으로 함께 포함되어야 한다. 즉, 이들을 모두 광학 배선을 구성하는 요소로 이해할 수 있다. 다음의 그림 1은 광학 배선의 모식도를 보여주고 있는데, 광원(light source), 광변조기(optical modulator), 광도파로(optical waveguide), 광검출기 (photodetector) 등이 모두 이러한 광학 배선 요소에 해당한다.

그림 1. 광학 배선의 모식도. (노란색: 광학 배선 요소, 회색: 논리연산 을 위한 CMOS 회로 요소)

광학 배선의 요소들은 이미 개별적으로는 높은 기술 수준으로 개발이 되어 있다. 앞의 기고에서 살펴본 바와 같이 보드 간 연결 (board-to-board interconnect) 기술은 이미 상용화, 칩 간 연결(chip-to-chip interconnect) 기술도 개발이 이루어진 상태이나 '차세대 VLSI를 위한 광전자 집적회로'를 실현하기 위해서는 광학 소자들이 광신호의 송수신 뿐만 아니라, 연산에 직접 참여할수 있는 수준에 도달해야 할 것이다. 그러기 위해서는 CMOS 소자들과의 집적이 필연적인데 광학 배선 요소들과 CMOS 회로 요소들 간에는 상당히 큰 규격의 차이가 존재한다. 따라서, 이미 개별적으로는 성숙한 수준으로 개발되어 있는 광학 소자들에 대하여 CMOS 소자와 비견할 만한 수준의 스케일링(scaling)을 이루는 것이 칩 상 광학 배선(on-chip optical interconnect)을 구현하고 최종적으로는 차세대 3-D VLSI의 배선 기술로 자리매김하는데 관건이 될 것이다.

#### 2. 최신 광학 배선 요소기술의 사례

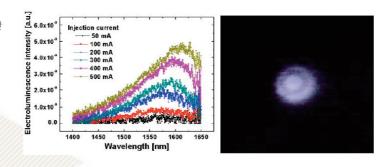

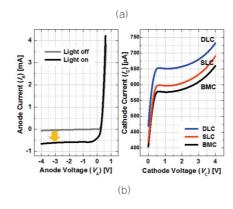

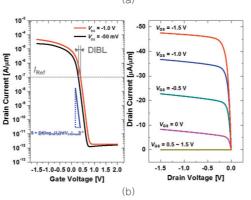

그림 2는 Ge을 기반으로 제작한 LED의 상온에서의 분석 결과를 보여준다. 1550nm 부근에서의 전계 발광(electroluminescence)를 확인할 수 있으며, 적외선 카메라를 통해 육안으로도 관찰할 수 있다. 적절한 양의 AI을 함유함으로써 AIGaAs가 감마 밸리에서 갖는 에너지 밴드갭을 Ge이 갖는 에너지 밴드갭(0.8 eV)보다 크게 하고, n형 AIGaAs로부터 p형 Ge으로 감마 밸리 전송(gamma valley transport)을 함으로써 Ge의 감마 밸리에서의 전자 농도를 높여 발광 효율을 높이는 기술로 소개되었다[1]. 외력이나 반경이 큰 원자를 함량시켜 인장력을 준 Ge에서 발광을 얻는 기술들과 더불어[2,3], Si 상에서 Si과의 집적성이 좋은 4족 원소 기반의 광원을 얻을 수 있는 활용도 높은 방법을 제시한다.

그림 2. Ge LED와 상온에서의 광 스펙트럼 분석 및 방출광 관찰.

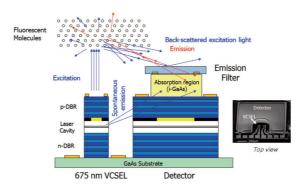

그림 3. III-V 기반에서의 광원 및 광검출기 집적회로.

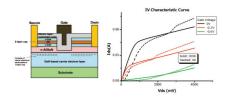

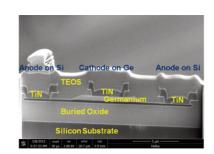

그림 3은 GaAs를 기반으로 하는 광원 및 광검출기를 단일 집적회로 (monolithic integrated circuit)로 구현한 사례이다[4,5]. 기반 물질은 다르지만, 광검출기 측에서 큰 면적을 필요로 한다는 점은 광전자 집적회로를 구성하는 데 해결해야 할 현안의 하나라는 점을 확인시켜 준다. 그림 4는 SOI 기판 상에서 선택적으로 결정성 성장시킨(selective epitaxial growth) Ge을 기반으로 20 GHz급 APD(avalanche photodetector)를 제작한 예와 동작 성능을 보여준다.

그림 4. Ge-on-Si 광검출기. (a) 제작된 소자의 단면적. (b) 광반응 특성 곡선.

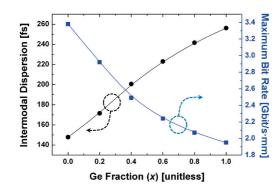

그림 5. Ge 함량에 따른 SiGe 광도파로의 광신호 전송 속도[6].

Ge은 Si 기판 상에 직접적으로 성장시킬 수도 있고, Ge과의 격자 상수의 차이가 비교적 작은 4족 합금인 GeSn 또는 III-V 화합물인 AlGaAs 계열의 물질을 Si 기판 상에 성장시킬 때의 완충층으로 응용할 수 있다. 공정 과정에서의 레벨을 고려해볼 때 Ge은 능동 및 수동 소자의 활성층으로 사용될 수도 있고, 광도파로 물질로의 응용도 가능하다. 광도파로 물질로 사용할 수 있는 가능성은 Ge이 Si보다 높은 굴절률을 가져 광신호의 포획 능력(confinement capability)이 크다는 사실에서 찾을 수 있는데 반해 Ge은 소멸 계수(extinction coefficient)도 역시 크기때문에 Si에 비하여 광도파로 내에서의 광손실이 크므로 최적 설계 시 중요한 요소로 고려해야 한다.

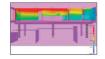

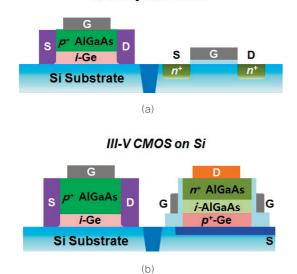

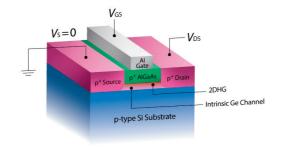

#### 3. 광전자 집적회로를 위한 전자 소자 및 회로 구성

그림 6은 단일 칩 상에서 구현할 수 있는 이종 단일칩 집적회로의 예들을 보여준다. 그림 6(a)는 정공의 이동도가 높은 Ge으로높은 정공 이동도 트랜지스터(high-hole-mobility transistor, HHMT)를 구현하고 기존의 Si NMOS와 결합한 CMOS 회로를,그림 6(b)는 III-V 물질 기반의 CMOS 회로를 Si 상에서 꾸미되 Ge HHMT와 Ge을 소스 접합물질로 갖는 터널링 전계효과트랜지스터(tunneling field-effect transistor, TFET)로 구성한 회로를 보여준다. 그림 6(c)는 로직 회로와 광학 회로를 동시에 집적함으로써 광학 배선 기술을 단일 칩/단일 층 상에서 구현할 수 있는 가능성을 보여주고 있다.

#### Si-Ge Hybrid CMOS

Logic Part (III-V CMOS on Si)

Optical Part

G

S

P\* AlGaAs

I-Ge

P Ge

A

Si Substrate

Optical Part

C

C

D

P\* AlGaAs

A

P Ge

A

(C)

그림 6. 이종 집적 단일 칩 회로 구성의 예. (a) Si-Ge 기반 CMOS. (b) III-V-on-Si CMOS. (c) 로직 및 광학 회로의 직접.

광집적 회로의 구현은 이종 집적(heterogeneous integration)을 근간으로 한다고 볼 수 있으며, 과거 서로 다른 물질 기반으로 구현되어 오던 서로 다른 기능 영역의 소자들, 즉 전자 소자와 광학 소자의 집적이 그 핵심이라고 할 수 있다. 국내외적으로이종 집적에 관한 연구가 점차 많은 관심을 끌고 있는데, 물질레벨에서의 이종 집적을 위한 공정 개발에 주안점을 많이 둔 측면도 있었으나 이종 집적의 본질은 기능의 집적이라는 사실에 목표적인 의미를 두어야 한다.

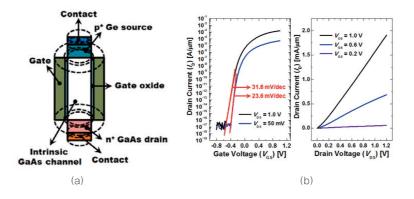

그림 7. Ge/GaAs 이종접합 TFET[7]. (a) 구조의 모식도 (b) 전달 및 출력 특성.

그림 8. Ge 기반의 HHMT[8]. (a) 구조의 모식도. (b) 전달 및 출력 특성.

전자 소자가 새로이 추구해야 하는 바도 찾을 수 있는데, 그것은 물질에 대한 의존성이 큰 광학 소자의 구현이 이루어지는 플랫폼 에서 제작할 수 있는 가능성을 찾아야 한다는 점이다. 위의 그림 7과 그림 8에서 각각 보여주고 있는 Ge을 소스 접합 물질로 하는 TFET, Ge 기반의 HHMT은 Si을 기반으로 하면서도 Ge, GaAs의 이종 접합에서 구현할 수 있는 전자 소자들의 예로서 동일한 물질 구성(configuration)에서 만들 수 있는 광학 소자들과의 집적이 가능하다. 어떤 측면에서는 기존의 Si CMOS 소자 대비 성능지표가 오히려 떨어지는 부분도 있을 수 있다. 그러나 기고의 첫 회에서 살펴본 바와 같이 로직 반도체 소자의 스위칭 속도가 광학 프로세스(optical process)의 속도보다는 훨씬 빠른 수준이고 집적도 역시 CMOS 소자가 훨씬 앞서 있다는 사실을 상기해 볼 때, 광집적 회로를 설계 및 구현하는 과정에서 전자 소자가 속도 및 집적도를 실질적으로 결정해야하는 요소인 광학 소자에 어느 정도 보폭을 맞추어야하는 부분이 불가피하게 존재할 수 있을 것이다.

3회에 걸친 본 기고를 통해 광학 배선 기술의 소개, 이종 집적을 위한 기반 환경 마련 기술, 광전자 집적회로 구현을 위한 요소 기술을 개괄적으로 살펴보았다. 3차원 구조를 지향하는 차세대 초고집적 회로에서는 전력 소모 억제와 처리 속도 향상을 위해 광학적 기술과의 접목이 필연적으로 이루어질 것으로 예상한다. 전 자공학과 광학이라는 서로 다른 영역의 기술이 "이종 접합"되기 위해서는 서로 다른 종류의 플랫폼 물질의 접목이 우선적으로 이루어져야 하는데, 물리적으로 붙이는 방법(bonding)이 현실적인 방안으로 많이 연구되어 왔으며, 보다 근래에는 얼로이(alloy)를 통해 광학 요소들을 구현하는 데 유리한 전자 구조를 갖는 물질을 마련하는 기술에 대한 관심도 높아지고 있다. 이종 집적의 성공은 최종적으로 요소간의 집적에서 결정되는데, 서로 다른 기능을 수행하는 소자들이 공정상의 어려움 없이 처리 속도 및 집적도 등 상대 영역의 기술 지표에 충분히 대응할 수 있는 수준에서 집적이 이루어져야 할 것이다.

사람들은 점차 손 안에서 보다 많은 기능들을 더 긴 시간동안, 그리고 더 빠른 속도로 수행하는 전자 시스템을 필요로 하리라는 점을 생각해볼 때, 차세대 전자공학의 화두는 초저전력 • 초고속이라고 하더라도 결코 무리한 요약이 아닐 것이다. 이를 위해서 전자공학과 광학 기술의 본격적인 접목이 이루어져야 하는 시점이며, 기반 물질의 마련, 광학 소자의 소형화, 전자 소자의 다변화 등이 상호보완적으로 이루어지는 이종 기술간의 근거리 융합이 이루어진다면 칩 상 광학 배선을 기반으로 하는 차세대 집적회로 기술이 결코 먼 미래의 일이 아닐 것이다.

조 성 재 교수 소속: 가천대학교 전자공학과 주 연구분야: 나노전자소자 및 광학소자 E-mail: felixcho@gachon.ac.kr Homepage: http://neol.gachon.ac.kr

#### 참고문헌

[1] S. Cho, B.-G. Park, C. Yang, S. Cheung, E. Yoon, T. I. Kamins, S. J. Ben Yoo, and J. S. Harris, Jr., "Room-temperature electroluminescence from germanium in an Alo.3Gao.7As/Ge heterojunction light-emitting diode by  $\Gamma$ -valley transport," Optics Express, vol. 20, no. 14, pp. 14921-14927, Jul. 2012.

[2] D. Nam, D. Sukhdeo, A. Roy, K. Balram, S.-L. Cheng, K. C.-Y Huang, Z. Yuan, M. Brongersma, Y. Nishi, D. Miller, and K. Saraswat, "Strained germanium thin film membrane on silicon substrate for optoelectronics," Optics Express, vol. 19, no. 27, pp. 25866-25872, Dec. 2011.

[3] J. S. Harris, H. Lin, R. Chen, Y. Huo, E. Fei, S. Paik, S. Cho, and T. Kamins, "MBE Growth of GeSn and SiGeSn Heterojunctions for Photonic Devices," ECS Transactions, vol. 50, no. 9, pp. 601–605, Oct. 2012.

[4] T. D. O'Sullivan, E. Munro, J. S. Harris, and O. Levi, "Fabrication of an integrated 670nm VCSEL-based sensor for miniaturized fluorescence sensing," Proceedings of SPIE, vol. 7615, pp. 76150D-1 - 76150D-7, Feb. 2010.

[5] N. Parashurama, T. D. O'Sullivan, A. D. L. Zerda, P. E. Kalassi, S. Cho, H. Liu, R. Teed, H. Levy, J. Rosenberg, Z. Cheng, O. Levi, J. S. Harris, and S. S. Gambhir, "Continuous sensing of tumor-targeted molecular probes with a vertical cavity surface emitting laser-based biosensor," Journal of Biomedical Optics, vol. 17, no. 11, pp. 117004-1-117004-16, Nov. 2012.

[6] S. Cho, J. Park, H. Kim, R. Sinclair, B.-G. Park, and J. S. Harris, Jr., "Effects of germanium incorporation on optical performances of silicon germanium passive devices for group-IV photonic integrated circuits," Photonics and Nanostructures-Fundamentals and Applications, vol. 12, no. 1, pp. 54-68, Feb. 2014.

[7] S. Cho, I. M. Kang, T. I. Kamins, B.-G. Park, and J. S. Harris, "Silicon-compatible compound semiconductor tunneling field-effect transistor for high performance and low standby power operation," Applied Physics Letters, vol. 99, no. 24, pp. 243505–1–243505–4, Dec. 2011.

[8] S. Cho, I. M. Kang, K. R. Kim, B.-G. Park, and J. S. Harris, Jr., "Silicon-compatible high-hole-mobility transistor with an undoped germanium channel for low-power application," Applied Physics Letters, vol. 103, no. 22, pp. 222102-1-222102-4, Dec. 2013.