IDEC newsletter

VOL. 222 December 2015

IDEC Newsletter I 통권 제222호

● 발행일 2015년 11월30일● 발행인 박인철● 편집인 남병규● 제작 푸울디자인

⊙ 기획 김하늘 ⊙ 전화 042) 350-8535 ⊙ 팩스 042) 350-8540 ⊙ 홈페이지 http://idec.or.kr

⊙ E-mail kimsky1230@idec.or.kr ⊙ 발행처 반도체설계교육센터(DEC)

VOL. 222 DECEMBER 2015

# IDEC newsletter

VOL. 222 December 2015

## OMPW (Multi-Project Wafer) 2015년 MPW 진행 내역

- ■2016년 MPW 진행 일정

- 일정 확정 후 홈페이지와 메일로 안내 예정(12월 중)

- TowerJazz 공정 지원 중단

- ■2015년 MPW 진행 내역

- 6개 공정 16회 진행 (327개팀 설계 참여)

- MPW 진행 일정 및 진행 내역

| 공정        | 회차구분<br>(공정_년도순서) | 모집팀수<br>((mmxmm)x<br>칩수)/회별 | 정규모집<br>신청마강 | 참여팀수<br>((mmxmm)x칩수)         | DB마감       | Die-out    | 비고              |

|-----------|-------------------|-----------------------------|--------------|------------------------------|------------|------------|-----------------|

|           | S65-1501          | [4x4]                       | 2014.12.29   | (4x4)x 39                    | 2015.06.15 | 2015.12.14 | 제작중             |

| 삼성 65nm   | S65-1502          | x48                         | 2015.04.20   | (4x4)x 33                    | 2015.10.19 | 2016.04.19 | 제작중             |

|           | S65-1503          |                             | 2015.06.22   | (4x4)x 40                    | 2016.01.18 | 2016.07.18 | 설계중             |

|           | MS18-1501         |                             | 2014.12.29   | (3.8x3.8)x17<br>(3.8x1.9)x16 | 2015.03.02 | 2015,08,03 | 제작완료            |

|           | MS18-1502         | (3.8x3.8)                   | 2015.01.26   | (3.8x3.8)x20<br>(3.8x1.9x7   | 2015.05.11 | 2015.10.12 | Package<br>제작중  |

| MS 0.18um | MS18-1503         | x25                         | 2015.02.23   | (3.8x3.8)x23                 | 2015.07.13 | 2015.12.14 | Package<br>제작대기 |

|           | MS18-1504         |                             | 2015.03.23   | (3.8x3.8)x22<br>(3.8x1.9)x6  | 2015.09.07 | 2016.02.01 | 제작중             |

|           | MS18-1505         |                             | 2015.05.26   | (3.8x3.8)x24<br>(3.8x1.9)x2  | 2015.12.18 | 2016.05.09 | 설계중             |

| N.C 0.05  | MS35-1501         | (5x4)x20                    | 2015.01.26   | (5x4)x18<br>(5x2)x3          | 2015.06.08 | 2015.09.29 | Package<br>제작중  |

| MS 0,35um | MS35-1502         | (3X4)X20                    | 2015.07.20   | 5x4)x19<br>(5x2)x2           | 2016.01.11 | 2016.04.30 | 설계중             |

| TJ SiGe   | TJS18-1501        | (2.35x2.35)x4               | 2014.12.29   | (2,35x2,35)x1                | 2015.04.27 | 2015.09.15 | 칩제작중            |

| TJ CIS    | TJC18-1501        | (2.35x2.35)<br>x4           | 2015.01.26   | (2,35x2,35)x4                | 2015.11.23 | 2016.03.28 | 제작대기            |

|           | TJC18-1502        |                             | 2015.05.26   | (2,35x2,35)x4                | 2015.11.23 | 2016.03.28 | 설계중             |

|           | TJB18-1501        | (2.35x2.35)                 | 2014.12.29   | (5x2.5)x2<br>(2.35x2.35)x8   | 2015.03.02 | 2015,07,06 | 제작완료            |

| TJBCD     | TJB18-1502        | x12~16                      | 2015.03.23   | (5x2.5)x1<br>(2.35x2.35)x8   | 2015.08.24 | 2015.12.28 | 칩제작중            |

|           | TJB18-1503        |                             | 2015.05.26   | (2.35x2.35)x8                | 2015.11.30 | 2016.04.04 | 설계중             |

\* 담당 : 이의숙(yslee@dec.or.kr)

- \* 일정은 사정에 따라 다소 변경될 수 있음.

- \* 표기 : MS = 매그나칩/SK하이닉스, TJ = TowerJazz

- \* 회차 표기 방법 변경 : 공정 코드-년도 모집 순서 (예시) 삼성 65nm 2015년 1회차 : S65-1501)

- \* TowerJazz 공정은 sub chip(2,35mmX2,35mm)으로 분리하여 모집

- \*모집기간: 모집 마감일로 부터 2주전부터 접수

- \* Package 제작은 Die out 이후 1개월 소요됨

- \* 2015. 11. 25(기준일)

## ○ 2015년 12월 교육프로그램 안내

수강을 원하는 분은 IDEC 홈페이지(www.idec.or.kr)를 방문하여 신청하시기 바랍니다.

#### KAIST 개설 강좌 안내

| 센터명 | 강의일자     | 강의제목                                              | 분류   |

|-----|----------|---------------------------------------------------|------|

|     | 12월 01일  | 직류/직류변환기                                          | 설계강좌 |

| 본센터 | 12월 11일  | Wireless Communication System의<br>이해와 RF IC 설계 기초 | 설계강좌 |

| 충북대 | 12월 8-9일 | 차세대 디스플레이 기술 소개                                   | 설계강좌 |

• 강좌일 : 12월 01일

• 강좌 제목 : 직류/직류변환기

• 강사: 이광찬 박사 (삼성전자 S.LSI)

#### 강좌개요

- 1. 전력변환기 소개

- 2. DC/DC Converter

- 3, Conclusions (QnA)

수강대상 대학원 석사과정 or 직류/직류 변환 설계 초보자

강의수준 초급 강의형태 이론

사전지식, 선수과목 전기회로, 전자회로

• 강좌일 : 12월 11일

• 강좌 제목: Wireless Communication System의 이해와 RF IC 설계 기초

• 강사 : 변영재 교수 (UNIST)

#### 강좌개요

MOS 기본 physics복습을 통한 Wireless Principle들을 점검하고, RF/Wireless IC 설계에 없어서는 안되는 RLC 소자들을 Wireless IC 설계입장에서 재조명을 해본다. Passive 소자에 대한 이해를 바탕으로 Distributed System을 공부하고, S-parameter, Smith Chart 및 bandwidth estimation technique을 숙지한다. 이를 기초로 하여 고주파 영역의 증폭기, LNA, MIXER, PLL 설계를 공부하고, 대표적인 architecture실용 예제를 분석하여 RF IC 설계에 대한 이해도를 높인다.

**수강대상** 전공자중 대학교4학년, 석사 1-2년, 직장인 및 타전공자

강의수준 초급 강의형태 이론

**사전지식, 선수과목** 전자회로 1,2

\*문의: KAIST IDEC 이한나 (042-350-8536, Ihn1224@idec.or.kr)

• 강좌일 : 12월 08-09일

• 강좌 제목 : 차세대 디스플레이 기술 소개

• 강사 : 강현수 교수 (충북대학교)

#### 강좌개요

1.차세대 디스플레이 개발기술을 소개한다 2.산화물 박막 트랜지스터 등 차세대 박막소자 개발 현황을 소개한다.

수강대상 학부, 대학원생, 일반인

강의수준 초급 강의형태 이론

**사전지식, 선수과목** 없음

\*문의: 충북대 IDEC 라해미 (043-261-3572, idec@chungbuk.ac.kr)

# IDEC newsletter

## O Chip Design Contest (CDC)

• International SoC Design Conference(ISOCC) 2015 Chip Design Contest(CDC) 개최

1. 일정 및 장소 : 2015년 11월 03일(화), 경주 현대호텔

#### 2. 진행 일정

| 구분        | 시간            | 내용                     |  |  |  |

|-----------|---------------|------------------------|--|--|--|

| 페너 O스티 바ㅠ | 00:00 - 00:45 | CDC session 1~3        |  |  |  |

| 패널 우수팀 발표 | 09:00 ~ 09:45 | • 총 8편, 한 편당 15분 발표    |  |  |  |

| 데모/패널 전시  | 09:00 ~ 15:30 | 데모 7팀, 패널 96팀          |  |  |  |

| 네포/페글 전시  | 09.00 19.00   | •총 103팀, 오전-오후로 나누어 전시 |  |  |  |

#### 3. 시상 내용

#### - Best Design Award (1팀)

| 소속      | 저자        | <del>논</del> 문명                               |

|---------|-----------|-----------------------------------------------|

| 금오공과대학교 | 이필호 장영찬   | An On-Chip Monitoring Circuit for 8-Gb/s      |

| ㅁㅗㅇ뉘네⊣ㅛ | VIZT, 00L | QDR Differential Signaling Integrity Analysis |

#### - Best Demo Award (2팀)

| 소속     | 저자       | 논문명                                         |

|--------|----------|---------------------------------------------|

| 중앙대학교  | 김주언 백광현  | 12-bit 15Ms/s SAR ADC with dummy            |

| 00414# | DTL, 70L | capaictor switching for capacitor reduction |

| 동국대학교  | 손충환, 변상진 | 4Gb/s, 0.97mW/Gb/s CMOS CDR IC with DVS     |

#### - Best Poster Award (5팀)

| 소속       | 저자               | 논문명                                      |

|----------|------------------|------------------------------------------|

| POSTECH  | 조윤성, 김범만         | Voltage Combined CMOS Doherty Power      |

| FOSTECIT | <u>т</u> до, пос | Amplifier Based on Transformer           |

| POSTECH  | 이두복, 김재준         | A 3.8mW 10Gb/s CDR for                   |

| FOSTECTI | 이구국, 검시I正        | Clock-Embedded Intra-Panel Interface     |

|          |                  | An Optimum Loop Gain Tracking            |

| 서울대학교    | 장성천, 정덕균         | All-Digital PLL Using Autocorrelation of |

|          |                  | Bang-Bang Phase-Frequency Detection      |

| 중앙대학교    | 유태근, 백광현         | A 9-bit CMOS DDFS with Area and          |

| 오임네릭파    | ㅠ네正, 픽링인         | Power Efficient Architecture             |

| 중앙대학교    | 성은택 백동현          | A Fast-transient Output-Capacitorless    |

|          | ·승근국, 액등인        | LDO Regulator for SoC Applications       |

|          |                  |                                          |

#### • The 23rd Korean Conference on Semiconductors(KCS) Chip Design Contest(CDC) 개최

1. 일정 및 장소 : 2016년 02월 23일(화), 강원도 하이원리조트

#### 2. 주요 일정

| 구분       | 날짜            | 내용                                              |

|----------|---------------|-------------------------------------------------|

| 논문 접수 마감 | 2015.11.20(금) | 논문 작성 양식 :                                      |

| 논문 채택 통보 | 2015.12.18(금) | <ul><li>IDEC 논문 양식으로 작</li><li>성해야 함.</li></ul> |

#### 3. 시상 내역

| Award 명           | 수상팀 수 | 내용             |

|-------------------|-------|----------------|

| Best Design Award | 1팀    | 상장 및 상금 100만원  |

| Best Demo Award   | 2팀 내외 | 각 상장 및 상금 50만원 |

| Best Poster Award | 4팀 내외 | 각 상장 및 상금 20만원 |

수상팀 수는 참여팀 수에 따라 조정될 수 있음.

\*문의: KAIST IDEC 김하늘 (042-350-8535, kimsky1230@idec.or.kr)

## O ISOCC 2015 Chip Design Contest 개최 소식

• 2015.11.03(화), 경주 현대호텔

반도체설계교육센터(IDEC)는 지난 11월 3일 경주 현대호텔에서 ISOCC 2015 Chip Design Contest를 개최했다. 이날 행사를 통해 총 103편의 논문이 발표되었다. 그 중 데모는 총 7팀이, 패널은 총 96팀이 참여하였다.

Chip Design Contest에 제출된 논문은 평가를 통해 우수팀에게 Best Design Award, Best Demo Award(SSCS 서울챕터상 및우수상), Best Poster Award를 수여한다. 가장 우수한 논문에게 주어지는 Best Design Award는 금오공과대학교 이필호(논문명: An On-Chip Monitoring Circuit for 8-Gb/s QDR Differential Signaling Integrity Analysis)에게 돌아갔다.

또한, 데모 참여팀 중 우수팀에게 수여되는 Best Demo Award는 중앙대학교 김주언(SSCS 서울챕터상), 동국대학교 손충환(우수상)이 받았다. 패널 참여팀 중 우수팀에게 수여되는 Best Poster Award는 POSTECH 조윤성, POSTECH이두복, 서울대학교 장성천, 중앙대학교 유태근, 중앙대학교 성은택이 받았다. 이번 행사에서는 Best Demo Award(SSCS 서울챕터상)과 Best Poster Award에 대한 시상만이 이루어졌다.

Best Design Award와 Best Demo Award(우수상)에 대한 시상은 오는 2016 IDEC SoC Congress에서 진행될 예정이다.

반도체설계교육센터(IDEC)에서 주관하는 Chip Design Contest는 반도체 및 시스템 설계분야의 기술공유 및 활발한 정보교류의 장이다. 이는 국내외 Foundry를 통해 제작된 IC 및 PLD를 이용하여 구현한 칩 내용을 시현 및 전시하는 행사로써,국내 시스템반도체 인력배출의 요람으로 자리잡고 있다.

\*문의: KAIST IDEC 김하늘 (042-350-8535, kimsky1230@idec.or.kr)

# 기반 연산의 정확도 향상 연구.

#### 서론

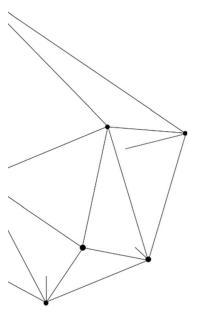

Logarithmic number system (LNS)는 컴퓨터 연산 방식의 대안으로 곱셈, 나눗셈, 제곱 연산 등과 같은 연산을 덧셈과 뺄셈으로 바꿔서 계산함으로써 빠르고 쉽게 연산 결과를 구하는 데에 사용되는 연산 시스템이다. 그림 1에서 볼 수 있듯 이러한 연산은 로그 변환, 덧셈/뺄셈 연산, 그리고 역로그 변환으로 이루어지며, 역로그 변환을 하기 전 연속적인 덧셈/뺄셈 연산도 할 수 있다. 이때, 로그 변환과 역로그 변환에서 지연시간의 상당 부분이 발생한다. 따라서, LNS 기반 연산이 실용화 되기 위해서는 로그 변환과 역로그 변환이 빨라야 하며, 이를 위한 모든 회로가 비교적 쉽고 적은 수의 논리 게이트로 구현되어야 한다. 또한, 임계 경로 지연시간이 적게 걸리도록 구현되어야 하며, 회로로 구현했을 때 저전력으로 구현되어야 한다. 마지막으로 연산결과의 오차가 적게 구현되어야 한다. 본기고문에서는 LNS 기반 연산에서 가장 긴 지연시간을 차지하는 로그 변환 회로 설계 방법에는 어떠한 것들이 있고, 설계 방법에 따라 오차가 어떻게 개선되는지에 대해 중점적으로 살펴보고자 한다.

LNS를 기반으로 한 연산은 크게 보면 Brubaker가 1975년에 제안 한 look up table (LUT) 기반 방식 [1]과 Mitchell이 1962년에 제 안한 Mitchell algorithm (MA) 기반 방식 [2]로 나눌 수 있다. LUT 는 어떤 함수를 논리회로로 구현 할 때 그 함수를 직접 계산하는 특수 논리회로를 만들지 않고, 구현하고자 하는 함수의 모든 가능 한 입력 값에 대해 출력 값을 작은 메모리에 저장함으로써 (어떤 출 력 값에 해당하는 메모리 데이터는 그 출력 값을 갖게 하는 입력 데이터를 해당 메모리 위치를 가리키는 주소 값으로 사용함) 쉽고 빠른 방법으로 임의의 함수를 구현하는 회로다. 임의의 연산을 구 현하기 위해서는 각 입력에 대한 결과를 LUT(메모리)에 표의 형태 로 저장해 놓으면 된다. 복잡한 연산을 통해 직접 구하는 것보다 메 모리로부터 값을 바로 받아오는 것이 더 빠른 경우가 많기 때문에 LUT를 사용한다. 하지만 LUT는 모든 입력에 대한 결과값을 저장 하기 위한 별도의 메모리가 필요하다는 단점이 있다. 이러한 단점 을 보완하기 위해 더 적은 메모리 용량으로 LNS 기반 연산을 하기 위한 노력들이 있었다. [8-10]

하지만, Mitchell이 LUT를 사용하지 않고 로그 변환이 가능한 방법을 제안하면서 이후의 많은 연구들이 MA 기반 방식에 초점을 두고 이루어지고 있다. Mitchell이 제안한 방식은 별도의 추가적인 메모리를 사용하지 않고 간단한 시프팅과 카운팅 그리고 덧셈으로 연산을 단순화시켰다. 이 방식의 단점은 특정 지점에서 오차가 발생한다는 것인데, 이를 개선하기 위해 많은 연구들이 진행되어 오는중이다. 지금부터 MA 기반 방식의 기술 변천과 최근까지 연구 현황에 대해 소개하고자 한다.

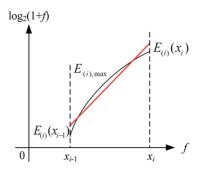

#### 그림 1. LNS 기반 연산

#### 현재까지 기술 변천 및 연구 현황

#### 1. Mitchell이 제안한 방식 - Mitchell, IRE Trans. Electron. Comput, [2]

Mitchell은 로그 값을 저장할 별도의 메모리가 필요하지 않은 로그 변환 방식을 제안하고, 이를 이용해 곱셈과 나눗셈 연산을 하는 것을 제안했다. 그 방식은 다음과 같다. 임의의 숫자 N 을 아래와 같이  $\frac{1}{2}$  수 있다.

$$\mathcal{N} = 2^{k}(1+f), 0 \le f \le 1$$

이 N에 밑이 2인 로그를 취하면,

$$\log_2 \mathcal{N} = k + \log_2 (1 + f)$$

이다. 여기서 k가 log의 정수 부분이고,  $log_{z}(1+f)$  가 소수 부분이다. Mitchell은 여기서 소수 부분인  $log_{z}(1+f)$  를 f로 선형 근사를 시켜서 아래와 같이 log 변환하는 것을 제안했다.

#### $log_{\mathfrak{I}} \mathcal{N} \cong k + f$

이때, 소수 부분에서  $\log_2 \mathcal{N}(1+f)$ -f 만큼의 오차가 발생하게 된다. 이 것이 앞에서 말한 MA 기반 방식의 단점이다. 아래의 표는 Mitchell 의 방법으로 로그 변환을 했을 경우의 결과를 정리한 표이다. 표 1을 보면 실제 로그값과 MA 기반으로 로그를 변환했을 때의 값을 비교해볼 수 있다. 결국 MA 기반 방식의 핵심은 로그로 변환 과정에서 소수 부분을 선형근사화 시키는 것에 있다. 이후에 진행된 연구들은 선형근사화 과정에서 생기는 오차를 줄이는 것에 집중했다.

표 1. Mitchell의 방식을 이용한 로그 변환 결과 ([3]의 표 인용)

| N<br>Decimal | N<br>Binary | log <sub>2</sub> N<br>Exact | log₂N<br>Exact | log <sub>2</sub> N<br>Exact |

|--------------|-------------|-----------------------------|----------------|-----------------------------|

| 1            | 00001       | 0.00000                     | 0.00000        | 000.0000                    |

| 2            | 00010       | 1.00000                     | 1.00000        | 001.0000                    |

| 3            | 00011       | 1.58496                     | 1.50000        | 001.1000                    |

| 4            | 00100       | 2.00000                     | 2.00000        | 010.0000                    |

| 5            | 00101       | 2.32193                     | 2.25000        | 010.0100                    |

| 6            | 00110       | 2.58496                     | 2.50000        | 010.1000                    |

| 7            | 00111       | 2.80735                     | 2.75000        | 010.1100                    |

| 8            | 01000       | 3.00000                     | 3.00000        | 011.0000                    |

| 9            | 01001       | 3.16992                     | 3.12500        | 011.0010                    |

| 10           | 01010       | 3.32193                     | 3.25000        | 011.0100                    |

| 11           | 01011       | 3.45942                     | 3.37500        | 011.0110                    |

| 12           | 01100       | 3.58496                     | 3.50000        | 011.1000                    |

| 13           | 01101       | 3.70043                     | 3.62500        | 011.1010                    |

| 14           | 01110       | 3.80735                     | 3.75000        | 011.1100                    |

| 15           | 01111       | 3.90689                     | 3.87500        | 011.1110                    |

| 16           | 10000       | 4.00000                     | 4.00000        | 100.0000                    |

| 17           | 10001       | 4.08747                     | 4.06250        | 100.0001                    |

# 2. 오차 평탄화(Error-flattened)를 고려하지 않는 방식(1) -Abed, IEEE Trans. Comput. 2003 [3]

Mitchell이 선형 근사를 이용한 로그 변환을 제안한 이후, 이 방식에 기반한 많은 연구들이 있었다. 특히, Mitchell의 방식에 의해 생기는 오차를 줄이기 위한 연구들이 많았다. 크게 보면 선형 근사 구간을 나누는 방식 [3-6], 오차 정정 항을 추가하는 방식 [11], 피연산자를 분해하는 방식 [12]으로 나누어 연구가 진행되었다. 특히, 선형 구간을 나누는 방식에 대한 연구가 가장 활발하게 이루어졌다. 따라서 본 기고문에서도 선형 구간을 나누는 방식에 초점을 두고자 한다.

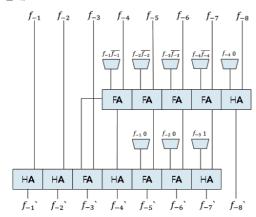

대표적으로 2003년 IEEE Trans. Comput.에 실린 Abed의 연구가 있다. Abed는 소수 부분인  $\log_2(1+f)$ 를 선형 근사 시킬 때, 구간을 2-구역, 3-구역, 6-구역으로 각각 근사 구간을 나누고, 이때의 오차 분석을 수행했다. 이때, 오차를 평탄화하는 것은 고려하지

않았다. 2-구역으로 근사 구간을 나누는 경우를 보면 근사식은 아래와 같다.

$$log_2(1+f) = \begin{cases} f + 2^{-2} f_{\text{amsBits}}, 0 \le f < 0.5 \\ f + 2^{-2} f_{\text{amsBits}}, 0.5 \le f < 1 \end{cases}$$

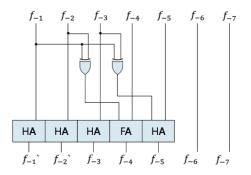

여기서  $f_{aMSBits}$ 는 소수 부분의 MSB 3bits을 사용하겠다는 의미이다. 3-구역, 6-구역으로 나누는 방식도 2-구역을 나누는 방식과 유사하다. Abed가 제안한 방식 중  $\log_2(1+f)$ 를 선형 근사 시킬 때 2-구역으로 나누는 방식을 예로 들어보자. 2-구역으로 나누어 근사 시키기 위해 XOR gate와 half adder(HA) 그리고 full adder(FA)로 모델링 한 그림은 아래와 같다.

그림 2. Abed의 방식으로 2-구역 근사 [3]

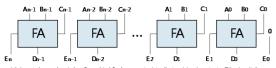

위의 그림 1에서 HA와 FA는 가장 기본적인 연산을 수행하는 논리회로 중 하나로 아래와 같은 구조를 가진다.

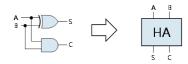

그림 3. Half adder의 구조 [7]

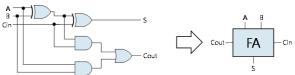

그림 4. Full adder의 구조 [7]

그림 3와 그림 4을 보면 알 수 있듯 HA와 FA는 간단한 논리 게이 트로 구성 가능하다.

# 3. 오차 평탄화(Error-flattened)를 고려하지 않는 방식(2) - Kim, IEEE J. Solid-State Circuits 2006 [4]

2006년 J. Solid-State Circuits에 실린 Kim의 연구는 로그의 소수 부분을 8-구역으로 균등하게 나누어 선형 근사 시키는 방식을 제안했다. [4] 각 구간의 크기를 0.125로 균등하게 나누고 아래와 같이 근사식을 구성하였다.

$$\log_2(1+f) = \left\{ \begin{array}{l} f + 2^{-1}f + (2^{-3} + 2^{-7})\bar{f}, \ 0 \leq f < 0.125 \\ f + 2^{-1}f + (2^{-2} + 2^{-6})\bar{f} + 15/1024, \ 0.125 \leq f < 0.25 \\ f + 2^{-2}f + (2^{-3} + 2^{-6})\bar{f} + 46/1024, \ 0.25 \leq f < 0.375 \\ f + 2^{-7}\bar{f} + 91/1024, 0.375 \leq \bar{f} < 0.5 \\ f + 2^{-4}f + (2^{-3} + 2^{-7})\bar{f} + 123/1024, 0.5 \leq f < 0.625 \\ f + (2^{-3} + 2^{-6})\bar{f} + 167/1024, 0.625 \leq f < 0.75 \\ f + 2^{-4}f + (2^{-2} + 2^{-6})\bar{f} + 215/1024, 0.75 \leq f < 0.875 \\ f + (2^{-2} + 2^{-7})f + 264/1024, 0.875 \leq f < 1 \end{array} \right.$$

이 연구에서 로그의 소수 부분을 8-구역으로 나누어 근사화하는 회로는 아래 그림 5와 같다. 이 연구에서는 로그 변환뿐만 아니라 그 이후 여러 연산을 수행하는 것까지 구현하였다. 곱셈, 나눗셈, 역수, 제곱근, 역제곱근, 제곱, n-제곱을 LNS에 기반하여 연산을 수행하였다. 이 논문에 따르면, 가장 큰 오차 범위는 0.21%으로 (나눗셈) 상당히 정확하다는 것을 알 수 있다.

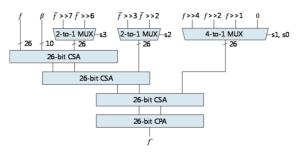

그림 5. Kim의 방식으로 8-구역 근사 [4]

그림 5를 보면 알 수 있듯 덧셈과 시프팅을 통해 로그의 소수부분을 근사화한다. 그림 2의 경우는 간단한 근사였기 때문에 XOR gate로 시프팅이 가능했지만, 이 경우에는 근사화 식이 많고 시프팅할 것이 많기 때문에 필요한 값들을 multiplexer (MUX)를 사용해 선택하였다. Carry save adder (CSA) 및 MUX 등의 구조는모두 간단한 논리 게이트로 구현이 가능하다.

CSA의 구조는 아래 그림 6과 같이 나타난다. CSA는 3개의 n-bit 입력 값을 더하여 2개의 (n+1)-bit 출력값을 만들어내는 매우 빠른 덧셈 회로다. 출력 속도가 빠른 이유는 각 비트 단계에서 이전 비트 단계의 carry-out 결과를 기다릴 필요 없이, 바로 처음부터 그 비트 단계의 sum 값과 carry-out 값을 구할 수 있기 때문이다. 물론 이렇게 하게 되면 2개의 (n+1)-bit 값이 나오므로 덧셈을 제대로 한 것이 아니라는 오해가 등장할 수 있지만, 3개의 multi-bit 값을 2개의 multi-bit 값으로 줄인 것이므로 더해야 할 숫자들을 줄인 것은 맞다. 3개 이상의 multi-bit 값을 더해야 할 때에는 CSA와 같은 회로를 사용하는 것이 이롭다 (물론 1개의 최종 덧셈 값을 원하면 언젠가는 2개의 multi-bit 값을 더하여 1개의 multi-bit 값으로 만들어야 하며, 이 작업은 별도의 carry propagate adder (CPA) 회로가 한다).

n-bit input A = An-1 An-2  $\cdots$  A1 A0 (connected to first adder inputs to FA circuits) n-bit input B = Bn-1 Bn-1  $\cdots$  B1 B0 (connected to second adder inputs to FA circuits) n-bit input C = Cn-1 Cn-1  $\cdots$  C1 C0 (connected to carry-in inputs to FA circuits) (n+1)-bit output D = Dn Dn-1  $\cdots$  D1 D0 (connected to sum outputs of FA circuits) (n+1)-bit output E = En En-1  $\cdots$  E1 E0 (connected to carry-out outputs of FA circuits)

그림 6. n-bit carry save adder (CSA)

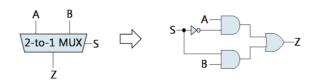

또한, 그림 5를 보면 2-to-1 MUX와 4-to-1 MUX가 쓰이는 것을 볼 수 있다. 2-to-1 MUX의 경우 선택 비트의 값에 따라 A와 B를 선택하게 된다. 2-to-1 MUX의 진리표와 구조는 아래와 같다.

그림 7 2-to-1 MUX

표 2 2-to-1 MUX 진리표

| S | A | В | Z |

|---|---|---|---|

|   | 0 | 0 | 1 |

|   | U | 1 | 1 |

| 0 | 1 | 0 | 0 |

|   | 1 | 1 | 0 |

|   |   | 0 | 1 |

|   | 0 | 1 | 0 |

| 1 |   | 0 | 1 |

|   | 1 | 1 | 0 |

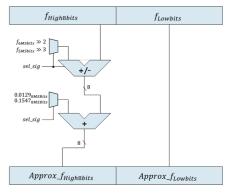

#### 4. 오차 평탄화를 고려한 방식 - Lin, VLSI-DAT 2013 [5]

2013년 VLSI-DAT에서 Lin은 기존의 근사 구간을 나누는 방식에서 오차 평탄화까지 고려하여 오차를 더 줄이는 방법을 제안했다. [5] 그는 근사 구간을 2-구역으로 나눌 때 오차 평탄화를 고려하여 아래와 같은 근사식을 구성했다.

$$\log_2(1+f) = \begin{cases} f + (2^{-3} + 2^{-4}) \underline{f}_{\text{4MSBita}}, 0 \le f < 0.375 \\ f - 2^{-3} + 2^{-4}) \underline{f}_{\text{4MSBita}} + 2^{-3}, 0.375 \le f < 1 \end{cases}$$

위의 식을 바탕으로 시프트와 덧셈으로 하드웨어 구성을 하면 아래 와 같다.

그림 8. Lin의 방식으로 2-구역 근사값 회로 블록도 [5]

2-구역 이외에도 4-구역, 8-구역, 16-구역, 32-구역에서 오차 평 탄화를 고려하여 근사 하는 방식과 오차 평탄화를 고려하지 않은 방식의 오차를 비교하는 결과를 보였다. 그 결과는 아래 표와 같다.

표3. 오차 평탄화 고려 유무에 따른 오차 범위 비교 ([5]에서 인용)

|                        | 나누는 구역 수에 따른 오차 범위        |        |        |          |          |

|------------------------|---------------------------|--------|--------|----------|----------|

| 나누는 방식                 | 2-구역 4-구역 8-구역 16-구역 32-구 |        |        |          |          |

| 균등<br>(오차 평탄화 고려하지 않음) | 0.0291                    | 0.0089 | 0.0025 | 6.63E-04 | 1.71E-04 |

| 불균등<br>(오차 평탄화 고려함)    | 0.0211                    | 0.0054 | 0.0013 | 3.38E-04 | 8.46E-05 |

표 3를 보면 더 많은 구역을 나눌수록 오차 범위가 줄어드는 것을 볼 수 있다. 또한, 구역을 나눈 수가 같을 때 오차 평탄화를 고려한 경우와 오차 평탄화를 고려하지 않은 경우를 비교해보면 오차 평탄화를 고려한 경우가 오차 범위가 더 줄어드는 것을 볼 수 있다.

#### 5. Maximum Absolute Error (MAE) 또는 Signal-to-Noise Ratio (SNR)를 반영하는 방식 - Liu, IEEE Trans. Comput. 2015

가장 최근에 진행된 연구는 Liu가 제안한 MAE 또는 SNR을 반영해서 오차를 줄이는 방식[6]이다. 이 방식은 오차 평탄화를 고려한상황에서 MAE나 SNR를 이용해 각 구간에서 오차의 최대값을 구하고, 이 값을 고려해서 평탄화된 오차를 더 줄이는 방식이다. 우선오차 평탄화를 고려하여 근사 구간을  $2^{\frac{1}{2}}(0 \le k < n)$ 크기로 나눈다. 그렇게 되면 각 구간마다 근사식은 아래와 같다.

$$\log_2(1+f)\hat{}_{(i)} = \frac{\frac{1}{n}}{\frac{i}{2^{\frac{i}{n}}-2^{\frac{i-1}{n}}}} \left(1+f-2^{\frac{i-1}{n}}\right) + \frac{i-1}{n}, 2^{\frac{i-1}{n}} \le f+1 < 2^{\frac{i}{n}}$$

이후, MAE나 SNR을 이용하여 구한 각 구역에서 오차의 최대값을 반영해 근사식을 구한다. MAE를 반영해서 구한 오차의 최대값은

$$E_{(i),max} = \log_2(\frac{n\left(\frac{1}{n} - 1\right)}{ln2}) + \frac{1}{n\left(\frac{1}{2^n} - 1\right)} - \frac{1}{ln2} \equiv E_{max}(n)$$

이다. 그리고 SNR을 반영해서 구한 오차의 최대값은

$$\mathbb{E}_{(\hat{i}),max} = \log_2(\frac{1}{a_{(\hat{i})}^{SNR} \ln 2}) - a_{(\hat{i})}^{SNR} - b_{(\hat{i})}^{SNR} - \frac{1}{\ln 2}$$

$$(a_{(j)}^{SNR} = \frac{I_2^{(i)} - \frac{x_{i-1} + x_i}{2} I_1^{(i)}}{\frac{x_i^2 - x_{i-1}^2}{3} - \frac{(x_i^2 - x_{i-1}^2)(x_i + x_{i-1})}{3}, b_{(j)}^{SNR} = \frac{I_1^{(i)}}{x_i - x_{i-1}} - \frac{a_{(j)}^{SNR}(x_{i-1} + x_{i-1})}{2}$$

$$(I_{1}^{(j)} = \left(f \log_{2} f - \frac{f}{\ln 2}\right) \Big|_{2\frac{1}{\pi}}^{\frac{1}{2\pi}}, I_{2}^{(j)} = \left(\frac{f^{2}}{2} \log_{2} f - \frac{f^{2}}{4 \ln 2}\right) \Big|_{2\frac{1}{\pi}}^{\frac{1}{2\pi}} - I_{1}^{(j)})$$

이다. MAE나 SNR을 통해  $E_{max}(n)$  를 구하여 근사식에 반영시 키면 아래와 같다.

$$\log_2(1+f)^{\text{`MAE or SNR}}_{\text{(i)}} = \log_2(1+f)^{\text{`}}_{\text{(i)}} + \frac{E_{\max(n)}}{2}, 2^{\frac{i-1}{n}} \leq f+1 < 2^{\frac{i}{n}}$$

위 식을 그래프 상에서 표현하면 아래와 같이 나타낼 수 있다.

그림 9. i-번째 구역의 근사식 (빨간색 선) ([6]의 그림 인용)

그림 9을 보면 알 수 있듯, 오차의 최대값을 반영하여 근사식을 보정해주었기 때문에 오차 범위가 줄어드는 것을 확인할 수 있다. 이 방식을 이용하여 기존의 방식과 MAE, maximum error range (MER), SNR을 비교해보면 아래 표와 같다.

표4. 사용한 방식에 따른 MAE, MER, SNR 비교 ([3-6]에서 인용)

| 사용한 방식<br>(n은 나누는 구역의 수) | MAE     | MER      | SNR(dB) |

|--------------------------|---------|----------|---------|

| [3] (n=2)                | 4.49e-2 | 6.32e-2  | 90.1    |

| [5] (n=2)                | 3.7e-2  | 4.48e-2  | -       |

| [6] (n=2)                | 1.75e-2 | 3.37e-2  | 103.3   |

| [3] (n=3)                | 2.93e-2 | 5.006e-2 | 95.3    |

| [4] (n=8)                | 2.05e-3 | 3.55e-3  | 145.2   |

| [6] (n=7)                | 1.79e-3 | 3.2e-3   | 152.3   |

표 4을 보면 알 수 있듯, 나누는 구역의 개수가 많아질수록 오차가 적어지는 것을 확인할 수 있다. 오차 평탄화를 고려한 경우와 고려를 하지 않은 경우, 추가적으로 최대 오차 값까지 반영한 경우를 비교하면 오차 평탄화를 고려한 경우가 고려하지 않은 경우보다 오차가 적다. 또한, 최대 오차의 값을 반영한 경우와 하지 않은 경우를 비교하면 최대 오차를 반영한 경우가 오차가 더 적은 것을 확인할수 있다. 오차 평탄화와 SNR을 반영해서 2-구역 근사를 설계한 그림은 아래와 같다.

$sel\_sig = f_2 \cdot f_3 + f_1$

그림 10. Liu의 방식으로 구한 2-구역 근사값 회로 블록도 [6]

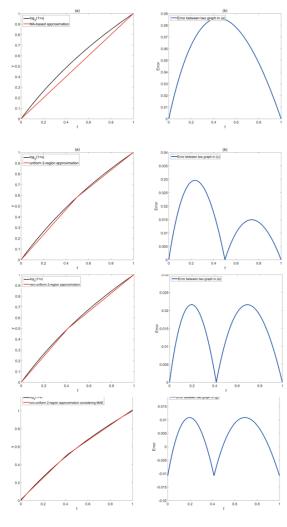

지금까지 MA 기반 방식의 발전 과정을 살펴보았다. 아래의 그래프들은 위의 변화 과정들을 거치면서 소수 부분 근사 과정에서 오차가 얼마나 감소하는지를 보여준다.

그림 11, MA 기반 방식의 발전 과정에 따른 오차 감소 (a) Mitchell의 방법에 의한 근사, (b) Mitchell의 방법에 의한 오차, (c) 오차 평탄화를 고려하지 않은 근사 (2-구역 근사), (d) 오차 평탄화를 고려하지 않은 근사에 의한 오차, (e) 오차 평탄화를 고려한 근사 (2-구역 근사), (f) 오차 평탄화를 고려한 근사에 의한 오차, (g) MAE 또는 SNR까지 고려한 근사(2-구역 근사), (h) MAE 또는 SNR까지 고려한 근사에 의한 오차

#### 결론

지금까지 LNS 기반 연산에 사용하기 위한 로그 변환 기술 변천 및 연구 현황을 살펴보았다. Mitchell이 1962년 제안한 방식을 기반으 로 오차를 줄이기 위한 많은 연구들이 있어왔다. 이 연구들에서 제 안한 방법으로는 시프팅, 카운팅 그리고 덧셈만으로 로그 변환이 가능했다.

입력된 숫자를 로그로 변환시키는 것만 쉽게 해결이 된다면, 변환된 로그 값을 가지고 연산을 수행할 때 곱셈의 경우 덧셈으로, 나눗셈의 경우 뺄셈으로 바뀌게 되므로 계산이 쉬워진다. 일반적인디지털 회로에서의 곱셈은 부분 곱을 구하고, 그 부분 곱들을 누적합시키는 과정이 필요한데, 이때 상당한 하드웨어가 필요하다. 그러나 LNS 기반 연산을 하게 되면 여러 번 더해져야 할 것이 로그로 변환 후 한 번만 덧셈 연산을 수행되므로 효율적이다. 이를 하드웨어로 구현할 때, 하드웨어 비용에 상당한 감소를 가져올 것이다.

이러한 이점은 이미지 처리나 동영상 처리와 같은 approximate computing이 허용되는 digital signal processing (DSP) 응용에 다양하게 쓰일 수 있을 것이라고 생각한다. 또한, 로그 값의 소수 부분을 선형 근사 하는 부분을 제외하면, 나머지 부분은 공통된 부분이므로 FPGA를 사용하여 reconfigurable 특성을 살려 구현하면 사용자의 요구에 따라 근사 구간의 개수를 바꿔가며 오차값을 조절하는 것도 가능할 것이라고 생각한다.

#### 〈저자 정보〉

이 승 구 교수 소속 : 포항공과대학교 전자전기공학과 주 연구분야 : 무선센서 네트워크, 무선 애드 혹 네트워크, 병렬 및 분산 처리, 실시간 컴퓨팅, 결함 포용 컴퓨팅 E-mall : slee@postech.ac.kr Homepage: http://esa.postech.ac.kr

하 민 호 소속 : 포항공과대학교 전자전기공학과 석사과정 주 연구면야 : 임베디드 시스템 E-mail : ml005@postech,ac,kr Homepage: http://esa.postech.ac,kr

#### 참고 문헌

- [1] T.A. Brubaker and J.C. Becker, "Multiplication Using Logarithms Implemented with Read-Only-Memory," IEEE Trans. Computers, pp. 761–766, 1975.

- [2] J. N. Mitchell, "Computer Multiplication and Division using Binary Logarithms," IRE Trans. Electronic Computers, pp. 512–517, vol. 11, Aug. 1962.

- [3] K. H. Abed and R. E. Siferd, "CMOS VLSI implementation of a low-power logarithmic converter," IEEE Trans. Computers, vol. 52, pp. 1421?1433, Nov. 2003.

- [4] H. Kim, B.-G. Nam, J.-H. Sohn, J.-H. Woo, and H.-J. Yoo, "A 231-MHz, 2.18-mW 32-bit logarithmic arithmetic unit for fixed-point 3-D graphics system," IEEE J. of Solid-State Circuits, vol. 41, pp. 2373?2381, Nov. 2006.

- [5] T.-C. Lin, S.-K. Chen, and C.-W. Liu, "A low-error and Rom-free logarithmic arithmetic unit for embedded 3D graphics applications," in Proc. International Symp. VLSI Design, Automation, and Test (VLSI-DAT), April 2013.

- [6] C. W. Liu, S. H. Ou, K. C. Chang, T. C. Lin, and S. K. Chen, "A low-error, cost-efficient design procedure for evaluating logarithms to be used in a logarithmic arithmetic processor," IEEE Trans. Computers

- [7] https://ko.wikipedia.org/wiki/%EA%B0%80%EC%82%B0%EA%B8%B0

- [8] G.L. Kmetz, "Floating Point Logarithmic Conversion System," United States Patent no. 4,583,180, Apr. 1986.

- [9] R. Maenner, "A Fast Integer Binary Logarithm for Large Arguments," IEEE Micro, pp. 41–45, Dec. 1987.

- [10] M. Arnold, T. Bailey, and J. Cowles, "Error Analysis of the Kmetz/Maenner Algorithm," J. VLSI Signal Processing, pp. 37–53, 2003.

- [11] M.J. Duncan, "Improved Mitchell Based Logarithmic Multiplier for Low Power DSP Applications," IEEE Int' I System on a Chip Conf. (SOCC), pp. 17–20, 2003.

- [12] V. Mahalingam and N. Ranganathan, "Improving accuracy in Mitchell's logarithmic multiplication using operand decomposition," IEEE Trans. Computers, vol. 55, pp. 1523?1535, Dec. 2006.

#### 서론

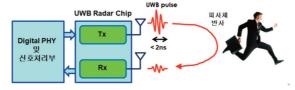

UWB(Ultra-Wide Band) 기반의 초고속 임펄스 신호를 이용한 전 파센서는 기존 국방분야의 감시 정찰용 센서에 대한 관심으로 연구 가 시작되어 국방, 민수 분야에서 감시 및 보안 센서로 사용되고 있 다. 감시, 보안센서 이외에도 UWB신호는 광대역의 특성상 투과성 이 좋고 펄스폭이 매우 짧아 고해상도의 탐지가 가능하여, 은닉된 물체나 지표면 밑의 지뢰 등을 찾아내는 GPR(Ground Penetration Radar)과 벽투과를 활용한 실내의 탐지(See Through Wall) 등의 분야에서 꾸준히 사용되어 왔다. 또한, 최근 사물 인터넷(IoT) 기술의 발달과 함께 TV, 에어컨, 자동차 등의 가전 및 전장 분야에 서도 응용 가능성을 위한 기술개발과 탐색이 활발히 진행되고 있으 며, 밀리미터 수준의 초고해상도의 특징을 이용하여 심박, 호흡을 측정하는 기술개발도 활발히 진행되고 있다 [1]-[3]. 이러한 UWB 전파센서를 구현하는 방법으로 과거에는 개별소자 부품들을 이용 하여 모듈로 제작하는 기술이 주를 이루었으나. 최근에는 CMOS 칩 기술의 발달로 UWB 전파센서를 단일칩에 집적한 사례들이 다 수 발표되고 있다 [1]-[4].

UWB 센서 IC개발은 기존의 RFIC 회로들에 비해 높은 주파수인 3~5GHz 또는 6~10GHz의 광대역 특성을 갖는 RF 회로기술과, 1~2ns 미만의 매우 짧은 임펄스 신호를 고속으로 sampling 할 수 있는 초고속 sample and holder 회로설계 기술을 필요로 한다. 또한, 저전력으로 광대역의 임펄스 신호 발생회로 설계 기술과 전 파센서 IC의 출력신호를 디지털 신호처리부로 보내 clutter 및 잡음을 제거하고 신호를 복원하고 정보를 추출하는 신호처리 기술이 매우 중요하다. 이 글에서는 주로 UWB 전파센서 IC의 회로설계를 중심으로 기술하고자 한다.

#### 본론

UWB 전파센서 기술 및 최근 기술 동향

전파센서라 함은 일반적으로 레이더 기술을 의미한다. 즉 그림 1과 같이 송신된 전자파가 목표물에 반사되어 돌아온 신호를 감지하여 목표물의 거리, 속도 등의 정보를 얻는 기술이다. 전파 레이더는 통신시스템과는 달리 송신된 신호가 목표물에 도달하여 반사된 후 돌아오기까지 발생하는 경로손실이 거리의 4제곱에 반비례하는 특성이 있다. 아래 식 (1)은 레이더 센서에서 수신된 전력의 크기를 구한 것이다. 이는 반사체의 표면적과 RCS(Radar Cross Section)에 비례하며, 주파수의 제곱과 거리의 4제곱에 반비례한다. 따라서, 통신시스템과는 달리 거리에 따른 감쇄가 심하여 원거리의 물체를 탐지하고자 하는 경우 상당히 큰 출력의 송신전력을 필요로 한다. UWB의 경우 규정상 출력신호를 -41.3dBm/MHz의 낮은 수준으로 유지해야 하기 때문에 수신거리가 짧아지는 문제를 가진다. 이외에도 송수신을 동시에 수행하는 경우 송수신의 격리 문제로 송신전력에 한계가 있어 탐지거리가 짧아지는 문제 또한 가지고 있다.

그림 1. UWB 전파센서의 원리 및 시스템 연결도

$$\begin{split} &P_{received} = P_T G_T \Bigg( \frac{\sigma}{4\pi R^2} \Bigg) \Bigg( \frac{A_e}{4\pi R^2} \Bigg) = P_T G_T \Bigg( \frac{\sigma}{4\pi R^2} \Bigg) \Bigg( G_R \frac{\lambda^2}{4\pi} \frac{1}{4\pi R^2} \Bigg) \\ &= P_T G_T G_R \frac{1}{64\pi^3} \frac{\sigma c^2}{f^2} \frac{1}{R^4} = P_T G_T G_R P L_{pathloss} \end{split} \tag{1}$$

$A_e$  = antenna aperture

$\sigma$ =RCS (reflection cross section)

$G_{R_i}G_T = receiver, transmitter antenna gain$

$P_{\scriptscriptstyle T} = transmitted\ power$

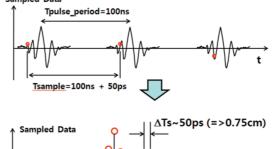

최근 들어 UWB 전파센서를 CMOS 단일칩으로 개발한 사례가 많 이 발표되고 있다. 이를 단일칩으로 구현하기 위해서는 광대역의 RF 회로설계와 센서의 고해상도의 거리 분해능을 얻기 위한 수십 GHz에 해당하는 초고속의 sampling 회로 기술이 필요하다. 먼저 3~5GHz와 6~10GHz의 광대역에서 동작하는 수신부의 경우 과 거 통신용 UWB RF 송수신칩에서 많은 연구가 진행되었는데, 이는 광대역을 위한 수신기 입력정합 기술로는 한계가 있다. 구조로는 3~5GHz 수준의 밴드를 얻기 위한 resistive feedback 구조 LNA 나 common gate를 이용한 noise cancelling을 이용하여 광대역 특성을 구현하고 있다. 또한. 3~10GHz의 초광대역 특성을 얻기 위해 L, C기반의 3차 정합회로를 이용하여 구현한 사례도 있다. 최 근까지 3~5, 6~10GHz의 수신기 회로설계 기술이 많이 발표되고 있으며, 이는 기술적으로 구현에 큰 어려움이 없다. UWB 전파센서 에서 가장 중요한 핵심기술은 초고속의 sampling회로 기술이라 할 수 있다. 일반적으로 1 cm 미만의 고정밀의 해상도를 얻기 위해서 는 15GHz 이상의 고속 sampling이 가능해야 한다. 그러나 CMOS 회로로 15GHz이상의 sampling clock 신호를 저잡음으로 만들기 어렵고, sample & holder 회로의 개발도 매우 어렵다. 특히 이런 회로들이 칩 안에 집적될 때 다른 회로에 치명적인 잡음을 제공해 수신기의 동작이 불가능할 수 있다. 이러한 문제의 해결을 위해 사 용된 기술이 equivalent time sampling 방법이다 [1]. 그림 2는 이 를 설명하는 그림이다. 동일한 임펄스 신호를 반복적으로 송수신하 면서 sampling 시간을 각 임펄스마다 50 ps간격으로 이동하면서 sampling 한 후, 수집된 데이터를 모아서 일렬로 정렬하면 그림 2 의 아래 그림과 같이 50 ps 간격으로 sampling 한 것과 통일한 결과를 얻을 수 있다. 즉, 20 GHz의 고속 sampling한 데이터와 동일한 데이터를 수집할 수 있다. 물론 under sampling의 개념으 로 2000회를 반복해서 송수신해야 하는 단점이 있다. 그러나 임펄 스를 반복하는 시간이 총 200 us가 소요되어 이 시간 동안에는 주 변의 환경변화가 없다는 가정이 가능하여 일반적인 감시정찰 및 탐 지에는 문제가 되지 않는다.

그림 2. Equivalent time sampling의 원리

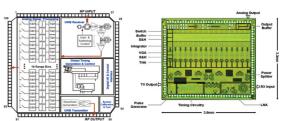

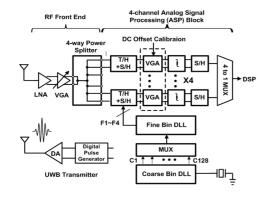

미국의 USC는 위 기술을 이용한 CMOS 단일칩을 2011년 ISSCC 학회에 발표하였으며, 구조와 칩 사진을 그림 3에서 볼 수 있다 [1]. 이 논문에서는 equivalent time sampling 기술 외에도 송수신 임 펄스의 회수를 줄이고자, 16개의 channel을 이용한 time interleaving 기술을 활용하여 16개의 sample을 한번에 얻는 기술을 적용하였다. 각 channel은 순서대로 각각 50 ps 시간차가 나는 clock들을 사용하며, 이들 clock들은 DLL(Delay Locked Loop)을 이용하여 생성한다. 각 channel은 50 ps씩, equivalent time sampling은 800 ps (50ps X 16channel) 씩 시간차가 나는 clock 이 필요하며 이는 모두 DLL 회로를 통해 생성된다. 송신기의 경우일반적인 impulse generator 회로를 사용하며, 수신기부의 경우

광대역 LNA를 통과한 후 수신된 RF신호를 16개의 channel로 배 분하는 RF power splitter를 통과하게 된다. 각 channel은 수신된 임펄스를 50 ps의 간격으로 고속 sampling 하기 위한 track & holder (T/H) 회로를 가지고 있다. 또한, 이를 적분하여 신호대 잡 음비를 개선하고 다시 저속의 S/H를 통해 외부의 ADC로 출력하 게 된다. 본 기술을 통해 논문에서는 심박 및 호흡에 대한 측정을 수행하였다. 본 구조는 16개의 channel에 RF 신호인 임펄스 신호 를 동일하게 배분하는 회로구현이 매우 어렵고, T/H 이후에 발생 한 저주파 신호를 적분하는 과정에서 회로에 발생하는 DC offset 의 문제가 크다. 본 논문에서도 이를 해결하기 위해 각 channel별 로 이득과 DC offset을 통시에 calibration 수행하고 있다. 그러나 이를 충분히 보상하는데 한계가 있어 적분을 충분히 하기 힘들고 원거리의 성능을 얻기 어렵다. 2011년 ISSCC에 동시 발표된 UWB 전파센서 칩으로 90nm CMOS공정 개발하여 호흡측정을 수행한 칩의 구조와 실험 결과를 그림 4에서 보여주고 있다 [2]. 본 논문에 서 채택한 구조는 고속의 T/H를 이용한 구조가 아닌 송수신된 임 펄스를 multiplier에서 곱하고 envelope 신호를 추출하여 탐지하 는 방식이다.

그림 3. ISSCC 2011에 발표된 USC의 UWB impulse radio CMOS sensor 칩

그림 4. ISSCC 2011에 발표된 90nm CMOS UWB 전파센서의 호흡측정

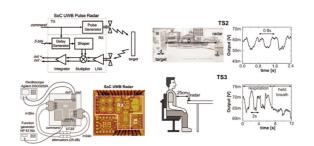

이 구조는 고속의 T/H가 필요 없고 논문에서는 출력을 오실로스코 프로 확인하였으나, 실제 시스템으로 구현시 초고속의 sampling을 외부의 ADC에서 수행해야 한다. 이 구조는 DC offset 등의 문제 가 없는 장점이 있으나, multiplier 회로 내의 큰 잡음으로 인해 SNR이 좋지 않을 수 있어 감지 가능한 거리가 제약된다. 본 논문 에서는 1~2m 수준에서 심박을 측정하는 결과를 보여주고 있다. 2 개의 논문 이후에 단일칩으로 구현된 논문들이 일부 발표되었으나 구조나 원리는 위의 2가지 논문 중 하나의 구조와 유사한 형태이므 로 생략한다. 이 외 실제 제품으로 노르웨이의 Novelda사에서 UWB 전파센서 단일칩을 제품으로 출시한 X2M1000 사례가 그림 5에 나와 있다 [3]. 이는 ADC를 UWB 센서칩 내에 집적하였고 6-8.5GHz에서 통작하며. 1mm 이하의 정밀도로 심박 및 호흡 측정 까지 가능하다. 또한, 초고속 sampling을 위해 digital interleaved sample 방식을 사용하여 등가적으로 39 GHz의 초고속 sampling 된 데이터를 얻을 수 있다. 최대 감지거리는 4~5m내외이며, 전력 소모는 350mA@2.8V이다. 이 외에도 오랫동안 UWB 전파센서 제 품을 출시한 미국의 Time Domain사 및 McEwan사 등이 있으나. 이는 멀티칩이거나 개별부품으로 개발된 모듈제품이다.

그림 5. 노르웨이 Novelda사(XETHRU)가 개발한 UWB 센서 단일칩 기반 X2M1000 제품의 사진

#### CMOS UWB 전파센서 단일칩 회로설계 및 응용 사례

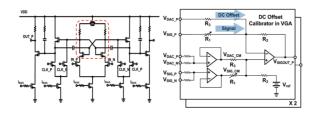

UWB 전파센서의 구체적인 회로 및 칩 개발 사례에 대해 좀 더 자 세히 기술하고자 한다 [4]. 아래 그림 6은 앞서 언급한 USC에서 개발한 equivalent time sampling 기술과 multi-channel을 이용 한 time interleaved 기술을 적용한 UWB 전파센서 개발 사례이 다. 그림에서 LNA는 3~5GHz의 광대역의 특성을 얻기 위해 active feedback을 이용한 광대역 회로를 채용했다 [5]. 또한, 이득 가변이 가능한 RF VGA가 있다. 이후 inductive shunt peaking 을 이용한 4-channel의 RF power splitter 회로를 이용하여 각 channel에 균일한 전력을 배분한다. 이 때 인덕터 및 4-channel 로 나뉘는 배선은 EM simulation을 통해 회로설계에 반영하였다. 또한, 고속의 임펄스 신호를 track & hold하는 T/H 회로는 아래 그림 7좌측에 보여지는 바와 같이 고주파 특성을 확장하기 위해 shunt peaking과 cross coupled feedback 구조를 사용하였다 [6]. 이후 T/H에서 감지된 신호를 아날로그 VGA와 적분기로 증폭 하고 신호대 잡음비 (SNR)을 개선해야 하는데, base band analog 회로에서 이득이 큰 경우 DC offset에 의한 SNR의 열화 및 saturation 되는 현상이 있다. 이를 위해 DC offset을 제거하는 회로 가 필요하게 되면, 그림7 우측에 보여진 바와 같이 DAC와 opamp를 이용한다. DC offset을 반대로 인가하여 제거할 수 있는 calibration 회로를 삽입하여 DC offset 보정을 할 수 있다. 이를 통해 DC offset이 감소하면 VGA와 적분이 이득을 높일 수 있고, 탐지거리를 확장할 수가 있다.

그림 6. CMOS UWB 전파센서칩의 송수신기 구조

그림 7. 고속의 Track and Holder(좌측)와 DC offset 보정회로(우측)

14 | CMOS UWB 전파센서 단일칩 기술 및 응용분야

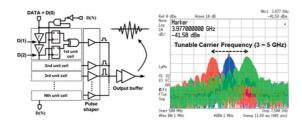

UWB 전파센서용 송신기 회로의 경우 임펄스의 생성을 위한 회로 구조로 switched VCO기반의 임펄스 생성기와, 디지털적으로 개 별 펄스를 만들어 조합하는 디지털 방식이 있다. 여기서는 전력소 모가 적고 reconfigurable한 digitally synthesized impulse generator를 사용하였다. 아래 그림 8의 좌측은 디지털 임펄스 생성기 의 회로를 보여준다. 작은 시간 delay au 의 지연된 신호들을 inverter로 만들어 내고, 이들을 D flip-flop과 EXOR를 이용하여 시 간차가 있는 단위 펄스를 생성한 후, 크기의 weighting을 두어 합 함으로써 전체 임펄스를 만들어 내는 방식이다. 그림 8의 우측은 송신기의 출력 spectrum을 보여주고 있다. 이는 디지털 방식으로 tunability를 가지고 있어 중심주파수를 3.5~4.5GHz까지 조절이 가능하며, bandwidth도 500 MHz에서 2 GHz까지 자유로운 조절 이 가능하다. 개발된 IC는 그림 9의 우측과 같이 모듈로 개발되어 거리에 따른 수신된 탐지 신호의 모양을 보여주고 있다. 이는 2.5m, 4.5m 거리에 대해 케이블과 감쇄기로 channel을 모사하여 측정한 것이다. 개발된 칩은 이후 성능개선과 ADC 내장형으로 개발되었 고. 디지털 FPGA와 연통이 가능하도록 하였다. 아래 그림 10은 UWB 전파 센서칩을 이용하여 개발된 UWB 센서모듈과 사람의 거 리를 탐지하는 사진을 보여준다. 안테나는 일반적인 patch antenna를 이용하였다.

그림 8. 디지털 방식의 임펄스 발생기 구조도와 측정된 임펄스의 spectrum 특성

그림 9. UWB 전파센서칩을 활용한 센서보드 및 거리 탐지 측정결과

그림 10. 개발된 UWB 전파센서칩 기반 센서모듈과 사람의

#### 결론

이 글에서는 고해상도의 임펄스를 이용한 UWB 전파센서의 원리와 동향을 살펴보았다. 또한. 최근 CMOS 단일칩화 기술로 UWB 센 서를 단일칩화 한 사례들을 보여주었다. 최근 국방분야에서는 감시 GPR See Thru Wall 분야 등에서 UWB 센서를 사용하고 있으며. 기존의 개별부품 기반의 모듈에서 소형화와 저전력을 위해 단일칩 화 해야 할 필요성이 대두되고 있다. 이는 민간분야 보안에 이미 사 용되고 있으며, TV나 에어컨 같은 가전에서 사람의 탐지 및 실내 의 인원수를 카운트하는 응용기술로 관심이 높은 상태이다. 기존의 개별부품으로 크기가 크고 전력소모도 많은 반면, UWB 센서는 단 일칩화를 통해 제어가 용이하고 소형화, 저전력이 가능하여 응용분 야도 늘어나고 있는 추세이다. 하지만 UWB 전파센서 기술은 IC 단 일의 성능보다는 신호처리와 안테나. 전파채널과도 상당히 영향을 많이 받고 연동하여 성능을 측정해야 하므로 전체적인 시스템에 대 한 충분한 이해와 경험이 개발의 필수요소라고 볼 수 있다.

어 윤 성 교수

소속 : 광운대학교 전자공학과 RF Circuit And System Lab 주 연구분야: RF Transceiver IC, UWB/FMCW Radar Sensor IC, F/Analog Circuit Design -mail: yseo71@kw.ac.k lomepage: http://cms.kw.ac.kr/rfcas/index.htm

정 승 환 수석(Ph.D) 소속 : 실리콘알엔디 연구소 팀장 주 연구분야 : RF Transceiver IC, UWB/FMCW Radar Sensor IC mail: seunghwan, jung@sirnd, com menage: http://www.sirnd.com/

#### 참고문헌

- [1] T. Chu, J. Roderick, S. Chang, T. Mercer, C. Du, H. Hashemi, "A short-range UWB impulse-radio CMOS sensor for human feature detection", IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 294-296, Feb. 2011.

- [2] D. Zito, D. Pepe, M. Mincica, and F. Zito, "A 90nm CMOS SoC UWB Pulse Radar for Respiratory Rate Monitoring", IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, pp. 40-41, Feb. 2011.

- [3] https://www.xethru.com/

- [4] S. Jung, J. Ha, H. Yoo, C. Cheong, Y. Chun, W. Kim, and Y. Eo, "A 3-5 GHz Fully Integrated CMOS UWB Radar Chip", Radar Conference (EuRAD), pp. 57-60. Oct. 2013

- [5] J. Borremans, P. Wambacq, C. Soens, Y. Rolain, and M. Kuijk, "Low-area active-feedback low-noise amplifier design in scaled digital CMOS", IEEE J. Solid-State Circuits, vol.43, no.11, pp.2422-2432, Nov. 2008

- [6] T. Sato, S. Takagi, N. Fujii, Y. Hashimoto, K. Sakata , H. Okada, "4-Gb/s track and hold circuit using parasitic capacitance canceller", Eur. Solid-State Circuits Conf. (ESSCIRC), pp. 347-350, Sept. 2004

# 모바일과웨어러블애플리케이션의고해상도이미지를 위한최적의 DSP

#### 개요

모바일과 웨어러블 응용분야에서 고해상도 컴퓨터 비전 응용 프로 그램의 성능을 크게 향상 시킬 수 있는 좋은 기회가 있다. 차세대 DSP는 전력소모와 성능 사이에서 이상적인 조화가 요구된다. 이 글에서는 모바일과 웨어러블 응용분야에서 이상적인 DSP를 선정 하기 위해 고려해야 하는 부분에 대해서 논의할 것이다.

#### 소개

코닥의 엔지니어인 Steve Sasson이 1975년에 첫 번째 디지털 카메라를 발표함으로써 우리에게 새로운 지평을 열어주었다. 그때는 누가 상상이나 했겠는가? 지금처럼 이렇게 해상도가 좋아지고 어디에서나 사진을 볼 수 있게 될 지를. 오늘날 우리는 스마트폰에서 고해상도의 이미지를 이용하여 얼굴을 찾아내고, 보안 시스템에서 얼굴을 인식하며, 자동차에서 교통신호를 인식하고 있다. 미래에는 자율 주행을 하게 될 것이다.

Yole Development에 따르면, CMOS 이미지 센서 산업은 2020년까지 연평균 성장률이 10.6%씩 상승하여 전체 시장규모가 US\$16.2B 이를 것으로 전망하고 있다. 스마트폰이 시장의 대부분을 차지하고 있으며, 자동차, 의료 및 감시 카메라 시장 역시 기회가 있다. 기술적인 측면에서는 카메라 모듈의 height와 픽셀 사이즈가 한계에 이르고 있다. 새로운 센서 기술의 변화 속도와 함께 가능한 최상의 화질을 만들어내는 특별한 이미지 처리 방법이 요구된다.

전자 시스템에서는 ISP 파이프라인 이미지와 비전 처리 알고리즘을 구현하기 위해 CPU 나 GPU, 전용 하드웨어 블록 등의 조합을 사용한다. 왜냐하면 센서 기술이 급격히 발전하고 다양한 제품이 개발되어, RTL 설계를 통한 전용 하드웨어 개발은 점점 힘들어 지고 있기 때문이다.

우리는 32Mpixel이나 그 이상의 이미지 또는 비전 처리와 관련하여 좀더 실행 가능한 방법에 대해 논의할 것이다. 특별히 디자인된 DSP를 이용함으로써, 최적의 DSP를 선택함으로써, 당신은 성능과 전력의 저하 없이 컴퓨터 비전을 처리할 수 있다.

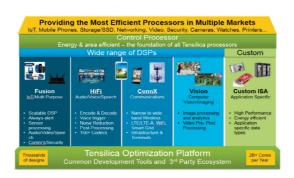

\* 참조: Tensilica Scalable Product Portfolio

#### 전력 소모와 성능의 난제를 해결하기

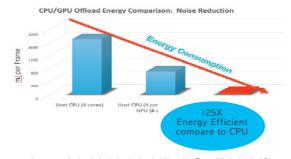

CPU/GPU를 사용하는 방법은 유연성이 높으나, 가장 큰 문제는 성능과 전력 소모의 트레이드오프(tradeoff)이다. 그림 1에 보이는 것과 같이 요구된 이미지나 비전 처리 알고리즘을 CPU/GPU에서 수행하게 되면, 전력소모에 큰 부담을 준다. 게다가 웨어러블 디바이스라면 CPU/GPU 방식은 배터리 수명에 영향을 주게 되고, 발열의 원인이 될 것이다. (또한, CPU/GPU의 속도저하가 빈번하게 발생할 것이다.) 특히, 화상 통화와 같은 경우에는 상당한 전력을 소모하게 될 것이다.

그림1. DSP에서 이미지나 비전 처리를 기능을 수행하면 상당한 에너지 절감을 가져온다.

또 다른 방법인 RTL을 이용하는 전용 하드웨어를 이용하면, 전력 소모 면에서는 상당한 이점은 있지만 유연성에 한계가 있다. 이러 한 방법은 오랜 설계 기간과 검증과정이 요구되며, 각각 기능별로 구현되어야 한다. 이는 새로운 기능을 추가하거나 알고리즘을 개선 하기가 어렵다. 심지어는 새로운 칩을 설계해야만 한다.

특별히 설계된 DSP는 성능과 전력소모 사이의 조화를 제공한다. DSP에서 사용되는 연산장치들은 여러가지 알고리즘에 공통적으로 사용될 수 있다.

#### DSP는 어떤 컴퓨터 비전 응용 프로그램을 지원 할 수 있을까?

컴퓨터 비전(인간의 시각 능력을 모방하여 전기적으로 인식되거나 이해된 이미지)은 웨어러블 장치뿐 아니라 자동차나 무인항공기의 응용 프로그램에 일반적으로 사용된다. 오늘날의 소비자들이 사용하는 기기인 컴퓨터 비전은 저전력(더 긴 배터리 수명을 위해서),고성능의 필수적인 응용 프로그램이 사용된다.

이러한 용도로 카메라 처리 시스템은 두가지 구성요소(이미지 처리 및 비전 처리)로 구성되어 있는데, 각각의 요구 사항들이 존재한다.

#### 이미지 처리

- •작은 픽셀 크기에 대응하기 위해 정교한 노이즈 감소

- 비디오 이미지 안정화 기능

- •고속 자동 초점 기능

- ·하이 다이나믹 레인지 (HDR)

- 같은 장치에 듀얼 카메라 지원

- 와이드 다이나믹 레인지 (WDR), 디지털 비디오 안정화 및 여러 고급 노이즈 저감 방법 지원

#### 비전 처리

- 얼굴 검출을 표준 비디오 그래픽 어레이 (VGA) 수준에서 720까지의 해상도를 가지고 있음

- 사람과 물체 검출

- 제스처 추적

- · 안구 추적 기능

- 모션 감지

- 회선 신경망 (CNN)

지속적으로 증가하는 해상도는 높은 대역폭을 요구한다. 오늘날의 스마트폰은 16MP을 제공하지만, 향후에는 24MP 또는 32MP의 높 은 해상도를 가질 것으로 예상된다. 마찬가지로 스마트폰에서 이미 1080p 비디오를 제공하고 있지만, 결국에는 4K해상도에서 120fps 로 지원하는 방향으로 이동하게 될 것이다.

이런 유형의 이미지 처리 및 비전 처리 기능과 메모리 대역폭의 요구는 비전 DSP의 핵심이다. 결국 광학 센서 및 알고리즘은 항상 변하고 있다. 이러한 고해상도 이미지 및 비전 처리 기능 및 메모리 대역폭 요구를 지원하는 다양한 기능을 가진 유연한 컴퓨터 비전 DSP가 필요하다.

- ·얼굴 인식, 제스쳐 인식, 움직임 인식, 이미지 안정화, HDR WDR, 2D/3D 노이즈 감소와 같은 다양한 알고리즘

- ·하나의 DSP가 디자인 요구사항이 달라질 수 있는 다수의 클라 이언트 애플리케이션을 지원할 수 있는 programmability

- •고사양. 저전력 소모

- Bayer domain의 ISP processing path안에서 배치될 수 있는 능력, 이는 노이즈 감소와 HDR과 같은 기능들을 지원하거나 새 로운 유형의 센서들(예를 들면, IR 센서들 혹은 R, G, B, IR 픽셀 의 혼합을 감지하는 센서들)을 지원함

- · 작은 폼팩터 (form factor)

이러한 DSP를 개발하는 것은 매우 고급 개발 도구 및 고도로 최적 화 된 이미지와 비전 라이브러리가 사용된다. 일부 응용 프로그램 에서는 정확한 계산을 필요로 하기 때문에, 벡터 부동 소수점 연산 을 수행 할 수 있도록 해야 할 것이다.

#### 새로운 이미징 및 비전 처리 DSP

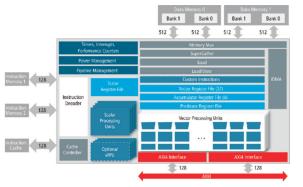

케이던스의 Tensilica® Vision P5는 이미징 및 비전 처리 애플리 케이션을 위해 특별히 설계된 프로세서의 예이다. 그림 2는 아키텍 처와 제4세대 Vision DSP의 중요한 특징을 보여준다.

그림2. Tensilica Vision P5 아키텍쳐

Tensilica<sup>®</sup> Vision P5는 영상 처리 및 분석을 위한 이상적인 기능뿐만 아니라 영상 전처리 및 후 처리 기능을 제공한다.

- 이전 세대 Tensilica IVP-EP DSP를 넘어서는 vision perfor mance에서의 델타 함수 (step function)

- 64-way SIMD 엔진

- · SuperGather™<sup>®</sup> 기술과 함께하는 1024-bit 메모리 인터페이스

- 32-bit data types를 위한 풍부한 지원

- · 더 고사양을 위한 고객화 (customizable)

• 필터링, 사물 인식, 옵티컬 플로우 (optical flow) 를 위한 이미징 /비전 커널 (kernels) 뿐만 아니라 많은 수의 OpenCV와 OpenVX library 기능들을 지원

• 멀티 프로세서 준비

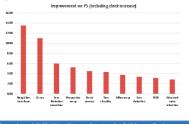

변경이 가능한 Cadence/Tensilica Xtensa 프로세서로 개발된 Tensilica Vision P5는 로컬 및 시스템 메모리 사이에서 높은 대 역폭과 전송률을 지원하는 2D iDMA를 가지고 있다. 또한, 차량용 인증을 위한 ECC(오류 정정 코드) 지원 및 벡터부동소수점 유닛 및 AMBA AXI4를 지원한다. 그림 3에서 볼 수 있듯 Vision P5는 이전 세대 DSP에 비하여 상당히 향상된 성능을 제공한다.

### Vision P5 performance increase over IVP-EP

그림3. 이전 세대 DSP 대 Tensilica Vision P5의 성능 향상

#### 사용 사례

일본 도쿄에 위치한 이미지 처리 전문 기업인 Morpho, Inc.는 단 일 이미지 기반의 휘도 향상 기술을 적용하기 위해, 예전 세대의 Tensilica image/vision DSP를 사용했었다. 비디오 WDR를 DSP 에 포팅함으로써 이전의 CPU 기반의 솔루션에 비해 8배의 성능향 상을 달성했다. 그림 4에서 나타낸 바와 같이 1080p@30fps를 지 원하기 위해서 CPU에서는 2.2Ghz 가 요구되지만, DSP에서는 282Mhz면 충분하다. Vision P5는 이전 세대에 비하여 응용프로 그램 수준에서 2x - 4x 성능을 제공하기 때문에 70Mhz 이하가 될 것이다.

그림4. Morph는 Tensilica DSP 기술로 전환 한 후 그 비디오 WDR 응용 프로그램의 대폭적인 성능 향상을 달성했다.

#### 요약

컴퓨터 비전 알고리즘을 구현하기 위해 CPU/GPU를 조합하는 방 식은 일반적인 방법이지만, 특히 모바일 및 웨어러블 응용 프로그 램에서는 전력소비에 있어 한계가 있다. 이와 대조적으로 Tensilica Vision P5는 이미지 및 비전 처리에서 높은 처리능력을 제공하면 서 실직적인 에너지 소비를 절감 할 수 있다.

cādence

회사명: Cadence

웹 주 소: http://www.cadence.com/ 한국지사: 경기도 성남시 분당구 판교로 344 엠텍IT타워 9층

전 화:031)728-3114 Email: korea\_crc@cadence.com

# 선거 편리한 생활에 한발짝 다가가다〉

이 윤 명 교수 성균관대학교 반도체시스템공학과

인터넷과 연결된 사물이 컴퓨터 하나이던 시대는 지나갔다. 멀리 떨어진 사람과 음성을 주고받을 수 있다는 사실만으로도 사용자에게 만족을 주던 전화기는 이제 인터넷과 연결된 스마트폰으로 진화하여 우리의 일상 곳곳에 투과한 지 오래이다. 대표적 일상공간인 거실 안의 TV는 시청자의 프로그램 패턴을 스스로 분석하여 본인에게 맞는 컨텐츠를 제공한다. 운동 중 스포츠밴드를 신체에 장착하면 심박수, 소모 칼로리, 운동 거리와 경로 등을 파악할 수 있어 체계적인 건강관리가 가능하다. 이처럼 앞으로 더 많은 기기들이 인터넷과 연결되어 인간의 생활을 놀랍게 향상시킬 것이다.

loT(Internet of Thing, 사물 인터넷)라는 용어로 통용되어 일컬어지는 이 기술은 다양한 방식으로 정의되어 왔으며, 이 기술은 세대를 거쳐 변화하고 있다. 그러나 이러한 IoT가 현실에 정착되기 위해서는 해결해야 할 수많은 과제들이 남아있다. 이에 관심을 가지고 저전력 회로 설계 분야에서 끊임없이 연구하는 성균관대학교 반도체시스템공학과의 이윤명 교수를 만나보았다.

#### 저전력 회로 설계의 시작

이윤명 교수는 IoT 기술 전개에 근간이 되는 저전력 회로 설계와 관련한 연구를 시작하게 된 계기를 밝혔다. "많은 학생들이 전공분야를 선택함에 있어서 특별한 계기가 있었는지에 대해 궁금해 합니다. 사실 학부과정을 갓 마친 수준에서 어떠한 연구주제가 의미 있고 달성 가능한지를 가능하는 안목을 가지는 것은 쉽지 않은 일입니다. 저 또한 학부과정 중 실습을 통해 전자 회로나디지털 시스템 설계 관련 분야에 대한 막연한 흥미를 시작으로 대학원 진학 후 디지털·아날로그 회로 설계를 구체적인 전공 분야로 결정하게 되었습니다."

이윤명 교수는 회로 설계를 시작하게 된 또 다른 계기로 지도교수님에 대한 이야기를 늘어놓았다. "석사과정 중 만난 지도교수님의 제안을 통해 저전력 회로 설계 분야에 대한 연구를 진행하게 되었습니다. 지도교수님을 학문적으로, 인격적으로 존경하여 그분의 가이드를 충실히 따른 덕분에 좋은 연구성과를 낼 수 있었던 것 같습니다."

#### 더 작게, 더 세밀하게

이러한 이윤명 교수의 연구 활동은 수  $mm^3$  크기의 초소형 센서 시스템을 구현하기 위해 다양한 회로를 초저전력으로 설계하는 연구를 시작으로 진행되었다고 한다. "IoT의 시대가 도래하면서 점점 더 다양한 전자기기들이 더 작은 크기로 설계되고 있습니다. 이러한 추세가 계속되면 궁극적으로 어떠한 기술이 필요할지를 연구했습니다. 초소형 시스템 구현에 필수적인 배터리 부피 축소를 위해서는 각 구성요소들의 소비전력을  $\mu$  W 이하의 수준으로 낮추어야 합니다. 이를 위해 새로운 회로 설계 기법을 도입하여 저전력 마이크로프로세서, 메모리, 타이머 등 각종 센서들을 설계하였고, 이들을 이용하여 하나의 완성된 센서 플랫폼을 제작·발표했습니다."

이윤명 교수는 박사과정을 회고하며 가장 인상 깊었던 연구활동에 대한 이야기도 잊지 않았다. "특히 mm<sup>3</sup> 크기의 센서 플랫폼을 만드는 연구를 진행했던 일련의 과정들이 기억에 남습니다. 이전까지 진행했던 연구를 넘어 하나의 플랫폼을 설계하고 시제품으로 만들기 위한 패키징 제작 과정까지 신경 써야했던 매우 부담스러운 프로젝트였습니다. 그러나 지도교수님의 끊임없는 격 려와 아낌없는 물적, 시간적, 인적 지원 덕분에 세계 최초로 1mm<sup>3</sup> 크기의 초소형 센서 시스템을 발표할 수 있었습니다. 이후 후배들에게 큰도움이 될 수 있었다는 사실과, 리더의 지지 그리고 이를 신뢰하는 멤버들과 좋은 결과를 낼 수 있다는 깨달음에 큰 보람을 느꼈습니다."

현재 이윤명 교수는 초소형·초저전력 센서 플랫폼에서 사용할 수 있는 각종 기능을 구현하는 연구를 진행하고 있다. 1nW의 매우 작은 에 너지원에서도 효율적으로 에너지를 포집할 수 있는 초저전력 에너지하베스터와, 적은 소비전력에서도 출력전압의 미세 조정이 가능한 DC-DC전압 변환기 설계를 연구 중이다. 이밖에도 저전력으로 동작할수 있는 Physically Uncloneable Functions(PUF)와, Piezoelectric energy harvester을 연구 중이다.

#### 반도체 산업의 성장동력이 될 IoT 기술

이윤명 교수는 최근까지 반도체 산업의 성장동력이 휴대폰이었다고 한다면, 앞으로는 IoT 기술이 중요하게 자리잡을 것이라고 말한다. "현재반도체 산업에서 IoT, 웨어러블 및 이식용 기기에 대한 관심이 증가하고 있습니다. 다양한 전자기기가 더 작게 만들어질 것이기 때문에, 저전력 회로 설계의 중요성은 더욱 부각될 것이라고 생각합니다. 저 또한 좀 더 복잡한 단위의 디지털 회로를 저전력으로 구현하는 연구에조금씩 관심을 가지고 있습니다. 특히 빅데이터 분석이나 인공지능에 대한 연구가 활발히 진행되면서, 이와 관련된 알고리즘을 기존의 프로세서보다 높은 효율로 구현해주는 회로에 대한 관심이 많아지고 있습니다. 이러한 측면에서도 저전력 회로 설계자들일 담당해야 할 역할이 매우 많을 것으로 생각합니다."

반도체 산업의 성장동력이 IoT 기술이라면, 연구자로서의 성장동력은 무엇이냐는 질문에 이윤명 교수는 다음과 같이 말했다. "박사과정 중 연구주제와 직접적으로 관련이 없는 분야의 논문이나 저널을 많이 찾아보지 못했습니다. 그러나 핵심적인 문제해결의 아이디어는 무심코 읽어보았던 타 분야의 연구결과에서 얻게 되는 경우가 많았습니다. 아날로그 아이디어를 디지털에 적용하고, 디지털 아이디어를 이날로그에 적용하는 것만으로도 의미있는 새로운 시도를 많이 할 수 있었습니다. 다양한 분야의 글을 읽는 것이 문제해결에 큰 도움이 되고, 새로운 영감을 얻을 수 있다는 측면에서 전공분야를 넓게 볼 수 있는 여유를 가지는 것이 연구자로서의 성장동력 중 하나가 아닐까 생각합니다."

새로운 세계에 대한 탐험을 통해 시행착오와 경험을 스스로 거치고, 분야의 모든 종사자에게 쉽게 나아갈 길을 제시하고 도와주는 것이 학자로서의 기쁨이라 여기며 연구에 매진하고 있는 이윤명 교수, 그가 새로운 시장을 개척하여 산업계에 기여할 수 있는 날이 오기를 기대해본다.

· 문의: 성균관대학교 반도체시스템공학과 IC & System Design Lab.

· 전화: 031-290-7979

· E-mail: yoonmyung@skku.edu

· Homepage: http://sites.google.com/site/icasskku/