## **High-Resolution Correlated Double Sampling Technique**

# for High-Density Subretinal Implant

Jong Gi Hong<sup>1</sup>, Yeon Ji Oh<sup>2</sup> and Jung Suk Kim<sup>1</sup>

<sup>1</sup>Gachon University, Korea <sup>2</sup> Korea University, Korea

### Introduction

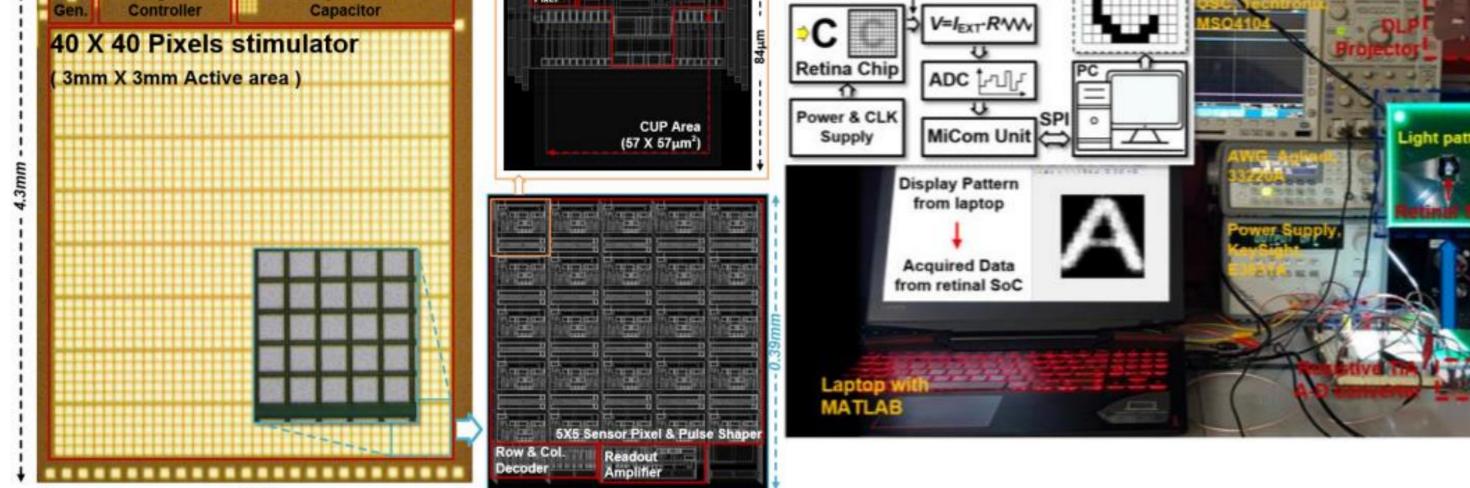

This paper presents a 1,600-pixel integrated neural stimulator with a correlated double sampling readout (DSR) circuit for a subretinal prosthesis. The retinal stimulation chip inserted beneath photoreceptor layer is consisted with an array of active pixel sensor (APS) and biphasic pulse shaper. The experimental result shows that the proposed high-density stimulation array chip can accomplish high temporal resolution due to low integration time condition. The 1600-pixel retinal chip is designed and fabricated using a DB-HiTeK 0.18µm standard process.

#### **Block Schematic Architecture**

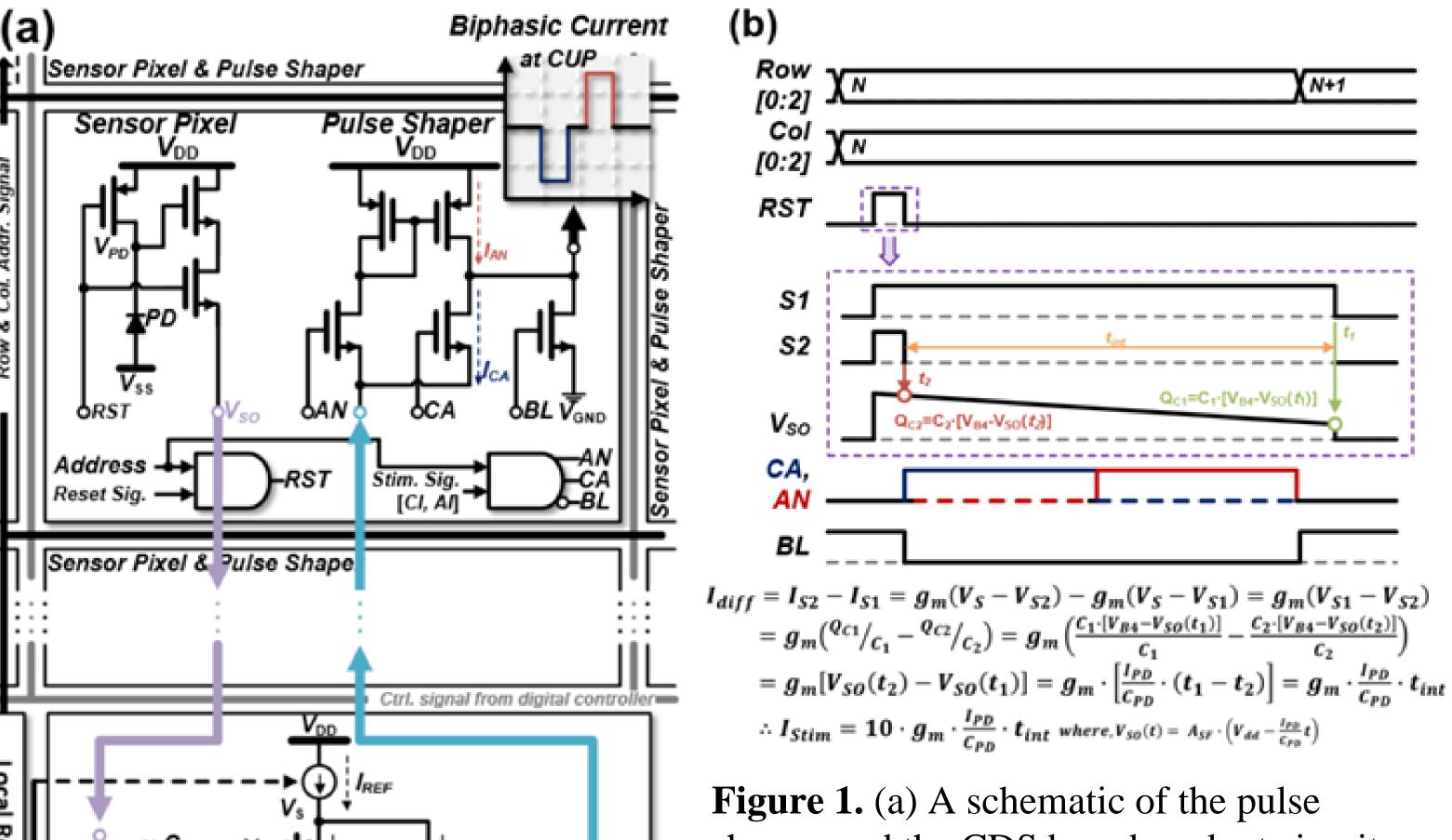

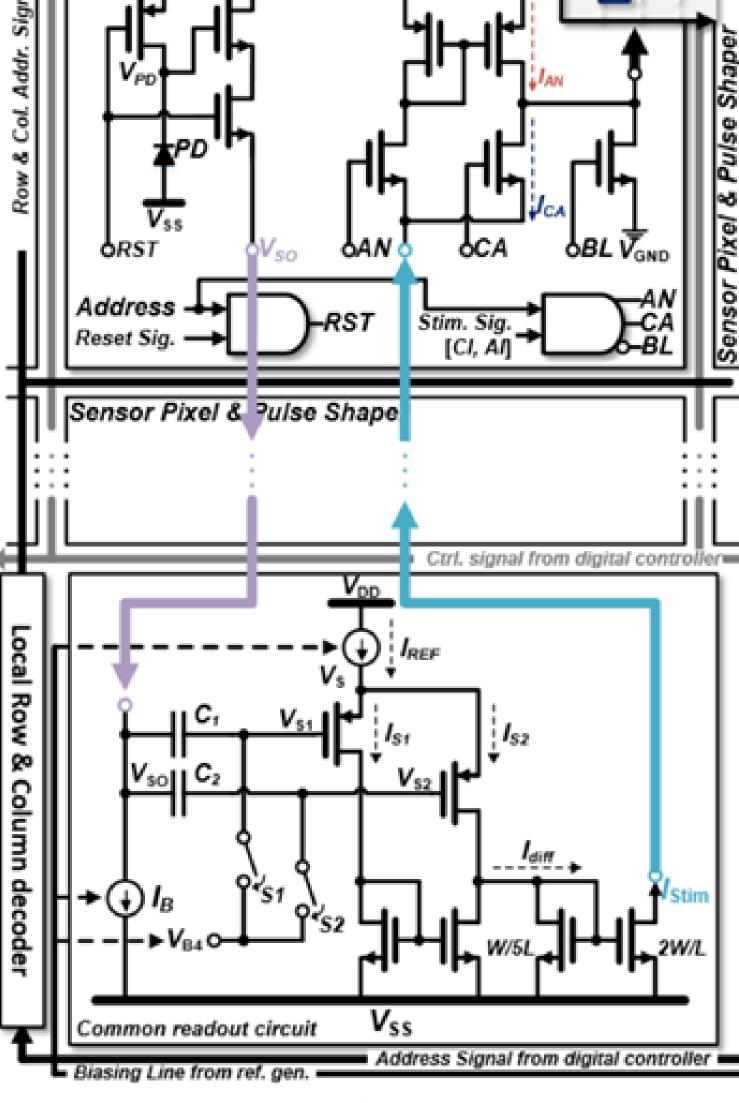

Fig. 1a shows schematics of the sensor pixel pulse shaper (SPPS) and the DSR circuit with address decoders. The address decoder determines which of SPPS is selected to connect with the DSR circuit, and is repeated after 25 sequences for cycling SPPSs. Fig. 1b illustrates a timing diagram of the SPPS and the DSR circuit in particular sequence of the cycle.

### **Experimental Results**

|                 |                          | This Work         | TBioCas'20[1]      | TBioCas'21[2]         |

|-----------------|--------------------------|-------------------|--------------------|-----------------------|

| Sensor<br>Pixel | APS                      | 3Tr-APS           | FPM                | PWM                   |

|                 | Pwr/Ch                   | 1.98µW            | 56.3nW             | 4.49nW                |

|                 | Cur.Dev                  | $\leq 0.63 \mu A$ | $\leq 3\mu A$      | ≤6.175µA              |

|                 | Pwr. <sub>MAX</sub> /Ch. | 10.8µW            | 1.45µW             | 4.28µW                |

|                 | Comp. V                  | ± 2.35V           | ± 1.6V             | 1V                    |

| Pulse<br>Shaper | I <sub>STIM</sub>        | $\leq 60 \mu A$   | $\leq 1 \text{mA}$ | $\leq 95 \mu A$       |

|                 | t <sub>STIM</sub>        | ≥ 1.152ms         | _                  | $\leq 15 \mathrm{ms}$ |

shaper, and the CDS based readout circuit, which collaborated address signals from the digital controller, and bias from the reference generator. (b) A timing diagram on particular sequence that connected with the SPPS pixel; A I<sub>STIM</sub>, a stimulus current amplitude is defined with a following equation under its timing diagram

|      | Cur. Dev.  | $\leq 0.51 \mu A$             | _                            | $\leq 0.475 \mu A$              |

|------|------------|-------------------------------|------------------------------|---------------------------------|

| Area | Pixel Size | 84× 80.3µm <sup>2</sup>       | 84× 86.6µm²                  | 90× 60µm²                       |

|      | Total Size | $4.3 \times 3.3 \text{ mm}^2$ | $5 \times 3.45 \text{ mm}^2$ | $2.93 \times 2.55 \text{ mm}^2$ |

#### **Table 1**. Performance of proposed system

#### Conclusion

This paper presents high-temporal and highspatial resolution neural stimulator to achieve nonflicker and high-resolution visual restoration. The proposed retina chip with 1600 stimulation pixels is implemented with the DSR circuit that works to recognize a light intensity in short integration time. In addition, with considering the mismatch on the Monte-Carlo simulation, the retina chip attains smallest standard deviation of the current output compared with conventional retina chips.

#### Acknowledgement

Figure 2. A microscopic image of the retina chip

**Figure 3.** A demonstration bench for the proposed retina chip,

The chip fabrication and EDA tool were supported by the IC Design Education Center(IDEC), Korea.

반도체설계교육센터