# **Precharge-Controlled 4T1C eDRAM Macro for Reconfigurable Digital Compute-in-Memory with Dual Multiplication Modes**

Ho-Sung Lee, Ik-Hyeon Jeon, Jiwon Lee, Eun-Bi Koh, and Joo-Hyung Chae Department of Electronics and Communications Engineering, Kwangwoon University

## Introduction

- Edge AI demands energy-efficient and reconfigurable CIM architectures.

- Conventional CIM lacks adaptability due to fixed bit-

widths and restricted logic operations.

- To overcome these limitations, we propose a precharge-controlled 4T1C eDRAM-based DCIM macro with dual-mode (AND/XNOR) multiplication and reconfigurable INT1-8 MAC operations.

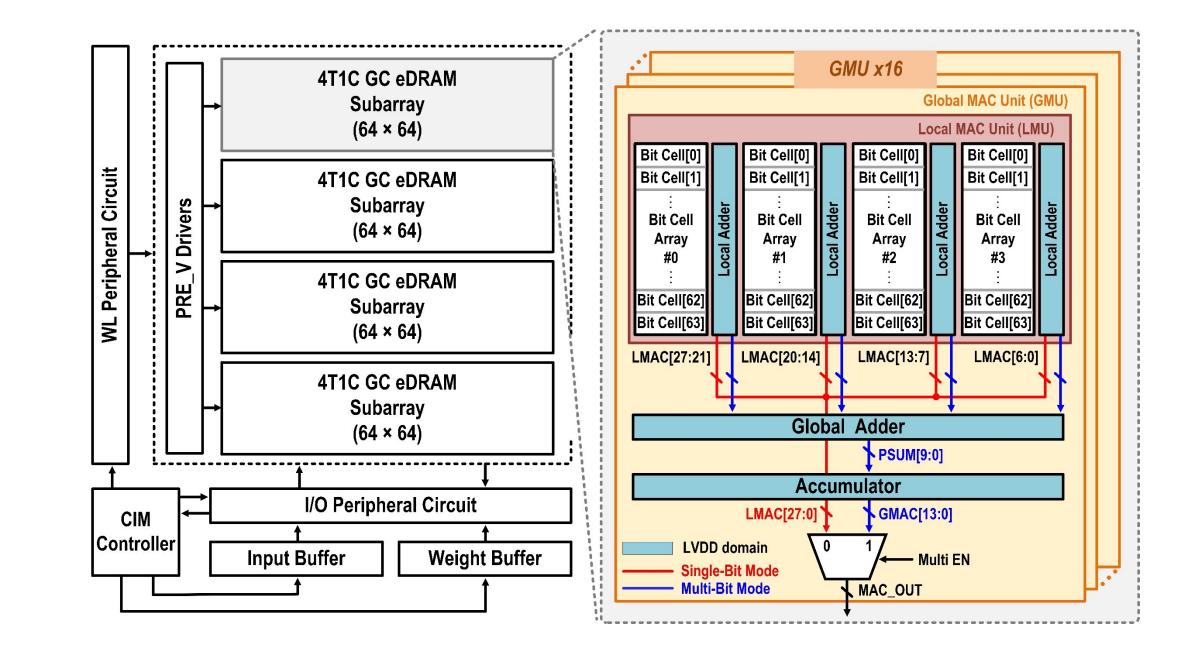

#### **Overall Architecture**

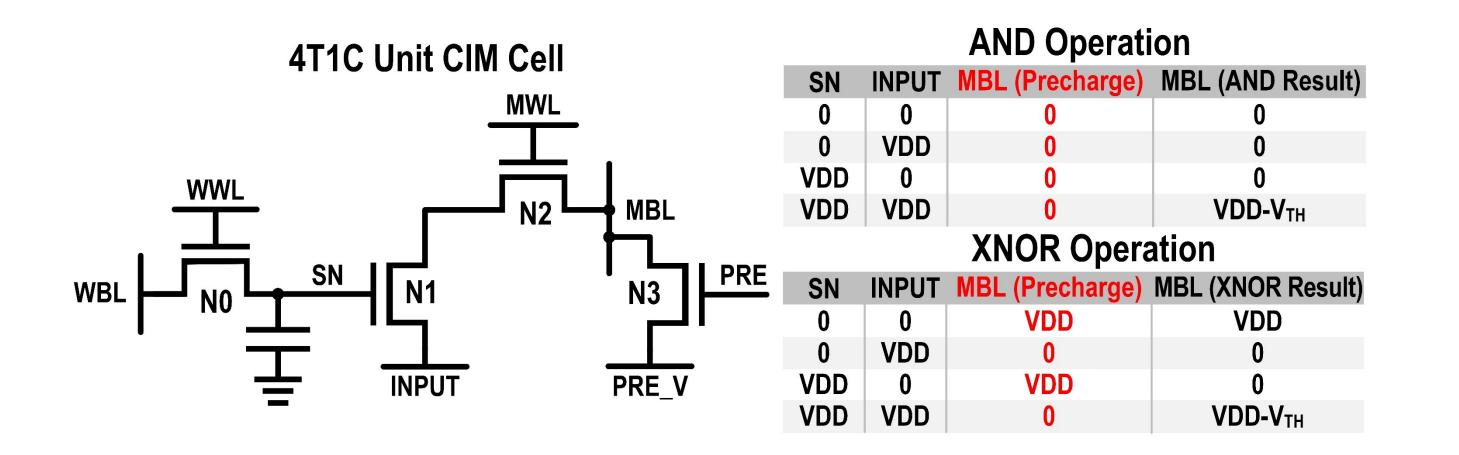

- The proposed 4T1C eDRAM cell supports both AND and XNOR operations through precharge control, enabling <u>dual-mode</u> multiplication in a single cell.

- A custom MOMCAP enhances data retention without increasing cell area.

- The 16Kb macro performs efficient MAC operations using <u>bit-</u> serial processing and shared adder structures.

- A 15:4 area-efficient adder reduces logic overhead and supports signed/unsigned multi-bit operations.

<Overall architecture of 4T1C eDRAM>

#### **Measurement Results**

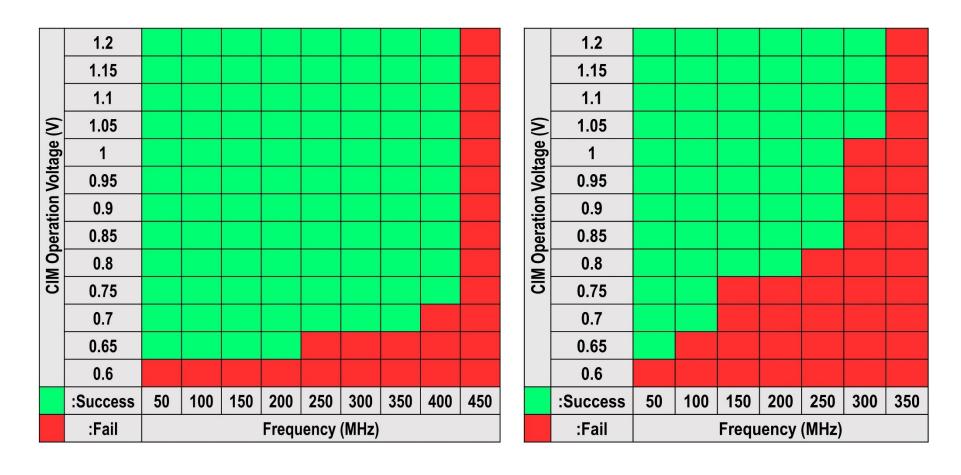

- CIM functionality was validated using an FPGA-based setup over 0.65-1.2V.

- Shmoo plots confirmed stable 1b-1b and 4b-4b MAC operations, with reduced margins in 4b-4b due to the use of global adder and accumulator.

<Shmoo plot, L: 1b-1b, R: 4b-4b>

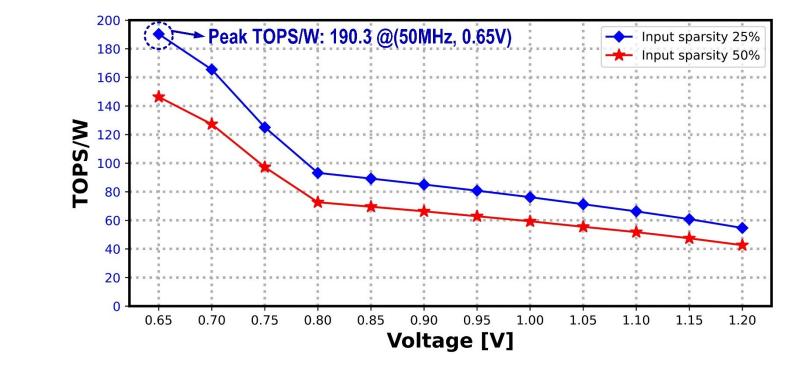

<Supply voltage for 4b-4b> < Performance summary >

### **Conclusion & Acknowledgement**

| Process                                    | 28 nm CMOS                      |

|--------------------------------------------|---------------------------------|

| Memory Type                                | eDRAM                           |

| Array Size                                 | 16Kb                            |

| Cell Structure                             | 4T1C                            |

| DRT                                        | 57.4-211                        |

| e Dual Multiply                            | XNOR/AND                        |

| Energy Efficiency<br>(TOPS/W)              | / 517.6(1b-1b)<br>190.3 (4b-4b) |

| Area Efficiency<br>(TOPS/mm <sup>2</sup> ) | 873.8(1b-1b)<br>28.9 (4b-4b)    |

- The proposed DMM-DCIM macro achieved <u>190.3</u> <u>TOPS/W</u> and <u>28.9 TOPS/mm<sup>2</sup></u> in 4b-4b operations. - CIM operations were verified up to 400MHz (1b-1b, >0.7V) and 300MHz (4b-4b, ≥1.05V) These results demonstrate that the proposed structure

- is an <u>efficient CIM solution</u> for edge AI applications.

- The chip fabrication and EDA tool were supported by the IC Design Education Center(IDEC), Korea.