# A High-Voltage Gate Driver IC with High CMTI and Integrated SPI Trimming

Myeong-Ho Kim and Se-Un Shin

Pohang University of Science and Technology (POSTECH), Korea

### **1. Introduction**

WBG semiconductors offer superior performance compared to Si, enabling much faster switching speeds than conventional Si-based MOSFETs or **IGBTs**.

In high-power applications, circuit topologies such as half-bridge or full-

However, due to their distinct characteristics, WBG devices require specialized gate drivers.

- To drive high-side switches, signal isolation is required due to the different voltage domain between the controller and the power stage.

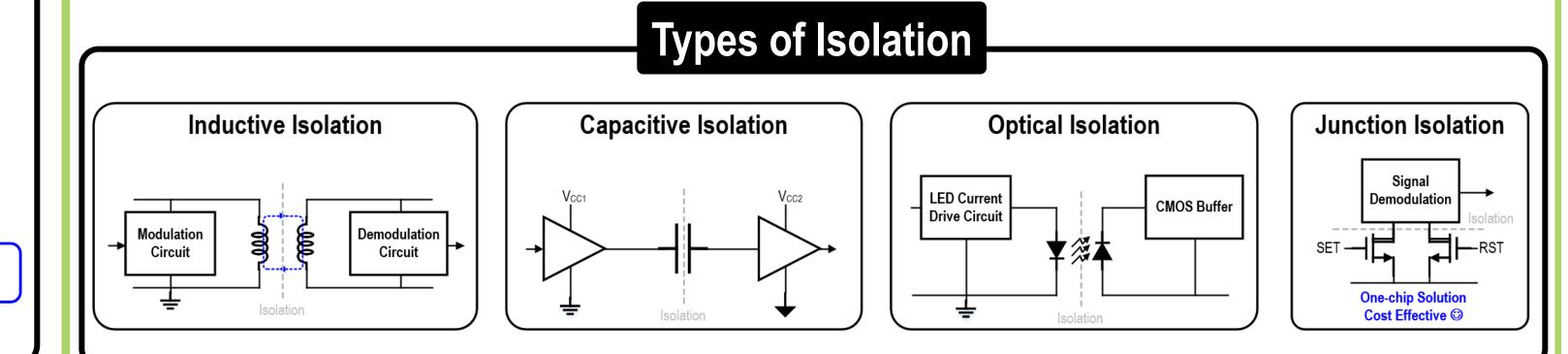

- Various isolation techniques are used, including inductive isolation using magnetic coupling, capacitive isolation using electric coupling, optical isolation using optocouplers, and junction isolation using LDOMSs.

- bridge are commonly used. ▲bandgap Si 500W [a.u.] SiC GaN breakdown Flyback Buck field a.u. Push-pull Boost electron mobility [a.u.] Buck-Half-bridge Boost Phase-shift Full-bridge thermal Full-Bridge saturation conductivity velocity [a.u.] Non-isolation Isolation [a.u.]

- Among these, junction isolation stands out as it can be implemented on a

- single chip, offering significant cost advantages over other approaches.

## 2. Issues

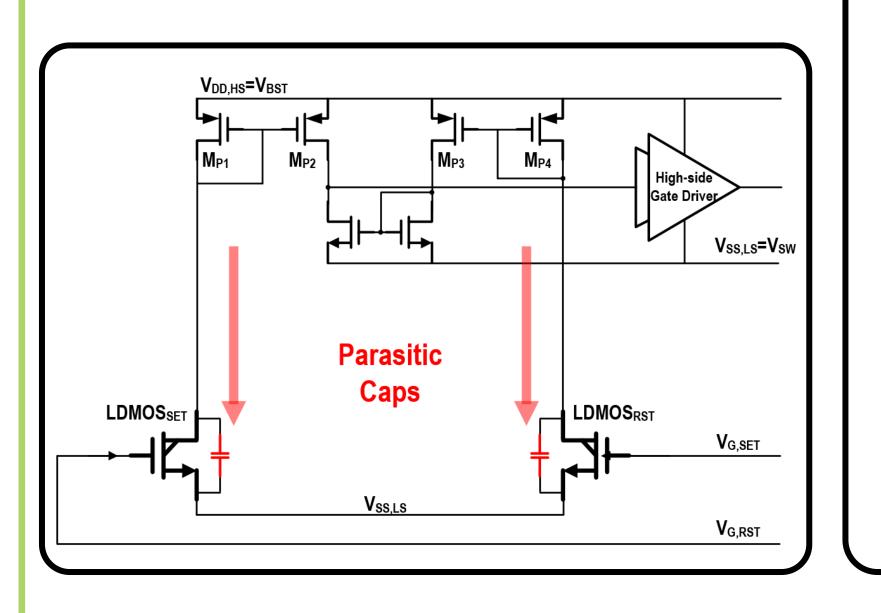

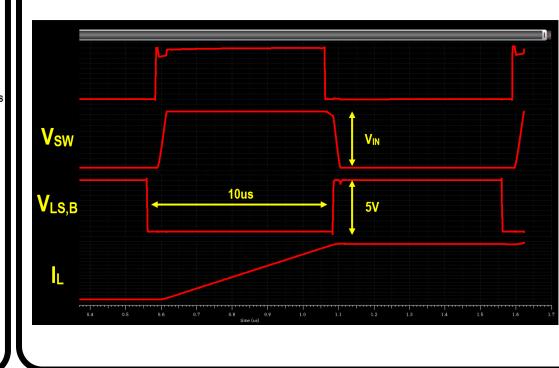

- When a signal to turn on the high-side switch is received, a pulse voltage is applied to the gate of the HV LDMOS, generating a pulse current through the left branch of the level shifter.

- This pulse signal is transferred to the high-voltage domain and demodulated, thereby turning on the high-side switch.

- Once the high-side switch is turned on, a large voltage transition (dv/dt) occurs at the V<sub>sw</sub> node.

## 3. Proposed Work

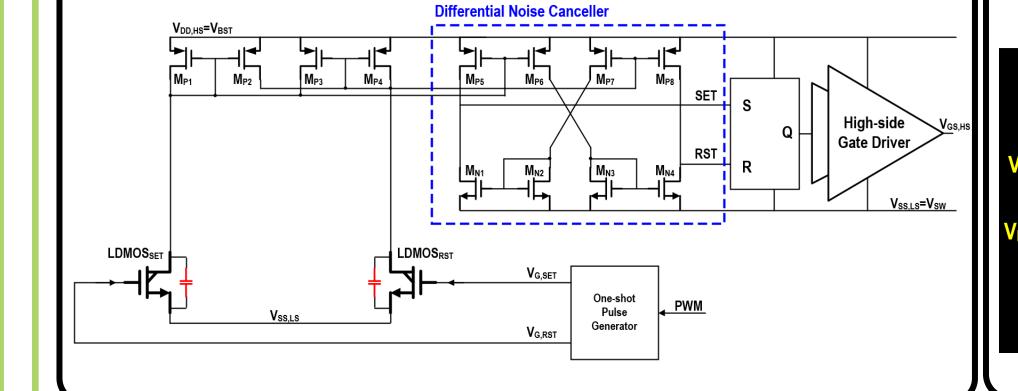

- The current generated by the combination of the dv/dt component and the parasitic capacitance of the HV LDMOS is ideally balanced through a symmetric layout, resulting in equal current flow.

- This current is then canceled by the current mirror structure in the subsequent differential noise canceller circuit, thereby improving CMTI

(Common Mode Transient Immunity).

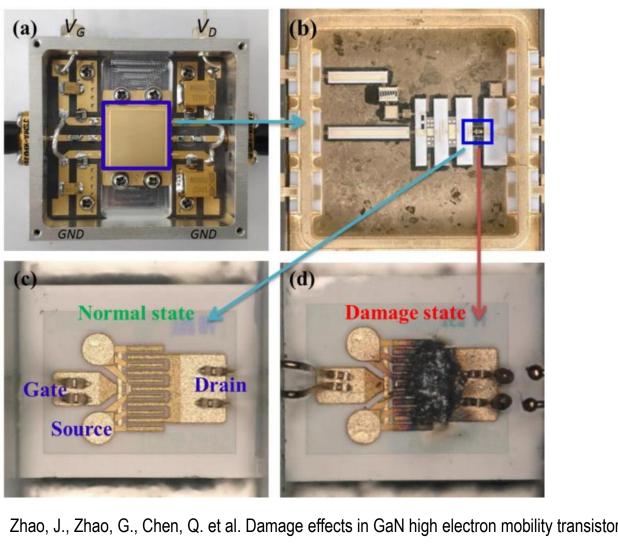

☺ Due to the large parasitic capacitance of the HV LDMOS, substantial current flows through both branches, causing false triggering. This can lead to malfunction of the converter and damage to the device.

power amplifier induced by high power microwave pulses. Sci Rep 15, 5988 (2025). https://doi.org/10.1038/s41598-025-89938-6

- The characteristics of fabricated chips often differ from the original design.

- To compensate for these variations, we include externally controllable trimming pins for post-fabrication adjustment.

Simulation Result

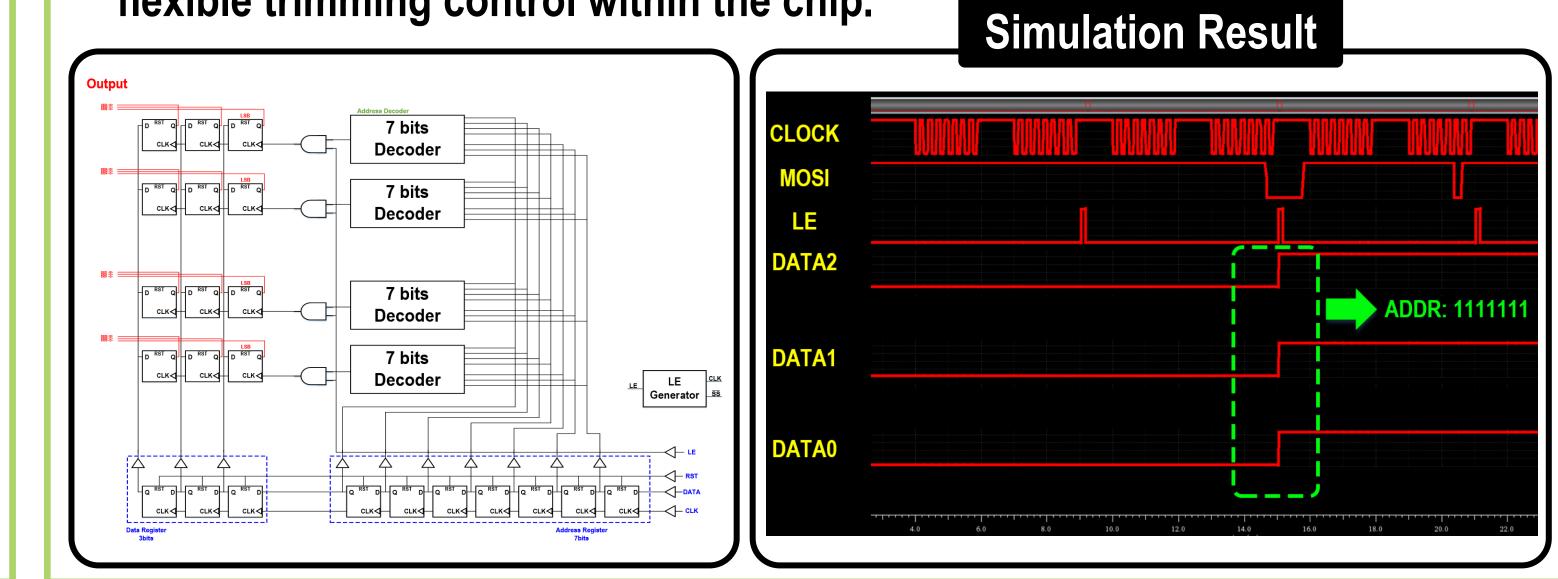

- SPI (Serial Peripheral Interface) is a standard protocol for communication between a chip and external devices.

- In this design, a reconfigurable full-custom SPI circuit is implemented, enabling communication with the external system using only four pads.

- The trimming signals are stored in an internal shift register and utilized for

flexible trimming control within the chip.

#### 7 bits Decoder 7 bits Decoder 7 bits Decoder

<sup>(2)</sup> However, implementing many trimming options requires many trimming pads, which leads to increased chip area.

#### **5.** Conclusion

- This work improves the noise Immunity (CMTI) performance of conventional level shifter structures by incorporating a differential noise canceller circuit.

- In addition, a reconfigurable full-custom SPI circuit is implemented for trimming, effectively reducing the number of pads required.

<Acknowledgement> 본 연구는 IDEC에서 MPW를 지원받아 수행하였습니다. 이 성과는 정부(과학기술정보통신부)의 재원으로 한국연구재단의 지원을 받아 수행된 연구임 (RS-2023-00219443) 본 연구는 Glocal 30 University Project (2회/년)의 지원을 받아 수행하였습니다. 이 논문은 2022년도 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원의 지원을 받아 수행된 연구임 (No.2022-0-00720, 차세대 초고속 저궤도 위성통신을 위한 W밴드 컴팩트·고효율·신개념 RF/전력 핵심 부품 개발) 이 성과는 2025년도 정부(산업통상자원부)의 재원으로 한국산업기술진흥원의 지원을 받아 수행된 연구임(RS-2024-00401466, 2025년 산업혁신인재성장지원사업) 본 연구는 한국산업기술평가관리원을 통해 산업통상자원부의 산업기술혁신사업 (RS-2022-00154983, 저전력 센서와 구동을 위한 자립형전원 센서 플랫폼 개발)의 지원을 받아 수행되었습니다