# IDEC Chip Design Contest

# dv<sub>DS</sub>/dt Sensing Based Active Gate Driver IC for SiC MOSFETs

Min-Sik Kim and Se-Un Shin Pohang University of Science and Technology (POSTECH), Korea

#### 1. Introduction

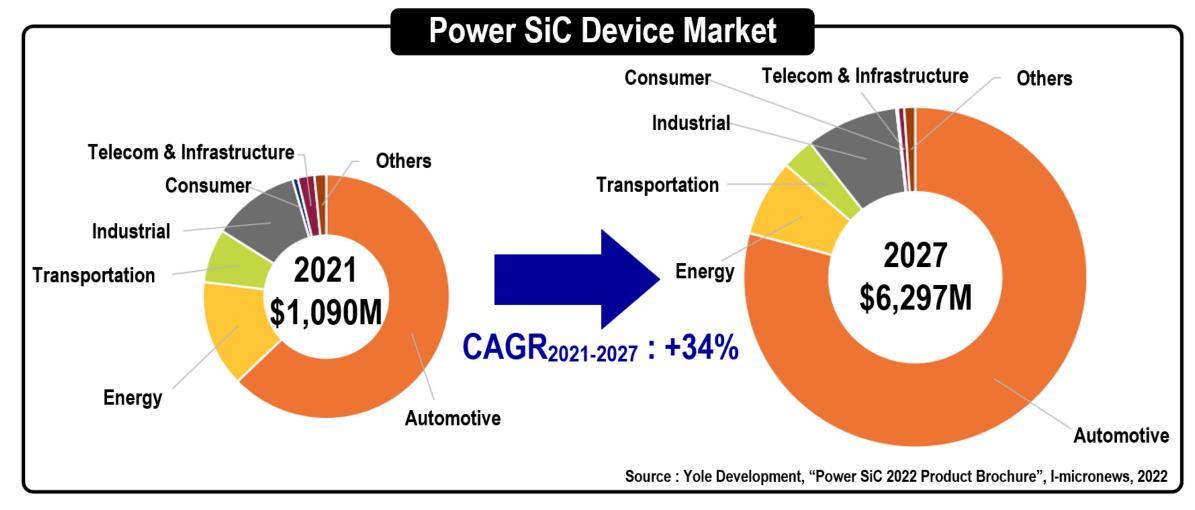

- Many advantages of SiC devices compared to Si devices :

- High breakdown voltage, low on-resistance, low parasitic capacitance, etc.

- There is a significant increase in demand in fields such as automotive, energy, and the power industry.

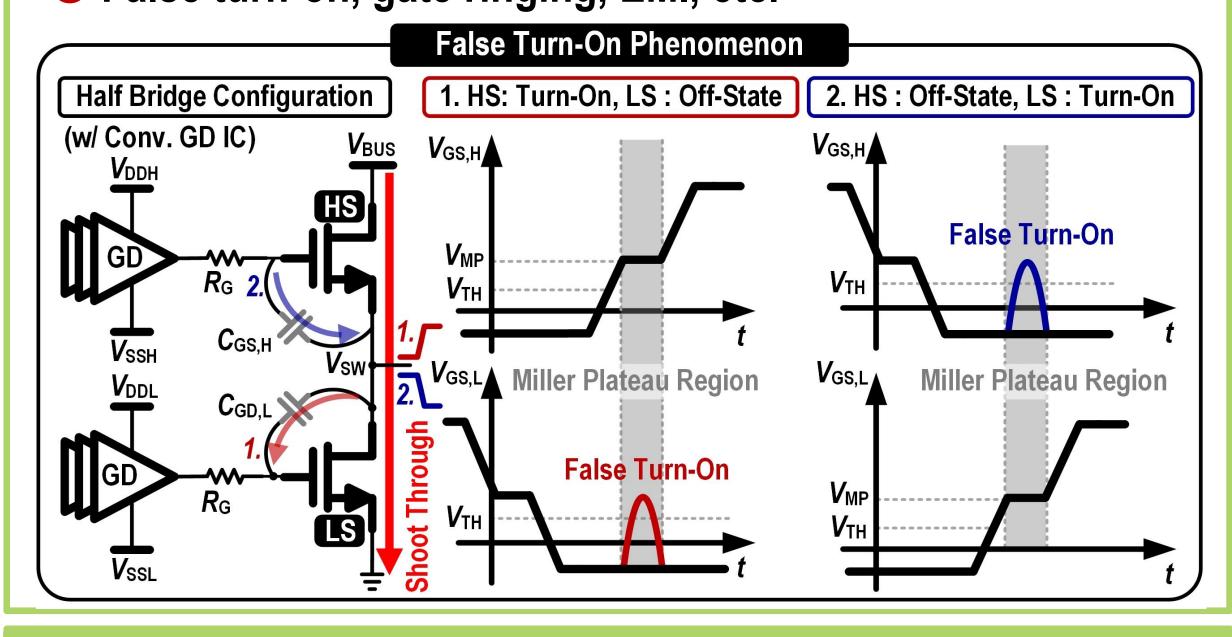

- With increasing the operating frequency, there are several issues due to high dv/dt and di/dt, parasitic elements :

- **B** False turn-on, gate ringing, EMI, etc.

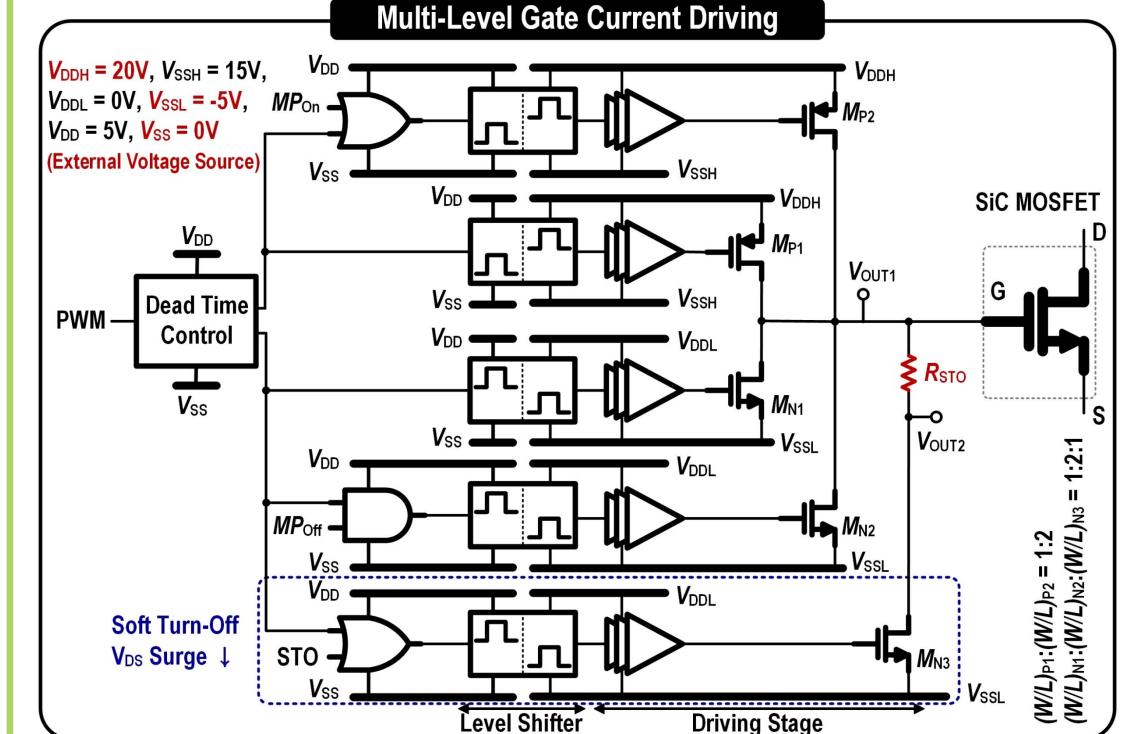

## 3. The Proposed Structure

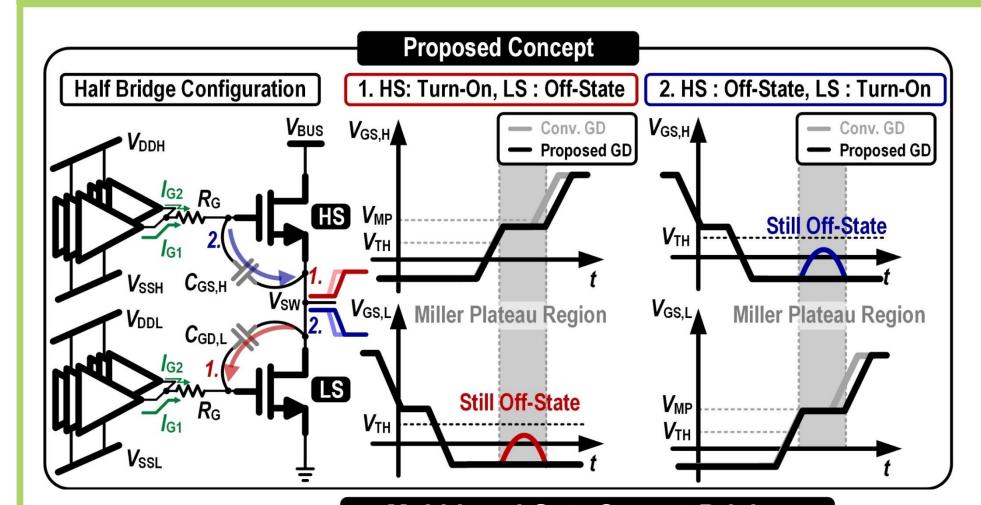

- Adjusting the driving strength differently for each region with closed-loop method.

- **©** Preventing of false turn-on

- Improving the trade-offs

- Practical

- © Small area

- Segmented output buffer

- Level shifter

- Dead time control circuit for buffer

- | Limiter

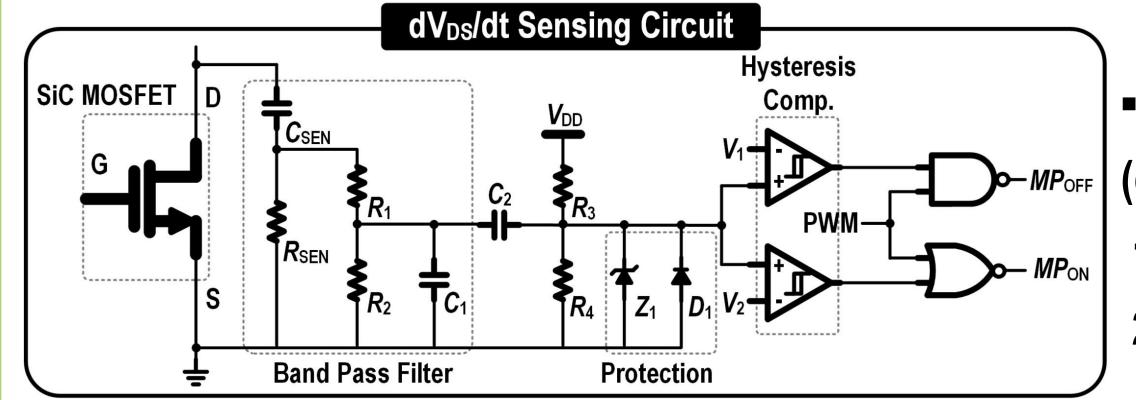

- dv<sub>DS</sub>/dt sensing circuit

- Desaturation circuit

- Under voltage lock out circuit

- etc.

- For preventing false triggering (due to noise)

- 1. Band-pass filter

- 2. Hysteresis comparator

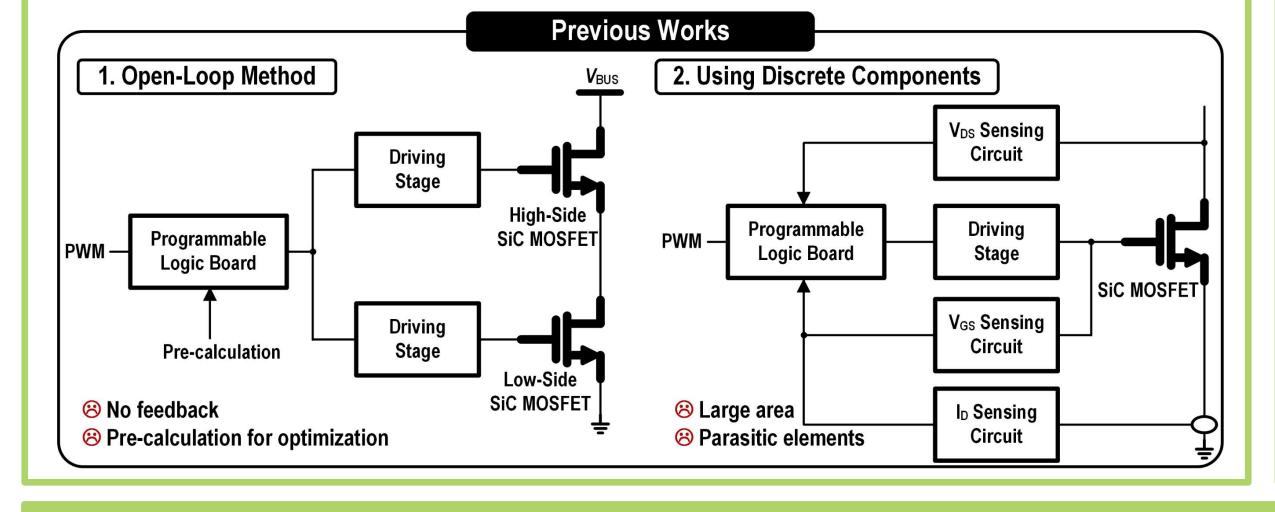

#### 2. Previous Works

- Active Gate Driver (AGD):

Improve trade-offs between the issues and switching speed

- Limitations of previous works

- 1. Open-loop methods:

- **8** Lack of flexibility to operating condition variations

- **(28)** Impractical

- 2. Circuit implementation using discrete components

- **8** Large area

<Acknowledgement>

(8) Increase in the influence of parasitic elements

#### 4. Simulation Result

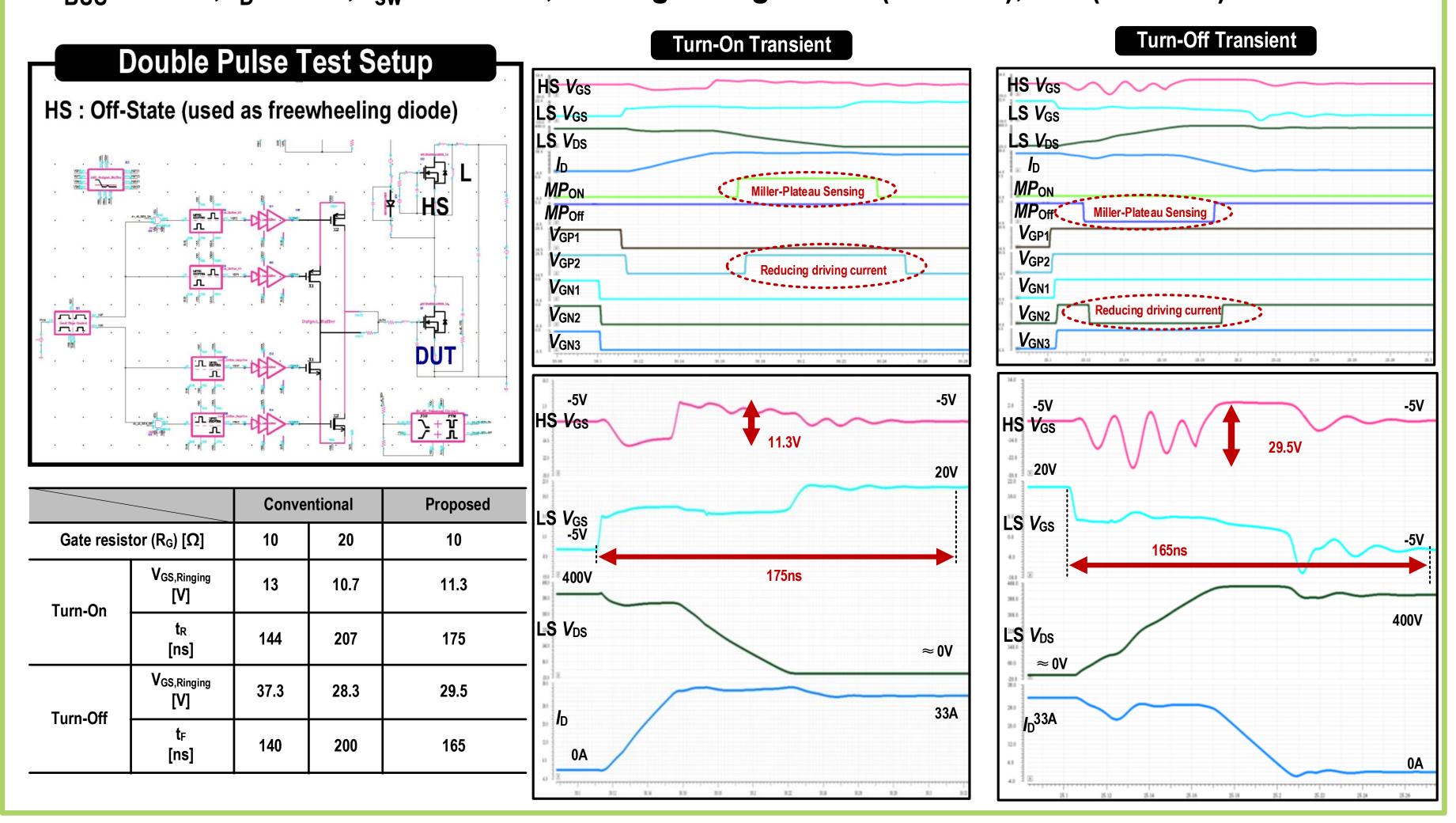

- Post-simulation result (Cadence), Double pulse test for evaluating the dynamic behavior

- $V_{BUS}$  = 400V,  $I_{D}$  = 33A,  $f_{sw}$  = 200kHz, Driving voltage : 20V (Turn-on), -5V (Turn-off)

### 5. Conclusion

- This work proposes AGD IC for high-frequency operation of SiC MOSFETs that overcomes the limitations of previous works.

- Miller plateau region is sensed, and the gate current is controlled using a segmented output buffer, with a closed-loop method applied.

- Proposed circuit reduces the magnitude of ringing caused by high dv/dt without significantly slowing down the switching speed.