# **IEEE Asian Solid-State Circuits Conference**

고려대학교 반도체시스템공학과 박사과정 김현진

### **Session 2 Switching Mode Power Converters**

이번 A-SSCC 2022의 Session 2는 Switching Mode Power Converters라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는 인덕터를 사용하여 높은 DC 전압을 낮은 DC 전압으로 강하시키는 고효율 Buck 변환기에 관한 논문들이 발표되었으며, 이는 고성능, 고집적 반도체 구성에 필요한 power management IC (PMIC) 회로들을 다루고 있다. 본 세션에서는 전통적인 인덕터 기반 DC-DC 변환기 구조를 바탕으로 한 DC-DC 변환기 논문이 3편이 발표되었고, 하이브리드 구조를 바탕으로 한 DC-DC 변환기 논문이 1편이 발표되었다. 특히, side-channel attack에 대한 내성을 갖는 3중 출력 인덕터 & low dropout (LDO) 레귤레이터 등 애플리케이션 중심으로 설계된 새로운 구조의 PMIC들이 발표된 것이 특징이다.

(#2.1 - 대만 NYCU & Chip-GaN Power Semiconductor Corporation & Realtek) 본 논문에서는 3중 출력 Buck 변환기와 LDO 레귤레이터를 기반으로 높은 Minimum Traces to Disclosure (MTD) 성능을 갖는 DC-DC 변환기를 발표하였다. 기존의 IoT의 advanced encryption system (AES) engine 은 PMIC의 전력 소모와 electromagnetic (EM) leakage 측정을 통해서 하드웨어적인 보안 키 유출위협이 존재한다. 이러한 위협을 줄이기 위해서 존래의 DC-DC 변환기는 LDO 레귤레이터의 기준전압과 더미 전류에 랜덤성을 사용하여 보안성을 강화하였다. 하지만, 이러한 기술들은 상대적으로 낮은 LDO 레귤레이터의 전력 효율을 더욱 감소시키므로 IoT 애플리케이션에 적합하지 못하다. 랜덤한 동작 주파수를 가지는 Buck 변환기 또한 소개되었지만, 외부 인덕터를 사용하므로 EM leaked signature가 보안 정보를 드러낸다. 따라서, 본 논문은 하나의 외부 인덕터와 세 개의 AES engine들을 사용하여 세 개의 DC 전압 출력을 만드는 구조를 제안하였고, 이는 각각의 AES engine의 EM signature를 파악하기 힘들게 만듦으로써, EM leaked probability를 2.1× 만큼 감소시킨다. 또한, 본 논문에서는 AES 간의 EM 정보를 섞어주는 intelligent true random number generator (iTRNG)를 사용하여 EM leaked probability를 7.8× 만큼 추가로 감소시켜준다. 마지막으로, EM gated LDO 레귤레이터 두 개를 랜덤하게 동작시켜서, 최종적인 MTD 성능을 최신 보안 DC-DC 변환기 대비 3배 이상 증가시켰다.

(#2.2 - 대만 NTU & Richtek) 본 논문에서는 cascaded된 voltage-controlled oscillator (VCO) 기반으로 동작하는 Gaming SoC 애플리케이션 목표의 time-domain Buck 변환기를 발표하였다. 종래의 time-domain 기반의 Buck 변환기 제어 기술은 Buck 변환기의 출력 전압 및 인덕터 전류 정보를 두 개의 VCO 간의 주파수 차이로 변환하여 Buck 변환기의 동작 주파수를 생성한다. 이러한

time-domain 기반의 제어 방식은 고주파 동작에 용이하고, 제어기가 작은 면적을 차지한다는 장점이 있다. 하지만 VCO 간의 mismatch 및 VCO gain (K<sub>VCO</sub>) variation에 DC-DC 변환기의 stability 가 변화하면서 전체적인 PMIC의 성능을 저하한다. 따라서, 본 논문에서는 cascaded-VCO를 사용하여, VCO 간의 mismatch로 인한 성능 저하를 제거한다. 첫 번째 VCO는 gain error subtractor의 출력 전압과 인덕터 전류 센서로 인한 전압 간의 차이를 입력으로 사용하고, pulsed 출력을 두 번째 VCO의 입력으로 보내서 VCO의 positive edge 시작을 정한다. 두 번째 VCO는 trigger 되었을 때, 정해진 on-time 펄스를 내보내며, feedback 제어에 따라서 동작 상태에 적합한 steady-state 주파수가 정해지게 된다. 이를 통해 본 논문은 0.81 mV/A의 기존 time-domain 변환기들 대비 높은 load regulation 성능과 상대적으로 낮은 FoM들을 달성하였다.

(#2.3 - 벨기에 KU Leuven) 본 논문에서는 하이브리드 Ladder Buck 변환기 구조를 기반으로, 두 개의 인덕터를 사용하여 Li-ion 배터리의 전압을 강하시켜주는 DC-DC 변환기를 발표하였다. 종래의 multi-level Buck 변환기 구조는 유효 동작 주파수를 증가시켜주므로, 작은 DCR을 가지는 부피가 작은 인덕터를 사용하여 효율 증대를 이뤘다. 하지만 multi-level 변환기는 단일 conduction path에 많은 수의 스위치를 직렬 연결하므로 높은 전류를 공급하기 어렵고, 위상에 따른 인덕터전류가 불균형하여 DC-DC 변환기의 전력 효율과 전력 밀도 성능들에 제한한다. 따라서, 본 논문은 대칭적인 2:1 ladder 변환기 구조와 두 개의 인덕터를 사용하여 duty 조절을 통해서 출력 전압을 일정하게 유지한다. 따라서 capacitor는 항상 soft charging을 유지하며, 인덕터에 흐르는 DC 전류가 감소하여 인덕터 크기를 감소시킬 수 있고, 스위치별 전류량이 감소하게 된다. 또한, 일정한 V<sub>IN</sub>/2의 전압 레일은 스위치 드라이버들의 공급 전압 레일로 사용되어 회로 복잡도를 매우 감소시켜준다. 이를 통해 본 논문은 종래의 다른 Buck 변환기 논문들과 비교하여 0.93 W/mm²의 가장 높은 active 전력 밀도를 달성하였다.

(#2.4 - 대만 NTU) 본 논문에서는 종래의 Buck-Boost 변환기 구조를 기반으로 auto-shift-ramp generator를 통해서 Li-ion 배터리 전압 변화에 따라서 seamless-mode-transition 기능을 구현한 DC-DC 변환기를 발표하였다. 종래의 Buck-Boost 변환기 구조는 시간이 흐름에 따라서 Li-ion 배터리 출력 전압이 감소하므로, 동작 방식이 Buck 변환에서 Buck-Boost 변환으로, Buck-Boost 변환에서 Boost 변환으로 순차적으로 변화한다. 이때, 기존의 Buck-Boost 변환기는 duty 변환 기간이 필요하므로 순간적인 stability 기준 변화가 compensator 출력 전압을 변화시키는 동안, DC-DC 변환기 출력 전압에 큰 리플 전압이 생성된다. 본 논문은 이러한 mode transition이 발생시키는 출력 전압 변화를 감소시키기 위하여 auto-shift-ramp (ASR) 기술을 제안한다. 제안된 기술은 mode transition 시 이론적으로 예상되는 compensator 출력 전압 변화를 corresponding delay time 및 advance time으로 계산하여 mode transition 시 ramp generator의 시작 지점을 변화시킨다. 이를 통해 본 논문은 0.484% 이하의 가장 낮은 mode transition 전압과 18.98 μs 이하 가장 낮은 mode transition settling time을 달성하였다.

# 저자정보

## 명예기자 김현진

● 소 속 : 고려대학교 반도체시스템공학과 박사과정

● 연구분야: Power Management IC ● 이 메일: jamespul@korea.ac.kr ● 홈페이지: https://kilby.korea.ac.kr

# **IEEE Asian Solid-State Circuits Conference**

KAIST 전기및전자공학과 박사과정 배홍현

### **Session 10 Analog Techniques**

**#10** 이번 A-SSCC 2022의 Session 10은 Analog Circuits and Techniques라는 주제로 총 4편의 논문이 발표되었다.

#10-1 IoT 및 wireless sensor node와 같은 장치에서 효율적인 동작을 위해 온도변화에 둔감한 On-chip sleep timer를 필요로 한다. 이를 위한 clock frequency 생성에서 중요한 점은 사용하는 power 대비 낮은 TC (Temperature Coefficient)이다. 쉽게 말해, 적은 전력을 사용하면서 동시에 온 도변화에 둔감한 clock frequency 생성이 필요하다. 이를 해결하기 위한 기존의 기술(ISSCC 2016, T. Jang)은 SCR (Switched Capacitor Resistor)와 switched resistance boosting 기법을 이용하여 온도변 화에 둔감한 clock frequency를 생성하였다. 하지만 leakage current의 경우 device의 크기가 점점 작아짐에 따라 더 증가하기 때문에 첨단 공정에서는 새로운 기법을 필요로 한다. 본 논문에서는 65nm의 상위 공정에서도 기존의 논문들과 비교하여 경쟁력 있는 성능을 가진다. 전력 소모를 최 소화 하면서 동시에 온도 변화에 둔감한 clock frequency를 만들기 위해서 본 논문에서는 supply 전압을 400mV 수준으로 낮추었다. 이는 supply 전압이 낮으면 leakage 전류 또한 낮아지는 device의 특성을 이용한 것이다. 하지만, supply전압이 낮으면 clock frequency를 일정하게 유지하 기 위한 feedback loop 형성이 까다롭다. 왜냐하면 feedback loop 형성을 위해서 analog amplifier 를 필요로 하는데, 본 논문과 같이 supply 전압이 400mV 낮은 경우 analog amplifier의 제대로 된 동작이 어렵기 때문이다. 따라서 본 논문은 analog amplifier의 역할을 digital domain으로 가져와 TDA (Time Domain Amplifier)로 대체하여 feedback loop을 형성한다. 본 논문에서는 SCRM (Switch-less Resistance Multiplier)와 p+ poly resistor의 ratio를 reference frequency로 사용한다. 하 지만, 본 논문에서 제시하는 SCRM은 온도에 따라 저항 값이 변하기 때문에 일정한 reference frequency를 유지하기 위해선 LUT-based calibration을 필요로 한다. 본 논문을 정리하면, 상위 공 정(65nm)에서 low-power clock 생성을 위해 supply 전압을 극단적으로 낮추었다. 낮은 supply 전 압에서도 안정적인 동작이 가능한 SLRM 및 TDA를 통해 Frequency-locked loop (FLL)을 만들었으 며, 기존에 발표된 다른 work 대비 가장 낮은 current efficiency 및 TC를 달성함에 의미가 있다고 생각한다.

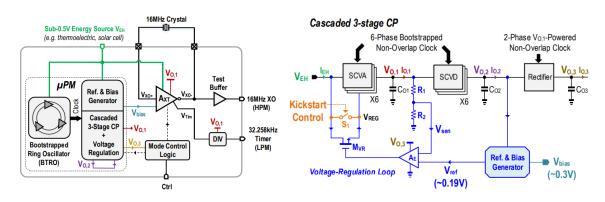

#10-2 최근 IoT 노드들의 소형화와 비용절감이 중요해짐에 따라 kHz/MHz 크리스탈과 같이 면적이 큰 외장소자의 사용을 피하고, 에너지 하베스터를 내장하려는 추세를 보이고 있다. 본 논문에서는 single crystal로 16MHz reference clock과 32kHz timer를 생성할 수 있는 sub-0.5V crystal oscillator-timer(XO-Timer)를 제안하였다.

제안한 XO-Timer는 에너지 하베스터 출력전압의 변화로부터 내부 모듈의 전압과 전류를 최적화하기 위해 micro-power manager( $\mu$ PM)를 사용하였다. 기존  $\mu$ PM구조의 경우 복수의 voltage regulation loop이 필요하였으나, 제안한  $\mu$ PM는 cascaded 3-stage charge pump(CP) 구조를 사용하여 하나의 voltage regulation loop으로 복수의 전압을 regulation하였다.

[그림 1] (좌) 제안한 XO-Timer의 구조 (우) Cascaded 3-stage CP

그림1의 우측 그림에서 보여지는 듯이, Cascaded 3-stage CP 구조는 voltage regulation loop이 첫 번째 stage의 출력 전압만 regulation하고 이후 stage들의 전압은 이전 stage의 전압을 바탕으로 생성되는 구조를 가지고 있다. 이로 인해 뒤쪽 stage들의 전압은 앞쪽 stage에 비해 regulation 성능이 떨어지는 특성을 가지고 있다. Regulation된 각 전압의 ripple을 줄이기 위해서는 각 스테이지의 출력에 붙어있는 smoothing capacitor의 크기가 커질 필요가 있다. 이러한 부담을 줄이기위해 본 논문에서는 첫 번째와 두 번째 stage에 사용된 SC voltage adder와 SC voltage doubler를 6개씩 병렬 구성하여 6-Phase 동작으로 구현하였고, 이를 통해 요구되는 smoothing capacitor의 크기를 감소시켰다.

사용된 Core amplifier의 경우 (그림 1 좌측의  $A_{XT}$ ) reconfigurable한 구조를 가져 모드에 따라 16MHz와 32kHz의 주파수를 생성할 수 있도록 구현하였다. 16MHz의 주파수를 생성할 때는 Pierce oscillator와 유사한 동작을 하며 낮은 위상 노이즈를 갖도록 하고, 32kHz의 낮은 주파수를 생성할 때는 3-stage gm구조를 사용하고 load capacitance를 감소시켜 파워소모를 낮추었다.

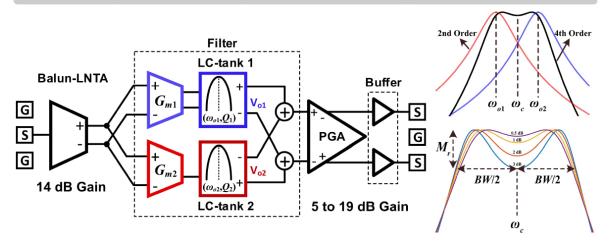

#10-4 RF receiver에서 다수의 채널을 선택적으로 사용하기 위해서 out-of-band 주파수 대역을 강하게 막아줄 RF filter를 필요로 한다. 기존 논문의 경우 amplifier 기반의 N-path filter를 사용하여 원하는 주파수 대역 만 통과시키는 filter가 발표되었다. 하지만 여러 stage의 amplifier를 필요로하며 그에 따라서 소모되는 전력 또한 증가하게 된다. 본 논문의 경우 전력소모를 최소화 하면서 동시에 quality factor (Q)를 극대화하기 위해 2개의 병렬 LC tank를 그림3과 같이 사용하여 filter를 구성하였다. 센터 주파수 ( $\omega_{\rm C}$ ) 기준으로 각각  $\omega_{\rm O1}$ ,  $\omega_{\rm O2}$ 에 공진 주파수를 가지는 LC-tank를 사용하였고, In-band( $\omega_{\rm O1} \sim \omega_{\rm O2}$ )에서는  $V_{\rm O1}$  및  $V_{\rm O2}$ 가 out of phase, out-of-band에서는 in-phase의 성질을 이용하여 그림3과 같은 4th-order의 band pass filter를 가진다. 사실 두 병렬의 LC 공진기를 이용하여 4th-order filter를 만드는 기법은 기존에 발표된 바 있으나 본 논문에서는 해당 기법을 1V의 낮은 supply 전압에서 넓은 fractional bandwidth를 가지는  $4^{\rm th}$ -order filter를 설계하였다는 점에서 의미를 가진다. 따라서 성능 비교 테이블을 보면 알 수 있듯이, NF<sub>min</sub> 및 FOM 등 성능 지표는 기존의 발표된 work들과 비슷한 수준이지만 1V은 낮은 supply 전압 및 22nm FDSOI의 상위 공정을 사용하였기 때문에 filter에 사용한 전력은 기존의 논문 대비 상당히 경쟁력 있는 지표를 나타낸다.

### Block Diagram of the Proposed Filter and Implemented Front-End

[그림 3] #10-4에서 제안한 RF-filter의 동작 원리

### 저자정보

### 명예기자 배홍현

● 소 속 : KAIST 전기 및 전자공학과 박사과정

● 연구분야: Fast & Fully-integrated DC-DC Converter

• 이 메 일 : hongbae2004@kaist.ac.kr

● 홈페이지: icdesignlab.net

# **IEEE Asian Solid-State Circuits Conference**

성균관대학교 전자전기컴퓨터공학과 박사과정 조종완

### **Session 14 LDO Voltage Regulators**

이번 A-SSCC 2022의 Session 14은 LDO Voltage Regulators라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는 LDO 설계에서 면적을 최소화하기 위한 구조에 대한 주제를 중점으로 발표되었다. 3가지의 Digital LDO 구현 방식과 Capless Analog LDO 구현 방식을 통해 Low Area, Fast Load Transient, High PSR(Power Supply Rejection, Low Ripple, Math Product Process Guide에 대해다양한 관점을 시사하고 있다. A-SSCC 2022의 LDO Voltage Regulation Session에서 보여주는 내용으로 보았을 때, 현재까지 Industry에서 기존 문제점을 해결하고 양산화를 진행하기 어려웠던 한계(Load Transient의 한계와 Data Rate 증가를 위해 요구되는 High PSR 한계를 해결하는 구조 기반으로 높을 수율 확보에 대한 어려움)를 빠른 시일내에 해결할 것으로 전망된다.

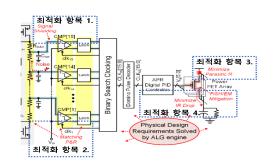

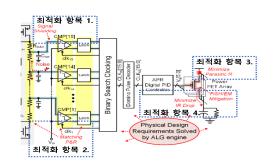

(#14-1. 칭화대(Intel Corporation), 중국) 본 논문에서는 Digital LDO의 자동화 구현 방법에 대해 연구하여 발표를 진행하였다. Digital LDO의 연구 중에 하나인 다양한 Process에 대해서 최적화하는 방법 및 엔지니어의 역량에 따라서 고려되지 않은 Path에 대해서 생기는 Noise 성분을 최소화하는 자동화 설계 방법에 대해서 제시하고 있다. 일반적으로 생각되는 Digital LDO의 경우 Memory나 Sensor에 사용될 수 있는데, Memory나 Sensor Application 이외에도 공정별로 새로운 Analog Circuit을 설계를 진행할 때, 필요한 Reference 전압에도 사용될 수 있다. 본 논문에서는 대표적으로 Reference 전압에 영향을 받게 되는 Block인 ADC의 Kickback noise를 최적화할 수 있는 방법을 설명하고 있으며, 본 논문에서 비교로 제시하는 Flash ADC 이외에도 SAR ADC나 SD ADC에서도 영향을 줄 수 있는 Parameter로 응용할 수 있는 분야가 클 것으로 기대된다. [그림1]에서 볼 수 있는 것처럼 자동화로 할 수 있는 DLDO 설계 방법에서 고려되는 부분 크게 Line Shielding, Device Place and 최적화 Routing, Critical Path에 대한 Minimize Parasitic Resistance를 고려하여 설계가 있다.

[그림 1] 논문에서 제시하는 최적화 항목

표 1에서 볼 수 있는 기준으로 Manual 설계와 Analog Layout Generator methodology를 비교하여, 각 사람의 Manual과 비교하여 최적화된 Size를 확인할 수 있으며, 이를 비교하기 위해 설계시 고려되는 시간과 최적화된 성능을 ADC에 Comparator Delay, offset, Kickback Noise Current, Power Consumption, Area의 지표로 비교하였다. 자동화되는 DLDO 설계를 할 수 있을 경우 공정에 따라 필요한 Reference Voltage를 자유롭게 생성할 수 있고 Analog Block에서 요구되는 Noise 성분을 최적화할 수 있다면, Analog Block의 최적화가 기존에 비해 빠르고 더 높은 성능을 가질수 있을 것에 대한 기대를 주는 연구이다.

|                                | Manual | EP1  | EP2                              | EP3                                                     |

|--------------------------------|--------|------|----------------------------------|---------------------------------------------------------|

| ALG Human-Related Cost         | Manual | None | Annotate<br>constraint<br>script | Give critical<br>device(x,y) w/<br>constraint<br>script |

| Delay [ps]                     | 158    | 200  | 193                              | 155                                                     |

| Offset [mV]                    | 0.4    | 3.5  | -1.78                            | 2.18                                                    |

| KB Noise Current [uA]          | 1.1    | 0.85 | 0.61                             | 0.18                                                    |

| Power Consumption [Normalized] | 100    | 111  | 108                              | 105                                                     |

| Area [Normalized]              | 100    | 171  | 299                              | 100                                                     |

[표 1] 논문에서 제시하는 ALG Human Related Cost와 Result Summary

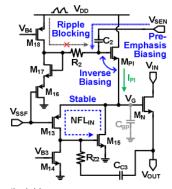

(#14-2. 서울대, 한국) 본 논문에서는 Capless Analog LDO의 한계로 시사되는 Load Transient Time 확보 및 High PSR 구조 설계에 대해 연구하여 발표를 진행하였다. 제안하는 구조에서는 [그림 2]에서 볼 수 있는 것처럼 Error Amplifier에서 사용되는 Bandwidth를 기존보다 더 확보하는 방식으로 Conventional 구조에서 쉽게 보일 수 있는 Current Source Path에서 보이는 Supply Ripple Path나 Loop에서 보이는 Stability까지 최적화하는 방법을 사용하였다.

[그림 2] 논문에서 제시하는 제안하는 SSF(Super Source Follower)구조 Error Amplifier

그림 2에서 보여준 내용이외에도 본 논문에서는 Load를 Sensing하는 Current Sensor를 통해, Load에 따라 pole 값과 zero 값을 조절할 수 있는 시스템 구성을 통해 Wide Range Pole 구조를 가지게 되었다. 이번 연구를 통해 외부 BoM 비용 없이 안정적인 Capless LDO 구조에 개발에 한 발자국 더 다가가게 되었다.

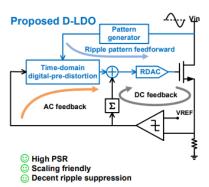

(#14-3. 청화대, 중국) 본 논문에서는 Digital Feedback 형태의 구조를 갖는 LDO를 연구하여 제안 하였습니다. NMOS의 Power Stage를 제어하는 방식은 R-DAC을 통해 제어를 진행하였으며, [그림 3] 에서 볼 수 있는 것처럼 Digital Feedback 형태의 LDO 구조를 통해 Load Transient 수치 향상 및 PSR 수치의 개선을 가져오게 되었다. 본 논문에서 기존의 Digital Feedback LDO의 경우 R-DAC을 선택하는 방법에서 한 개의 Step 단위가 너무 크게 되면 Load Transient 반응은 빠르게 이루어질 수 있으나 Ripple이 크게 발생하게 되는데, 이를 개선하기 위해 Integer Classification과 Noninteger Classification Table을 가지게 되어, Ripple을 최적화한 결과를 하여, 일반적인 Digital LDO구조에서 발생할 수 있는 Ripple 문제 해결 방안이 하나의 방향이 추가되었다.

[그림 3] 논문에서 제시하는 Digital Feedback Digital LDO

(#14-4. 홍콩대, 중국) 본 논문에서는 Reference Oscillator와 출력 전압을 감지하여 주파수를 변경하는TRO(Tunable Ring Oscillator) 출력을 비교하여 DVFS(Dynamic Voltage and Frequency Scaling)을 지원하는 DLDO를 연구하여 제안하였다. 제안하는 구조에서는 Conventional 구조와 다른 점은 Self-clocked Unified Voltage and Frequency Regulator(UVFR)을 추가하여, 출력 전압이 Reference Low 보다 낮아져서 출력 전압이 Regulation이 어려울 경우 Reference CLK 주파수를 Reference High에 맞춰서 출력 전압을 다시 올리는 방법을 사용하여 Load Transient 성능을 개선하였다. 본 논문에서 제안하는 Self-clocked UVFR 구조를 통해 Oscillator 사용한 Digital LDO 구조 PVT Variation을 최소화할 수 있는 장점이 있다.

### 저자정보

### 명예기자 조종완

● 소 속 : 성균관대학교 전자전기컴퓨터공학과 박사과정

● 연구분야: Energy Harvesting, PMIC

• 이 메 일 : jw1114@skku.edu

● 홈페이지: http://iclab.co.kr

# **IEEE Asian Solid-State Circuits Conference**

성균관대학교 전자전기컴퓨터공학과 박사과정 조종완

### **Session 14 LDO Voltage Regulators**

이번 A-SSCC 2022의 Session 14은 LDO Voltage Regulators라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는 LDO 설계에서 면적을 최소화하기 위한 구조에 대한 주제를 중점으로 발표되었다. 3가지의 Digital LDO 구현 방식과 Capless Analog LDO 구현 방식을 통해 Low Area, Fast Load Transient, High PSR(Power Supply Rejection, Low Ripple, Math Product Process Guide에 대해다양한 관점을 시사하고 있다. A-SSCC 2022의 LDO Voltage Regulation Session에서 보여주는 내용으로 보았을 때, 현재까지 Industry에서 기존 문제점을 해결하고 양산화를 진행하기 어려웠던 한계(Load Transient의 한계와 Data Rate 증가를 위해 요구되는 High PSR 한계를 해결하는 구조 기반으로 높을 수율 확보에 대한 어려움)를 빠른 시일내에 해결할 것으로 전망된다.

(#14-1. 칭화대(Intel Corporation), 중국) 본 논문에서는 Digital LDO의 자동화 구현 방법에 대해 연구하여 발표를 진행하였다. Digital LDO의 연구 중에 하나인 다양한 Process에 대해서 최적화하는 방법 및 엔지니어의 역량에 따라서 고려되지 않은 Path에 대해서 생기는 Noise 성분을 최소화하는 자동화 설계 방법에 대해서 제시하고 있다. 일반적으로 생각되는 Digital LDO의 경우 Memory나 Sensor에 사용될 수 있는데, Memory나 Sensor Application 이외에도 공정별로 새로운 Analog Circuit을 설계를 진행할 때, 필요한 Reference 전압에도 사용될 수 있다. 본 논문에서는 대표적으로 Reference 전압에 영향을 받게 되는 Block인 ADC의 Kickback noise를 최적화할 수 있는 방법을 설명하고 있으며, 본 논문에서 비교로 제시하는 Flash ADC 이외에도 SAR ADC나 SD ADC에서도 영향을 줄 수 있는 Parameter로 응용할 수 있는 분야가 클 것으로 기대된다. [그림1]에서 볼 수 있는 것처럼 자동화로 할 수 있는 DLDO 설계 방법에서 고려되는 부분 크게 Line Shielding, Device Place and 최적화 Routing, Critical Path에 대한 Minimize Parasitic Resistance를 고려하여 설계가 있다.

[그림 1] 논문에서 제시하는 최적화 항목

# **IEEE Asian Solid-State Circuits Conference**

KAIST 전기 및 전자공학과 박사과정 임규완

#### **Session 18 Sensor Interfaces and References**

"Sensor Interfaces and References" 라는 주제로 만들어진 이번 A-SSCC 의 18번 session에서는 총 5편의 논문이 발표되었다. 5개의 논문 중 4개는 이미지센서나 온도센서 등을 위한 analog-frontend 및 ADC를 다룬 논문이고, 1개의 논문은 MOSFET을 이용한 voltage reference를 다루었다. 이번 review에서는 sensor interface에 관한 3개의 논문을 다루어 보겠다.

#### #18-1

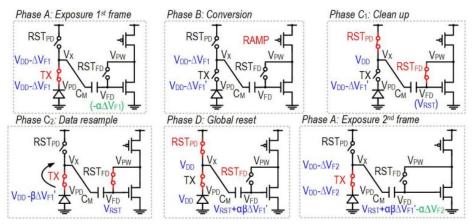

[그림 1] 논문에서 제안된 pixel 구조

본 논문에서는 적은 transistor 및 capacitor (6T1C)을 사용하여 motion-detection(MD) 및 local binary pattern (LBP) extraction을 수행한 image sensor을 발표하였다. Frame간 차이를 가지고 motion detection을 수행하는 기존 image sensor은 pixel 내부에 이전 frame data를 저장하는 요소가 필요했고, 이로 인해 복잡한 pixel 구조를 사용하여 fill factor (FF)가 낮아지게 되었다.

본 논문은 이와 같은 단점을 해소하고자 floating-diffusion (FD) node의 cap과 photodiode 사이에 capacitor을 삽입하고, 분리된 FD node의 capacitor을 이용하여 이전 frame의 data를 저장하는 방법을 사용하였다. 또한, 이전 frame data와 현재 frame data 사이의 차이 값의 계산은, 삽입된 capacitor을 통한 capacitive coupling 및 coupling time의 조절을 통하여 구현하였다. 상세한 pixel 구조는 [그림 1]에 설명되어 있다.

저장된 data의 readout은 data가 저장된 cap이 gate에 연결된 NMOS와 이의 drain에 연결된 PMOS를 이용하여 수행하였다. PMOS의 gate 전압을 ramp 형태로 조절하여 PMOS의 drain 전압이 transition 되는 순간이 저장 data에 따라 달라지는 방식을 통해 저장 data를 pulse 형태로

PWM하여 readout 하였다. 출력 파형이 pulse 형태로 나오기 때문에, 단순한 logic gate를 통한 pulse의 비교를 통해 LBP 및 range of interest (ROI) extraction을 수행하였다.

제안하는 image sensor은 compact한 pixel 구조에서 frame-based MD를 수행한 데 큰 의미가 있다. 하지만 이전 frame data를 cap에 저장하기 위한 동작 때문에 charge integration time이 짧아지는 데서 오는 conversion gain 저하가 우려되고, 삽입된 capacitor과 FD의 capacitor의 ratio variation에 따른 calibration 부담이 늘어나는 부분이 우려된다.

#### #18-2

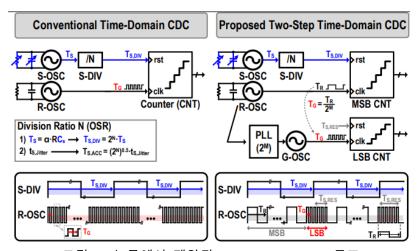

[그림 2] 논문에서 제안된 two-step TD-CDC 구조

본 논문은 oscillator을 이용한 counter-based time-domain RC-to-digital converter을 제안하였다. 기존의 RC-to-digital converter은 delta-sigma modulation (DSM) 또는 SAR 방식과 DSM 방식을 조합한 two-step conversion 방식을 사용하였다. 하지만 이러한 방식은 sensor의 출력을 전압으로 변환하기 때문에 voltage supply에 의해 입력 range가 제한된다는 단점이 있다.

이러한 단점을 극복하기 위해 본 논문은 이러한 입력 제한이 없도록 sensor 출력을 clock으로 변환하여 time-domain (TD) 기반으로 RC-to-digital conversion을 하는 방식을 사용하였다. 이에 더해, 기존의 TD 기반 방식이 가지던 단점인 jitter로 인한 resolution 제한 및 높은 전력 소모 문제를 해소하고자 2개의 oscillator 및 PLL을 활용하는 구조를 제안하였다.

본 논문에서 제안하는 구조 및 conventional한 two-oscillator 기반 counting ADC의 구조가 [그림 2]에 표현되어 있다. 기존의 일반적인 two-oscillator 기반 counting ADC는 sensing oscillator (S-OSC)의 clock이 RC에 따라 가변 되도록 하고, 이 clock의 주기를 N배하여 oversampling을 한 다음, N배 된 주기를 reference oscillator (R-OSC)의 clock을 사용하여 counting 하는 구조를 취한다. 이 구조는, resolution을 높이려면 R-OSC의 주파수가 높아져야 하거나 oversampling을 더 많이 하여야 하고, 이는 sensing time이 늘어나거나 R-OSC의 전력소모가 높아지는 단점을 초래한다.

따라서 본 논문에서는 R-OSC의 전력소모를 줄이고자 R-OSC의 주파수를 낮게 설정하여 MSB conversion을 수행한 뒤, R-OSC의 주파수를 2<sup>M</sup>배 증가시켜 주는 PLL을 LSB conversion을 수행할 때만 활성화시켜 PLL로 인한 추가적인 전력소모를 최소화하였다. 이러한 구조의 사용을 통해 제

안하는 RC-to-digital converter은 같은 Q-noise 조건에서 PLL이 계속 활성화되었을 때도 기존의 two-oscillator 기반 converter보다 37.5배 낮은 전력소모를 달성하였으며, PLL의 활성화 시간을 조 절하였을 때 더욱 낮은 전력소모를 얻을 수 있었다.

제안된 RC-to-digital converter은 전력소모를 낮추기 위해 PLL을 사용한 two-step 구조를 채택하 고 PLL을 저전력으로 잘 설계하여 resolution 대비 전력소모를 잘 낮추었다는 점에서 의미가 있다.

#### #18-3

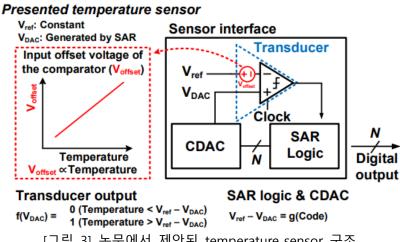

[그림 3] 논문에서 제안된 temperature sensor 구조

본 논문은 기존에 BJT 등으로 구현되던 온도 센서의 센서부를 MOSFET을 이용한 comparator의 offset으로 구현하고, 기존에 널리 사용되고 많이 분석된 SAR ADC에 앞서 구현된 comparator을 사용하여 온도 센서를 구현하였다. 기존에 많이 사용되던 BJT 기반의 센서들은 공정에 따라 구현 이 어려운 경우가 있을 수 있는데, 제안하는 논문은 이러한 단점을 극복하여 가장 일반적인 MOSFET 기반으로 온도 센서를 구현하고, 이에 더해 간단한 구조로 센서를 구현하여 전력 소모를 줄이고 빠르게 센싱 하는 것에 목표를 두었다.

제안하는 온도 센서의 구조는 [그림 3]과 같다. 이는 널리 쓰이는 SAR ADC의 구조와 동일한 구 조를 지니고 있는데, 제안된 구조에서 입력 전압에 해당하는 부분은  $V_{ref}$  +  $V_{offset}$  으로,  $V_{offset}$ 에 해 당하는 comparator의 offset이 온도에 선형적으로 비례하게 증가하도록 설계하였다. 온도에 선형 적으로 비례하는 comparator offset은, 일반적으로 많이 쓰이는 strongarm latch comparator의 입 력단 MOSFET을 sub-threshold로 만들어 이의 PTAT 특성을 활용하여 구현하였다. 이렇게 구현된 comparator offset의 temperature coefficient는 differential input MOSFET의 상대적인 size 차이로 만 결정되기 때문에, 일정한 temperature coefficient 값을 가진다고 할 수 있다.

제안된 온도 센서의 측정 결과를 살펴 보면, 0.13K의 resolution에서 38.69 pJ/conversion의 전력 소모를 달성하였고, 이는 비슷한 resolution의 온도 센서 중 낮은 수치로써 경쟁력 있는 수치를 달성하였다고 할 수 있다. 이러한 수치는 앞서 설명한대로 간단한 구조를 사용하였기 때문에 전 력소모를 낮출 수 있었던 것으로 보인다. 다만, 온도 센서의 inaccuracy를 살펴보면, 2-point calibration을 수행하였음에도 -2.54/2.16도의 inaccuracy를 가진다. 이는 transducer의 역할을 하는 MOSFET의 variation에서 발생한 것으로 보이고, 이러한 variation은 MOSFET이 태생적으로 BJT 대 비 좋지 못한 특성을 가지기 때문에 아직 극복하지 못한 부분으로 보인다. 제안된 온도 센서는, 단순한 구조와 간단한 design 방법을 통해 온도 센서를 구현하였다는 데에 의의가 있다.

## 저자정보

## 명예기자 임규완

● 소 속: KAIST 전기및전자공학과 박사과정

• 연구분야 : Display Driver IC, Readout IC

• 이 메일: limkw@kaist.ac.kr

• 홈페이지 : https://ICdesignlab.net