### 2024 International Solid-State Circuits Conference

## (ISSCC) Review

연세대학교 시스템반도체공학과 박관서 교수

**Topic: Wireline**

#### Session 7: Ultra-High Speed Wireline

이번 ISSCC2024의 Session 7은 Ultra-High Speed Wireline이라는 주제로 총 9편의 논문이 발표되었다. 이 세션에서는 초고속 유선통신을 위한 송수신기 개발에서 데이터 속도와 에너지 효율을 높이는 것에 중점을 두었고 고성능 클록 생성기에 대한 논문들도 발표되었다.

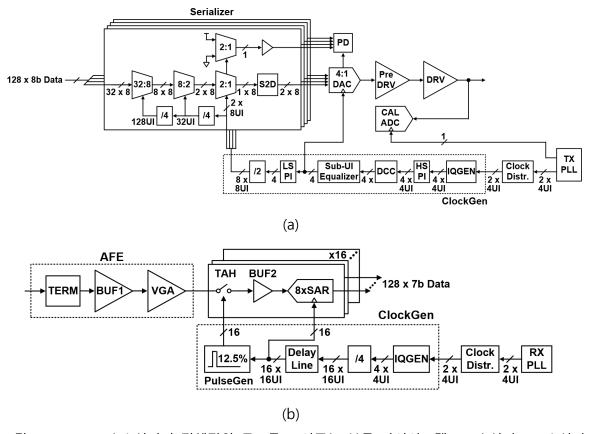

#7-1 Marvell, 본 논문은 DSP기반의 초고속 송수신기에 대한 발표이고 5nm FinFET에서 구현하였다. 최초의 212Gb/s의 동작속도를 가지고 direct optical detection을 위한 PAM-4 송수신기이고 아날로그 에너지 효율이 2.69pJ/b으로 기존 최고 성능의 112Gb/s 송수신기들과 비슷한 수준을 달성했다. 그림 1과 같이 송신기는 4-way time interleaved DAC과 linear driver로 구성되어 있고 RJ (72fsrms), Amplitude (0.78Vppd), RLM (0.98)의 성능을 달성한다. 수신기는 wideband AFE와 128-way time-interleaved ADC로 구성되고 3-dB BW (>53GHz), SNDR (=36dB), pre-FEC BER (<1e-12)으로 고성능이면서 안정적인 동작을 제공한다. 높은 완성도의 설계면서 적은 파워를 사용하는 인상 깊은 논문이다.

[그림 1] 212Gb/s 송수신기의 전체적인 구조를 보여주는 블록 다이어그램 (a) 송신기 (b) 수신기

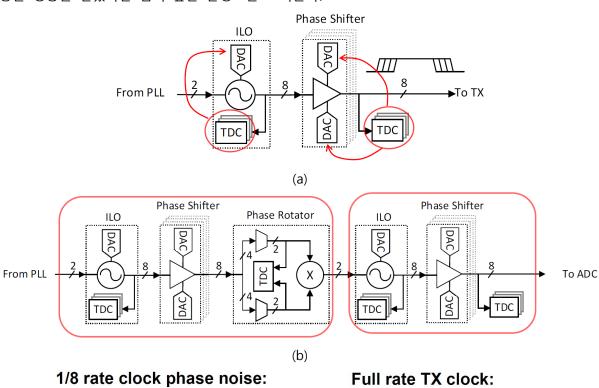

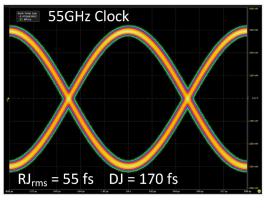

#7-3 Synopsys, 본 논문은 3nm FinFET에서 개발한 224Gb/s의 동작속도를 가지고 40dB loss까지 보상이 가능한 Long reach용 송수신기에 대한 발표이다. 고성능 송수신기를 달성하기 위해 클록쪽에 신경을 많이 쓴 논문이다. 그림2와 같이 TDC 기반의 클록 조절기를 구현하였고 이는 송신기와 수신기에 각각 적합한 구조로 포함되었다. 이 클록 조절기를 통해 송수신기에서 필요한 여러 위상의 클록을 생성하고 보정하여 RJ (55fsrms), DJ (170fs)이라는 적은 지터를 가지는 클록을 생성하였다. 송신기는 7b DAC기반의 driver과 8:1 multiplexer로 구성하였고 여기에 클록 조절기에서 만든 클록을 사용하였다. 수신기는 인버터 기반의 AFE와 7b ADC로 구성하였다. AFE는 peaking 주파수를 50GHz 이상, peaking gain 최대 20dB를 달성하였고 ADC는 50GHz에서 ENOB 4b을 얻었다. 이 송수신기는 40dB loss까지 동작을 하며 pre-FEC BER을 1e-6을 달성하였다. 초고속 송수신기에서 long reach를 타겟하여 40dB loss까지 보상을 했음에도 에너지 효율이 3pJ/b이라는 굉장히좋은 성능을 얻었다는 점이 높은 완성도를 보여준다.

#

(c)

[그림 2] (a) 송신기용 클록 조절기 (b) 수신기용 클록 조절기, (c) 클록 측정 결과

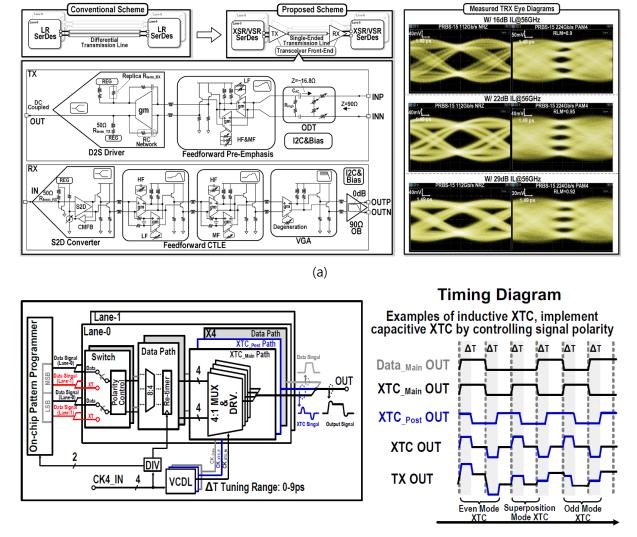

#7-5, 7-6 Southern University of Science and Technology, 단일단 시그널링을 활용한 224Gb/s, 112Gb/s급 송수신기가 같은 연구그룹에서 발표되었다. 우선, 그림3과 같이 224Gb/s PAM-4 송수신기는 long reach 어플리케이션을 타겟하여 29dB loss까지 보상하고 총 4개의 채널을 만들어서 검증을 하였다. 송신기는 differential-to-single driver를 활용하였고 signal integrity를 높이기 위해 group delay variation 보상 기법을 적용하였다. 수신기에서는 noise immunity를 좋게하기 위해 single-to-differential 변환기에서 power bounce cancellation 회로를 추가하였다. 결과적으로 SiGE 130nm 공정에서 구현된 송수신기는 224Gb/s의 동작속도와 29dB의 채널 손실에서 1E-12의 BER을 달성하였고 2.08pJ/b의 에너지 효율을 얻었다. 두번째로는 112Gb/s의 송수신기이며 Crosstalk 보상에 초점을 맞춘 연구이다. 그림 3과 같이 재구성가능한 crosstalk 보상 기법을 개발했고 TX FIR 기반으로 voltage를 빼고 더해주는 식으로 구성되었다. 수신기에서는 mismatch를 줄이는 single-to-differential 회로와 4-way interleaved 4-tap FFE를 활용하여 gain mismatch와 ISI를 줄이도록 했다. 결과적으로 28nm CMOS 공정에서 구현된 송수신기는 2.77pJ/b의 에너지 효율과 31dB loss까지 보상하며 1e-10 이하의 BER을 달성하였다.

[그림 3] (a) 224Gb/s 송수신기 블락도와 측정결과, (b) Crosstalk cancellation 기술

# 저자정보

# 박관서 교수

● 소 속 : 연세대학교 시스템반도체공학과

● 연구분야 : High Speed I/O

• 이 메 일 : kwanseo@yonsei.ac.kr

● 홈페이지 : aics.yonsei.ac.kr