이 우 주 교수 | 명지대학교 전자공학과

이 재 진 책임연구원 | 한국전자통신연구원

한 규 승 선임연구원 | 한국전자통신연구원

1. 서론

지금의 우리 사회는 4차 산업혁명이라는 공통의 주제에 주목하고 이를 성공시키기 위해 모든 방면의 자원과 노력을 쏟고 있다. 학계, 산업계, 경제계, 정치계를 통틀어 최근 발표된 모든 기획서, 제안서 및 보고서

등에서 ‘4차 산업혁명’이라는 문구가 들어가진 않은 글을 찾을 수 있을까 싶을 정도이다. 그래서일까, 이제는 4차 산업혁명이라는 문구로 시작하는 글들을 읽을 때면, ‘혁명’이라는 단어가 주는 강한 이미지에도 불구하고

어딘지 모를 진부함이 느껴지며, 이미 익숙한 내용의 재탕이 아닐까 하는 의심마저도 들곤 한다. 그럼에도 불구하고, 본 글의 제목이 ‘4차 산업혁명’이라는 문구를 포함하고 있듯이, 우리는 이 기고문을 통해 이미 잘

알려진 4차 산업혁명에 대한 이야기를 하려 한다. 다만 본 글은 저전력 설계(low power design)을 탐구하는 연구자의 관점에서 바라본 4차 산업혁명에 관한 글로서, 저전력 설계의 역사와 철학을 통해

어떻게 지금의 4차 산업혁명이 시작될 수 있었는지 생각해보고, 저전력 설계의 혁신이 어떻게 4차 산업 혁명의 성공에 이바지할 수 있을지에 관한 본 연구자의 생각을 여러분과 공유해보고자 한다.

눈이 부실 정도로 빠른 속도로 발전하고 있는 기술들과 그 결과물들을 보며 우리는 분명 무엇인가 큰 변화가 일어나고 있음을 체감하고 있고, 그것이 모두가 말하는 4차 산업혁명일 것이라 여기고 있다. IoT

(Internet-of-Things) 제품들이 속속들이 마켓에 등장하고 있고, 개인의 취향에서부터 사회 전반의 트랜드까지 예측을 해주는 빅데이터(big data) 시스템이 이미 구동하고 있으며, 난공불낙으로

여겨졌던 바둑 세계를 제패한 알파고는 어느덧 인공지능(Artificial Intelligence, AI)의 대명사가 되었다. 나아가, ‘4차 산업혁명에서 살아남는 법들’을 알려주는 수많은 서적들을 보면 마치 4차

산업혁명의 성공은 기정사실이 된 것만 같다. 하지만, 여러분들이 조금의 노력만 기울인다면, 4차 산업혁명을 이야기하는 수많은 낙관론적인 혹은 결정론적인 글들이 아닌 4차 산업혁명을 비판적 혹은 비관적인 시각으로

바라보며 4차 산업혁명의 실체의 모호함을 이야기하는 글들을 찾아낼 수 있다. 과연 무엇이 4차 산업혁명인가? 위키피디아에서 정의하듯 인공지능, 로봇공학, 사물인터넷, 무인 운송 수단(무인 항공기, 무인 자동차),

3차원 인쇄, 나노 기술과 같은 분야에서 새로운 기술 혁신이 일어나 우리의 일상생활이 바뀌게 되는 것이 4차 산업혁명인가? 또는 (좀 더 자세히) IoT 디바이스들을 통해 많은 데이터를 수집하고 빅데이터 분석을

통해 수집한 데이터들로부터 유의미한 결과를 추출하며 이를 학습시킨 AI를 만드는 것이 제 4차 산업혁명인가? 아니면 (다음은 본 연구자의 개인적인 생각이다.) IoT 디바이스들을 통해 우리 세상의 모든 것에 대한

데이터들을 수집하고 AI를 통해 이를 분석하여 P-NP 문제의 답이 P=NP 였음을 풀어내는 것인가?

‘이것이 바로 4차 산업혁명이다!’라고 모두가 동의하는 정의를 내리기에는 굉장히 많은 논의가 필요하겠지만, ‘어찌되었든 지금 무엇인가 일어나고 있다’라는 것은 우리 모두가 공감하는 바이다. 본 글은 이에 대해

‘그렇다면 왜 지금인가?’라는 질문을 던지고 그 답에 대한 고찰을 해본다. 4차 산업혁명의 실체가 무엇이든 우리는 현재 IoT, Big data, AI 기술의 눈부신 발전을 경험하고 있고, 이들은 분명 우리 세계를

변화시키고 있다. 하지만, 이 기술들은 지금의 ‘혁명(revolution)’에 의해 새로이 탄생한 것이 아닌 기존의 것들이 ‘진화(evolution)’를 한 것에 가깝다. IoT 이전에

유비쿼터스(ubiquitous)가 있었고 Big data 이전에 데이터베이스 시스템이 있었으며 AI의 뉴로모픽(neuromorphic) 컴퓨팅, 딥러닝(deep learning)의 근간인

인공신경망(neural-network) 기술은 90년대 주요 연구 주제였다. 이들이 지금의 4차 산업혁명을 이끌고 있는 기술로 진화할 수 있었던 것은 이들 내부의 근본 아이디어에 혁신(innovation)이

일어났기 때문이라기보다, 하드웨어 공정 기술 발전과 이를 뒷받침하는 소프트웨어 기술의 발전에 힘입어 기존 아이디어의 현실화(realization)가 가능해졌기 때문이다. 특히, 반도체의 미세공정 기술 발전은 IoT

디바이스를 구현함으로써 유비쿼터스의 Smart-dust 개념을 실현시킬 수 있는 토대가 되었고, GPU와 매니코어 시스템 등장시킴으로써 뉴럴 네트워크와 딥러닝의 현실 구현이 가능해졌다. 다시 말하자면, 이론 혹은

개념으로 존재하던 기술들이 반도체의 혁신적인 발전으로 인해 바로 지금 그 능력을 발휘하게 된 것이다.

그렇다면 반도체의 발전에 어떤 혁신이 일어났던 것일까? 이에 대한 대답은 여러분들도 익히 들어봤을 법한 ‘무어의 법칙’이 될 수 있다. 무어의 법칙은 인텔의 공통 창업자인 고든 무어의 경험적 관찰에 바탕을 둔

말로써, 반도체 집적회로의 성능이 24개월마다 두 배로 증가한다는 법칙이다. 무어의 법칙은 반도체 미세 공정 기술의 기하급수적인 발전에 따른 결과이자, 그 발전을 이끌어낸 원동력이기도 하였다. 일정 면적의 반도체

안에 집적할 수 있는 회로를 기하급수적으로 늘이기 위해서 반도체 공정 기술은 더욱 더 미세하고 정밀하게 스케일링(scaling) 되었고 그 결과 2000년대 초 수백 nm (예: 180nm)이었던 공정기술이

지금은 수 nm (예: 7nm)의 공정기술로 발전하였다. 공정기술이 미세해질수록 일정 면적의 반도체 칩(chip)에 더 많은 트랜지스터(transistor)를 담을 수 있게 됨으로써 칩에 더 많은 기능 장착이

가능해졌고, 반도체의 크기가 작아짐으로써 짧아진 인터커넥트(interconnect) 길이와 줄어든 트랜지스터 내 정전용량(capacitance)을 통해 칩의 동작 속도를 증가시킬 수 있었으며, 반도체 구동을 위한

공급 전압(supply voltage)을 줄일 수 있음으로써 칩의 소비 전력을 줄 일 수 있었다.

반도체 공정기술이 초미세공정(deep-submicron)으로 내려가면서 반도체 스케일링은 공정기술의 발전만으로는 해결하기 어려운 문제를 직면하게 되었다. 반도체 칩의 소비전력이 문제가 되기 시작한 것이다. 전력이

야기하는 여러 문제들 중에서도 가장 크리티컬한 문제는 바로 반도체 칩 내 단위면적당 소비전력이 올라가는 전력 밀도(power density)였다. 전력 소비는 열 발생을 의미하는데, 전력밀도가 높아짐에 따라 좁은

면적에서 많은 열이 발생되기 시작하였고 동시에 열을 방출시키기도 어려워졌다. 칩의 온도가 올라가게 되면 회로의 성능(속도)이 줄어드는 반면 소비전력은 더욱 상승하게 된다. 온도가 성능과 소비전력에 미치는 부정적

영향은 끝내 열폭주(thermal runaway)를 초래하고 이는 곧 칩이 타버리는 결과를 낳는다. 즉, 초미세공정기술에 힘입어 초집적 칩을 구현할 수 있다 하더라도, 그 칩을 정상 동작시킬 수 없게 된 것이다.

이 문제를 해결하기 위해 등장한 것이 바로 저전력 설계 기술이다. 저전력 설계 기술은 (많은 이들이 오인하는 것처럼) 단순히 소비전력을 줄여서 오랫동안 칩을 동작시키기 위함 보다는, 반도체 스케일링을 지속하고 이를

통해 더욱 더 고집적 칩을 만들기 위해 탄생하였다고 할 수 있다. 대표적인 저전력 설계 기술로서, 전력상황에 따라 동적으로 칩의 전압레벨과 동작속도를 변화시킴으로써 소비전력을 획기적으로 줄일 수 있는 DVFS

(Dynamic voltage and frequency scaling) 기술이 개발되었으며, 사용을 하지 않는 블럭 또는 모듈의 전력공급 또는 클럭(clock)공급을 차단(gating)함으로써 소비전력을 줄이는

DPM (dynamic power management) 기술들이 제안되었다. 열폭주를 막기 위한 DTM (dynamic thermal management) 기술들도 함께 발전해왔다. 그리고 이에 힘입어, 반도체

스케일링이 지속될 수 있었음은 물론이다.

DVFS, DPM, DTM은 지금도 일선에서 IoT, AI 칩들의 소비전력을 줄이는 역할을 수행하고 있다. 하지만 이들이 지속적인 반도체 스케일링이 가능하도록 주도할 수 있던 시기는 2000년대 중반까지였다.

우리가 초점을 맞추고 있는 ‘지금’의 IoT, AI 칩들은 최근 2010년대 중반에 이르러서야 등장하기 시작했는데, 이는 곧 2000년 대 중반부터 최근까지 반도체 기술에 새로운 혁신이 있었음을 의미한다. 그리고

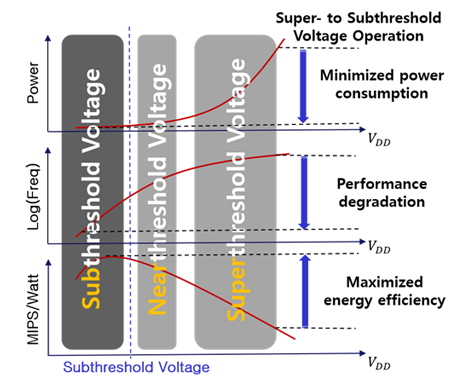

본 연구자는 그 혁신이 바로 초저전압(ultra-low voltage, ULV) 동작 회로 기술과, FinFET, FD-SOI와 같은 차세대 반도체 공정 기술이었다고 생각한다. 특히 저전력 설계 관점에서 ULV

동작 회로 기술은 기존의 저전력 설계 기술로는 도달할 수 없었던 이론적 최고 에너지 효율을 도달 가능하게 하는 기술로서, 기존의 저전력 설계 기술을 뛰어넘는 초저전력(ultra-low power, ULP) 기술이다

(그림 1 참조). 사실 2000년대 처음 등장한 ULV 동작 회로 기술은 초저전력을 실현할 수 있었음에도 불구하고 속도가 크게 저하된다는 치명적인 단점을 가지고 있었다. 하지만 IoT 시대가 도래하며, 낮은

소비전력이 최우선 요건인 (아울러 고성능은 그리 중요치 않게 여기는) IoT 디바이스들의 특징으로 인해 ULV 동작 회로 기술은 IoT 디바이스에 가장 어울리는 기술로 각광받게 되었다. 나아가 ULV 동작 회로

기술은 최근의 뉴로모픽 (neuromorphic) 컴퓨팅이 보이는 높은 병렬성(parallelism)과 맞물려 (마치 기다렸다는 듯이) 온 칩 뉴럴 네트워크(on-chip neural network) 실현을 위한

필수 기술이 되었다.

이렇듯 저전력 설계 기술은 반도체의 발전을 견인하며 혁명을 준비하는 원동력이 되었고, 최근엔 초저전력 설계 기술이라는 혁신을 통해 지금의 혁명을 시작시킬 수 있었다. 자, 그렇다면 이제 저전력 설계 기술은 혁명의

불씨를 당긴 것에 만족하면서 IoT, Big data, AI 기술들이 혁명을 완성하길 기다리고 있으면 되는 것일까? 이에 대해 본 연구자는 ‘아니다, 분명히 저전력 설계 기술이 혁명의 성공을 이끌 수 있는 혁신을

제공할 것이다’라는 믿음을 가지고, 그것이 무엇인가를 찾기 위한 연구를 진행하고 있다. 그리고 이어지는 글을 통해 우리가 지금까지 찾아온 그 실마리에 대한 이야기를 해보려 한다.

[그림 1] 공급전압에 따른 소비전력, 성능 및 에너지효율 그래프

2. 저전력 설계 기술의 새로운 패러다임

지금까지의 저전력 기술들은 모두 칩의 온도(chip temperature)를 부정적인 요인(negative factor)로만 여겨왔다. 그도 그럴 것이, 공급전압레벨이 Super-threshold voltage로 동작하는 회로들은 모두 칩의 온도가 올라갈수록 속도가 느려지고, 더 많은 전력을 소비하였기 때문이다. 칩 온도 T에 따른 회로의 속도와 소비전력을 이론적으로 살펴보도록 하자. 먼저, 칩의 딜레이 τ_D는 다음의 식으로 표현할 수 있다.

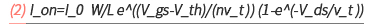

(1)에서 C는 칩 내 회로의 capacitance이고, V_DD는 공급전압이다. I_on은 on-current로서 다음의 식으로 표현할 수 있다.

(2)에서 V_gs, V_ds, V_th는 각각 게이트-소스(gate-source), 드레인-소스(drain-source), 문턱(threshold) 전압을 나타내며, I_0는 V_gs=V_th인 경우를 통해 구해낸 sub-threshold current를 의미한다. n은 sub-threshold factor이고 v_t는 열전압(thermal voltage)로서 v_t=kT/q이다 (k는 볼츠만 상수, q는 전하량이다). 식 (2)를 온도에 따른 함수로 다시 서술하면 다음과 같다.

(3)에서 μ(T), V_th (T), S(T)는 모두 온도에 따른 함수로서, 온도가 올라감에 따라 μ(T), V_th (T)는 감소하고 S(T)는 증가한다. 기존의 회로들이 모두 super-threshold

voltage (V_DD≫V_th)로 동작을 했었기에, 식 (3)에서 V_th (T)가 I_on에 미치는 효과는 미비하였다. 따라서 온도가 올라감에 따라 I_on이 감소하는 것이 일반적이었다. 그 결과, 식

(1)을 통해 알 수 있듯이, 온도가 올라감에 따라 τ_D는 증가하였고, 동시에 속도(1/τ_D)는 감소하였다.

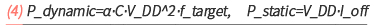

한편, 칩의 소비전력 P는 크게 동적전력(dynamic power, P_dynamic)과 누설전력(static or leakage power, P_static)으로 구분할 수 있으며

P=P_dynamic+P_static이다. P_dynamic과 P_static는 각각 다음과 같이 간단히 표현할 수 있다.

위 식에서 α는 activity factor이며, f_target와 I_off는 각각 동작 주파수, off-current이다. 식 (4)에서 I_off는 I_on과 비슷하게 온도 T에 관한 함수로 표현될 수 있으며,

온도가 올라감에 따라 I_off도 증가한다. 따라서 온도가 증가함에 따라 P_static은 증가하게 된다 (P_dynamic은 온도의 변화와 무관하다). 2000년대 초까지 super-threshold

voltage로 동작하는 회로에서는 P_dynamic이 P_static보다 훨씬 큰 경향을 보였기에 T의 변화에 따른 회로 전체 소비전력의 변화가 크리티컬하지 않았지만, 이후 지속적인 반도체 스케일링으로 인해 전체

소비전력에서 P_static이 차지하는 비중이 커짐에 따라 T가 상승함에 따라 P가 증가하는 것이 중요하게 되었다.

super-threshold voltage로 동작하는 회로에서 회로의 온도가 칩의 성능과 소비전력에 부정적으로 영향을 미쳤던 것과 달리, ULV (near-/sub-threshold voltage) 로 동작하는

특성에서는 회로의 온도가 상승할수록 회로의 딜레이가 줄어들고 성능이 좋아지는 현상이 발견되었다 (소비전력은 여전히 증가한다) [1-5]. 최근에는 상용 칩에서도 이와 같은 현상이 나타남이 보고되기도 하였다

[6,7]. 이는 수식 (1)과 (3)을 통해서도 유추해볼 수 있는데, 수식 (3)에서 T가 증가함에 따라 V_th (T)가 줄어드는 효과가 I_on을 증가를 유발하고 (V_DD가 V_th에 가깝기 때문), 이로

인해 수식 (1)의 τ_D가 줄어들게 됨을 알 수 있다.

즉, ULV 영역에서는 온도가 증가함에 따라 딜레이가 줄어드는 현상이 발생한다. 본 연구자들은 기존의 온도-딜레이에 관한 틀을 뒤엎는 이 현상에 주목하였고, 여러 종류의 반도체 공정들을 기반으로 한 회로 실험을

통해 한 가지 더 중요한 사실을 알아챌 수 있었다. 그것은 바로, ULV로 구동하는 회로의 온도-딜레이 특성이 super-threshold voltage로 동작하는 회로의 온도-딜레이 특성보다 훨씬 더 급격하다는

것이었다. 가령 온도 변화가 0℃에서 100℃로 바뀔 경우 super-threshold voltage 구동 회로의 속도가 약 0.8배로 줄어들었다면, ULV 구동 회로의 속도는 약 20배가량 늘어날 정도로 온도에

대한 딜레이의 민감도가 컸다. 본 연구자는 기존의 상식과 정반대인 이 현상을 “온도역전현상(temperature effect inversion, TEI)”이라고 명명하였다 [8]. 그림 2는 여러 종류의 반도체

공정 기반 회로를 바탕으로 수행한 실험 결과이며, 모두에게서 TEI 현상이 일어남을 분명하게 보여준다.

우리는 TEI 현상을 이용하면 새로운 저전력 설계 패러다임을 만들 수 있다는 생각을 하였다. 온도를 부정적인 요인으로 여기고, 온도 증가를 억제시키는 것이 늘 이상적이었던 기존의 저전력 설계 철학을 뒤엎고, 온도를

회로의 속도를 증가시킬 수 있는 긍정적인 요인으로 생각하기 시작하자 우리가 새로이 개발할 수 있는 수많은 저전력 설계 기술들이 보이기 시작하였다.

[그림 2] 다양한 반도체 공정을 기반으로 한 회로들의 온도-딜레이 시뮬레이션 결과

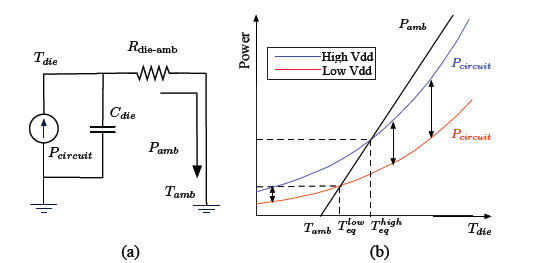

[그림 3] (a) 칩의 thermal modeling을 위한 회로, (b) 열평형에 따른 T_eq도출 그래프

우리가 TEI 현상을 이용하여 처음 제안한 기술은 다음과 같다. 상용 칩들의 동작주파수 f_target은 어떠한 환경에서라도 칩이 보장할 수 있는 최소한의 속도로 결정이 된다 (즉, worst case corner에서 f_target이 결정 된다). 이를테면, super-threshold voltage로 구동하는 칩은 칩이 동작을 보장하는 온도 범위 중 가장 높은 온도에서 결정된 속도를 통해 칩의 f_target을 결정하게 된다. 반대로 ULV로 동작하는 칩들의 f_target은 칩이 동작 온도 범위 중 가장 낮은 온도의 속도를 기반으로 결정될 것이다. 가령 ULV 구동 칩이 -25℃에서 125℃까지 동작하는 칩이라면, 이 칩의 f_target은 -25℃에서의 속도로 결정이 될 터이다. 자, 이제 그럼 칩이 상온 25℃에서 동작한다고 가정해보자. 칩이 열평형(thermal equilibrium)이 일어나는 온도를 T_eq라고 했을 때, T_eq에 도달하기까지 칩의 온도는 서서히 올라가게 될 것이다. 이 과정을 그림 3과 같이 간단히 모델링할 수도 있는데, 이에 관심이 있는 사람은 레퍼런스 [8] 을 참조하길 바란다. 칩의 온도가 올라가면서 어떤 일정 온도에 도달하게 되면, TEI 현상에 의해 더 낮은 V_DD로 회로를 구동시키더라도 f_target은 보장이 된다. 수식 (4)를 통해 알 수 있듯, 낮은 V_DD를 사용할수록 회로의 소비전력은 급격히 줄어들게 된다. 즉, TEI 현상을 활용하여 칩의 성능을 유지하면서 동작전압을 낮추어 소비전력을 줄일 수 있는 것이다.

(a)칩의 문턱온도(T_th)예,칩 온도가 T th에 도달하여 전압을 낮췄을 경우 칩 온도가

(b) 올라가는경우, (c) 내려가는 경우의 소비전력 절감 효과 그래프

[그림 4] 20nm FinFET 기반 FO4 인버터체인 회로를 기반으로한 시뮬레이션 결과

원래의 V_DD보다 더 낮은 공급전압 V_target을 사용하면서 칩의 속도를 유지할 수 있는 온도를 문턱온도(T_th^(V_DD→V_target ))라 정의해보자. 그림 4 (a)는 0.75V로 동작하는 20nm

FinFET 기반의 FO4 인버터체인(inverter chain)회로의 T_th들을 보여준다. 실험 결과에 따르면, 주어진 회로는 18℃에서 0.7V로 낮출 수 있고, 61℃에서 0.65V까지도 낮추면서 같은

속도를 유지할 수 있다. 한편, 칩의 온도 변화는 T_eq에 따라 달라지게 된다. 가령 0.7V로 동작하는 회로의 T_eq가 50℃라면 칩의 온도는 50℃에 이르러 변화를 멈출 것이다. 이 경우, 회로가

0.75V로 동작하기 시작해서 18℃에 이르게 되면 우리는 V_DD를 0.7V로 내려 소비전력을 절감시킬 수 있고, 이 상태로 회로는 50℃까지 온도가 오르게 될 것이다. 이때의 절감되는 소비전력을 보여주는 예가

그림 4 (b) 이다. 그럼 과연 0.7V로 동작하는 회로의 가 70℃인 경우는 어떠할까? 우리는 회로의 온도가 61℃에 이르렀을 때 V_DD를 한 단계 더 낮춰 0.65V로 동작시킬 수 있다. 하지만 만일

0.65V로 동작하는 회로의 T_eq가 61℃보다 낮은 온도라면, 문제가 발생하게 된다. 0.65V로 낮추고 나면 이내 회로의 온도가 61℃보다 떨어지게 되고, 회로의 속도 유지되지 않는다. 이럴 경우, 우리는

61℃가 되자마자 바로 V_DD를 0.65V로 내리지 않고, 일정 시간을 기다려 칩의 온도가 올라가길 기다린 다음 이후에 voltage down-scaling(0.7V→0.65V)을 수행할 수 있다. 그리고

voltage down-scaling의 결과로 온도가 떨어지게 되어 61℃에 이르게 되면 다시 voltages up-scaling(0.65V→0.7V)을 통해 온도를 올리게 되고 회로의 속도를 유지시킬 수 있다.

이 방법을 통한 예제의 실험 결과는 그림 4의 (b)와 같다.

우리는 앞서 논의한 예제를 기반으로 좀 더 보편적인 TEI-aware Voltage Scaling 알고리즘을 개발하였고, 이를 TEI-power라 명하였다 [8, 9]. TEI-power는 Algorithm 1에

서술되어 있다. 자세한 설명은 레퍼런스[8]을 참조하기 바란다.

한편, TEI-power를 실제 회로에 구현하기 위해서는 반드시 칩 내 인터커넥트(interconnect, 또는 wire) 딜레이를 고려해야만 한다. 반도체 스케일링 덕분에 소자들의 크기가 줄어들었음에도 불구하고,

칩에 여러 기능들이 집적되면서 칩 사이즈와 집적도가 커지고 있다. 이는 long global wire들의 인터커넥트 딜레이가 증가하는 결과를 낳았고, 이들이 칩 전체 딜레이에 미치는 영향이 커졌다. 인터커넥트

딜레이 τ_wire를 온도의 함수로 표현하면 다음과 같다.

위 식에서 r_(wire,0)은 resistance per unit length이고 β 는 temperature coefficient of resistance (1/℃) 이다. 수식 (5)에서 알 수 있듯이 인터커넥트 딜레이TEI 현상을 따르지 않고, 오히려 기존의 super-threshold voltage 구동 회로와 같이 온도가 올라감에 따라 딜레이가 커지게 된다. 따라서 인터커넥트 딜레이의 비중이 큰 칩에 TEI-power를 적용하기가 어려워진다.

[그림 5] TEI-power 알고리즘

위 문제를 해결하기 위해, 우리는 인터커넥트에 버퍼를 삽입(buffer insertion)하는 기술에 주목하였다. 인터커넥트 딜레이를 줄이기 위한 가장 대표적인 방법이 바로 buffer insertion 기술이다.

Buffer는 인버터들로 구성된 로직 게이트이고, TEI 현상을 보인다. 따라서 Buffer가 삽입된 인터커넥트는 온도가 상승함에 따라 그 딜레이가 커지는 정도가 줄어들거나, 혹은 많은 버퍼가 삽입된 경우

딜레이가 줄어들게 된다. 물론 버퍼들을 많이 집어넣을수록 TEI 현상이 두드러지게 되어 TEI-power를 적용하는데 도움이 되겠지만, 버퍼 자체의 크기와 소비전력이 문제가 될 수 있다. 따라서 이들을 고려한

설계가 반드시 필요하며, 레퍼런스 [9, 10]은 이에 관한 자세한 최적화 설계 방법을 제안하고 있다.

TEI-power는 칩의 성능을 유지하면서 동작전압을 낮추어 소비전력을 줄이기에 에너지(전력x시간)을 줄이는 효과가 있다. 그렇다면 과연 칩의 성능을 유지하는 것이 아닌, 온도가 올라감에 따라 높아진 성능을 그대로

사용하면 어떤 결과를 얻게 될까? 레퍼런스 [11, 12]는 TEI 현상을 활용한 터보 모드(turbo-mode)로 방법에 관한 아이디어를 제안하였고, TEI-turbo 기술이라고 이름 지었다. TEI-turbo는

기존의 터보 기술과 비교하여 Voltage upscaling이 필요 없다는 큰 장점이 있다. 이전까지 존재하는 모든 터보모드들은 칩의 동작주파수를 올리기 위해 반드시 동작전압을 증가시켜야만 했다. 따라서, 수식

(4)에서 알 수 있듯이, 기존의 터보모드들은 급격한 소비전력 증가라는 희생을 동반할 수밖에 없었다. 하지만 TEI 현상을 이용한다면 공급전압의 증가 없이도, 온도의 변화만으로 동작주파수를 증가시킬 수가 있다.

즉, TEI-turbo는 f_target의 증가에 따라 선형비례로 늘어난 P_dynamic 변화만큼 만의 소비전력 증가를 유발한다. 나아가, 에너지의 측면에서 바라본다면 TEI-turbo는 소비전력이 증가하여 잃은

손해보다 더 빠른 시간 내로 주어진 일을 마칠 수 있음으로써, 에너지 절감 효과를 가능하게 한다 (물론, 일이 memory-bound task여서 터보모드를 썼음에도 불구하고 일을 마치는 시간에 별 차이가 없다면

에너지가 오히려 증가할 수도 있다. 하지만 우리는 주어진 일의 특성에 따라 터보모드를 사용할 것이기에 터보모드를 사용하면 처리시간이 줄어든다고 가정한다). 특히 ULV 구동 칩의 소비전력 중 P_static이

차지하는 정도가 크기 때문에, 처리시간을 감소시킴으로써 누설 에너지를 줄이는 것은 전체 칩의 사용 에너지를 줄이는데 큰 기여를 한다.

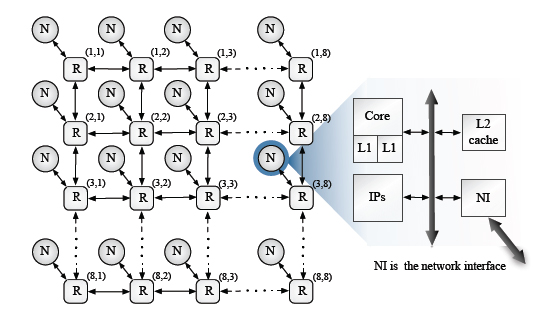

[그림 6] Mesh 토폴로지의 Network-on-Chip 구조

한편, 우리는 최근 네트워크 온 칩(Network-on-Chip, NoC)를 개발하면서 TEI 현상을 이용하여 NoC의 소비전력을 크게 절감할 수 있는 기술을 제안하였다. 참고로 NoC는 칩 내 수많은 모듈간의

통신을 효과적으로 컨트롤하기 위한 IP (intellectual property)로서 현대의 대부분의 칩들은 NoC를 통해 칩 내 네트워크를 구현하고 있다. NoC가 보편적으로 사용이 되기 시작하면서 NoC의

소비전력이 칩 전체 소비전력에서 차지하는 비중이 늘어나고 있기에, 최근 NoC의 소비전력을 줄이기 위한 다양한 저전력 설계 방법들이 제안되고 있다. 이에, 우리는 TEI 현상을 통해 NoC 저전력 설계 방법의

새로운 패러다임을 제안하였다 [13].

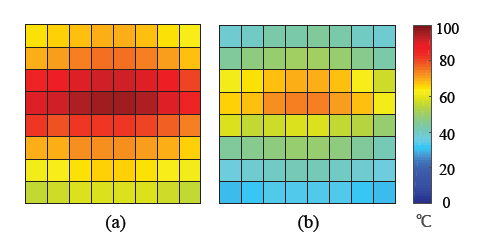

우리가 대상으로 한 NoC의 구조는 그림6과 같은 전형적인 메쉬(mesh) 토폴로지의 NoC로서, 각각의 라우터들이 ULV로 구동되는 회로로 구현된 ULP-NoC이다. 그림 내 R은 라우터(router)를 의미하고

N은 프로세싱 노드(node)를 의미하며, 노드 내에는 코어(Core)와 캐시(cache), 네트워크 인터페이스(network interface, NI) 및 각종 IP들이 포함되어 있다. 우리는 NoC가 구동이 될

때, 각각의 라우터마다 다른 온도를 가질 수 있다는 것에 주목하였다. 그림 7은 그림 6의 NoC가 보이는 온도분포를 보여주는 예로서 주변 온도(ambient temperature)가 높을 경우 (그림 8.

(a)), 낮을 경우 (그림 7. (b))의 thermal map이다. NoC는 ULV로 구동을 하기에 TEI 현상이 나타날 것이고, 따라서 높은 온도 상태인 라우터들일수록 더 빠르게 구동할 것이다.

우리는 이를 이용하여, 더 빠르게 돌 수 있는 라우터들을 실제로 더 빠르게 동작시키면서 네트워크의 패킷(packet)처리를 더 많이 하게하고, 대신 느리게 동작하는 라우터들은 전력을 제거(power-gate)해서

소비전력을 줄이자는 제안을 하고, 이 방법을 power-gating and frequency scaling (PGFS)라 정했다. 빠르게 동작하는 (온도가 상대적을 높은) 라우터들이 소비전력을 위해 전력을 차단한

라우터들의 몫까지 일을 수행하게 함으로써 NoC의 전체 성능이 유지된다. 이때, 같이 높은 온도로 더 빨리 동작하는 NoC들은 동작전압을 늘이지 않고 동작주파수만을 늘였기에 (TEI-turbo 모드의 경우처럼),

빠른 NoC로 인해 유발하는 소비전력증가는 오로지 P_dynamic의 f_target에 따른 선형증가뿐이다. 반면 낮은 온도의 라우터들은 전력이 완전히 차단되므로 이를 통해 상당량의 소비전력을 절감할 수 있다.

우리는 메쉬 토폴로지의 NoC 구조 특성상 가장자리(edge)에 위치한 라우터들이 전체 성능에 영향을 미치는 정도가 낮다는 특성을 이용하여, 가장자리의 낮은 온도의 라우터들부터 순차적으로 라우터들을 끄는

정책(policy)를 제안하였다. 아울러 라우터들을 키고 끔에 따라 새롭게 변형된 NoC의 구조에 따라 라우터드 간의 패스(path)를 재구성하기 위한 알고리즘도 제안하였다. 제안하는 NoC 아키텍처는 그림 8와

같으며, 자세한 알고리즘은 레퍼런스 [13]을 참조하기 바란다.

[그림 7] NoC내 라우터/노드들의 온도분포 <예: 주변 온도가 (a) 높을 경우 (b)낮을 경우>

[그림 8] 제안한 NoC 아키텍처

지금까지 살펴본 TEI-power, TEI-turbo 및 PGFS 저전력 설계 기술들은 모두 약 30%이상의 소비전력/에너지 감소 결과를 실험을 통해 입증하였다. 근래에 발표된 저전력에 관한 기술들 중 소비전력 절감 효과가 두 자릿수(%)가 넘는 업적을 찾아보기 힘들다는 것만 보아도, TEI 현상을 이용하는 것이 얼마나 큰 이득을 주는지 짐작해볼 수 있다. 우리는 현재 가칭 TEI-BB, TEI-GPU 및 TEI-NN이라는 프로젝트를 진행하고 있으며, 그 결과를 통해 TEI-aware 저전력 설계가 저전력 설계의 새로운 패러다임이 되길 희망해본다.

3. 결론

우리는 TEI-aware 저전력 설계 기술들을 개발함으로써, 온도를 더 이상 부정적인 요인이 아닌 소비전력/에너지를 절감할 수 있는 긍정의 도메인으로 가져왔다. 지금까지 개발한 기술들과 기술을 개발하며 얻은 통찰력(insight)를 바탕으로 우리는 현재 저전력 설계의 혁신을 위한 연구에 매진하고 있으며, 가까운 미래에 그 결과를 발표할 수 있을 것이라 기대하고 있다. 궁극적으로, 우리가 목표하는 새로운 저전력 설계 패러다임이 제4차 산업혁명의 성공에 큰 공헌을 할 수 있길 희망한다. 본 기고문을 읽어준 여러분들께 감사의 말을 전하며, 본 글을 마친다.

- [1]A. Calimera, E. Macii, M. Poncino, and R. I. Bahar. Reducing leakage power by accounting for temperature inversion dependence in dual-Vt synthesized circuits. ISLPED. 217–220. 2008.

- [2]S. Soleimani, A. Afzali-Kusha, and B. Forouzandeh. Temperature dependence of propagation delay characteristic in FinFET circuits. Microelectronics. 276–279. 2008.

- [3]Yu Pu, X. Zhang, J. Huang, A. Muramatsu, M. Nomura, K. Hirairi, H. Takata, et al. Misleading energy and performance claims in sub/ near threshold digital systems. ICCAD. 625–631. 2010.

- [4]M. Ashoueil, H. Luijmes, J. Stuijt, and J. Huisken. Novel wide voltage range level shifter for nearthreshold design, ICECS. 285–288. 2010.

- [5]A. Calimera, E. Macii, M. Poncino, and R. I. Bahar. Temperature-insensitive synthesis using multi-Vt libraries. GLVLSI. 5–10, 2008.

- [6]Y. Zu, W. Huang, I. Paul and V. J. Reddi, "Ti-states: Processor power management in the temperature inversion region," MICRO, pp. 1-13, 2016

- [7]J. Park and H. Cha, Aggressive Voltage and Temperature Control for Power Saving in Mobile Application Processors, in IEEE TMC, vol. PP, no. 99, pp. 1-1. 2017

- [8]W. Lee, Y.Wang, T. Cui, S. Nazarian, and M. Pedram. Dynamic thermal management for FinFET-based circuits exploiting the temperature effect inversion phenomenon. ISLPED, 105–110. 2014.

- [9]W Lee, K Han, Y Wang, T Cui, S Nazarian, M Pedram, TEI-power: Temperature Effect Inversion--Aware Dynamic Thermal Management. ACM TODAES, 22 (3), 51, 2017

- [10]S. N. Shahsavani, A. Shafaei, S. Nazarian and M. Pedram, "A thermally-aware energy minimization methodology for global interconnects," DATE, pp. 1213-1218, 2017

- [11]E. Cai and D. Marculescu. TEI-Turbo: Temperature Effect Inversion-Aware Turbo Boost for FinFET-Based Multi-Core Systems. ICCAD, 500-507, 2015.

- [12]E. Cai and D. Marculescu, "Temperature Effect Inversion-Aware Power-Performance Optimization for FinFET-Based Multicore Systems," in IEEE TCAD, vol. 36, pp. 1897-1910, Nov. 2017.

- [13]K. Han, J. J. Lee, J. Lee, W. Lee and M. Pedram, "TEI-NoC: Optimizing Ultra-Low Power NoCs Exploiting the Temperature Effect Inversion," in IEEE TCAD, vol. PP, no. 99, pp. 1-1. 2017

-

이 우 주 교수

이 우 주 교수- 소속 명지대학교 전자공학과

- 주 연구분야 저전력 설계, SoC, VLSI 설계

- E-mail spacelee@mju.ac.kr

- Homepage home.mju.ac.kr/spacelee

-

이 재 진 책임연구원

이 재 진 책임연구원- 소속 한국전자통신연구원 SoC설계연구그룹

- 주 연구분야 SoC설계, 저전력 플랫폼 설계

- E-mail ceicarus@etri.re.kr

- Homepage https://www.etri.re.kr

-

한 규 승 선임연구원

한 규 승 선임연구원- 소속 한국전자통신연구원 SoC설계연구그룹

- 주 연구분야 마이크로 아키텍처 설계, 네트워크 온 칩 설계

- E-mail han@etri.re.kr

- Homepage https://www.etri.re.kr