soft-error resilient SRAM Cell

장 익 준 교수 | 경희대학교

서론

이 뉴스레터에는 본 연구 그룹이 진행하는 radiation-hardening memory/logic design 관련 연구 중 soft-error resilient SRAM design 관련 연구 결과를 일부 소개하고자 한다. 관련 논의를 위해서는 트랜지스터들이 radiation에 노출될 경우 어떠한 영향을 받는지를 우선적으로 살펴볼 필요가 있다. 높은 에너지를 가진 radiation입자들이 트랜지스터의 silicon body를 관통할 때, silicon body내에는 그 에너지에 의하여 다수의 electron-hole pair가 생성된다 (Fig. 1 참조). 생성된 electron과 hole은 자신에게 상응하는 전극으로 이동을 하게 되고 이 과정에서 회로에는 순간적으로 전기적인 noise가 발생한다. 이러한 현상을 single-event effect (SEE)라고 한다. 이러한 SEE에 의해 회로는 복구가 가능한 soft-error와 복구가 불가능한 hard-error 모두 발생할 수 있다. Soft-error의 대표적인 예는 SEE에 의해 SRAM/DRAM과 같은 volatile memory에 저장된 data가 flip되는 것이다. 이러한 현상을 single-event upset (SEU)라고 한다. SEE에 의한 hard-error의 대표적인 예는 SEE에 의해 latch-up이 triggering 되어 트랜지스터가 영구 파손되는 single-event latch-up (SEL)이 있다.

![[Figure 1] Radiation particle에 의한 Silicon 내부의 electron-hole pair 생성](./2019/05/resources/images/sub/01/02_01.jpg)

[Figure 1] Radiation particle에 의한 Silicon 내부의 electron-hole pair 생성

SEE외에도 Total Ionizing Dose (TID) 효과 역시 radiation 환경에서 CMOS기반 회로의 신뢰성에 큰 영향을 미친다. TID 효과가 발생하는 원인은 다음과 같다. Radiation 입자들이 트랜지스터의 절연체인 SiO2를 지나갈 때, SiO2 내부에도 역시 electron-hole pair가 생성된다. 이 중 electron은 mobility가 높으므로 빠르게 positive biasing이 걸린 쪽으로 흘러 나간다. 하지만. Mobility가 낮은 hole은 SiO2 내부에 있는 trap site들을 hopping 하면서 negative biasing이 걸린 방향으로 이동한다 (Fig. 2 참조). NMOS에서는 이러한 hole들은 SiO2와 silicon-body 경계면에 trap되어 축적되면서, NMOS의 threshold voltage (Vth)를 negative한 방향으로 전이하거나 subthreshold swing을 저하시킨다. 이로 인하여 NMOS에서는 leakage 전류가 급격히 증가하는 문제점이 발생한다. TID 효과 역시 트랜지스터에 미치는 영향은 영속적이며, TID에 의한 발생하는 회로의 동작 오류 역시 복구가 어려운 hard-error에 가깝다.

![[Figure 2] NMOS에서 Total Ionizing Dose 효과 발생 원리](./2019/05/resources/images/sub/01/02_02.jpg)

[Figure 2] NMOS에서 Total Ionizing Dose 효과 발생 원리

SRAM의 radiation-hardening을 하려면 SEE와 TID에 대한 대처가 모두 필요하다. 본 연구 그룹에는 이를 위한 다양한 연구를 수행 중에 있다. 이 중 이 뉴스레터에서는 SRAM에서 SEU를 극복하는 기술 및 관련 연구들에 대하여 중점적으로 설명하려고 한다. 더 나아가서는 본 연구 그룹에서 제안한 SEU에 내성이 뛰어난 새로운 SRAM cell인 we-Quatro에 대하여 논의하고자 한다.

기존의 SEU 대처 기술들 요약

SEU는 우주와 같은 극심한 방사선 환경이 아닌 일반적인 대기 환경에서도 종종 발생하므로 이에 대한 대비가 반드시 필요하다. 특히 차량용 반도체처럼 높은 신뢰성이 요구되는 곳에서 SEU를 대처하는 것은 중요하다. 근래에 차량용 반도체를 위하여 ISO26262 스펙이 발표되었다. ISO26262의 가장 높은 신뢰성 요구 수준인 ASIL-D를 만족하기 위해서는, SEU에 대한 고려가 반드시 필요하다.

현재 SRAM에서 SEU를 대처하는 가장 대표적인 기술은 EDAC(error detection and correction)과 scrubbing이다. SRAM은 주로 cache나 scratchpad memory 같은 내장형 메모리로 쓰이기 때문에, latency가 매우 중요하며 따라서 적용할 수 있는 EDAC 기술은 매우 제한 적이다. 이러한 제한 조건 때문에, single-bit correction 정도가 가능한 EDAC이 주로 쓰이며 따라서 SRAM에 SEU가 누적될 경우 발생하는 multi-bit flipping을 대처하기가 어렵다. 이러한 문제점을 대처하기 위해서 주기적으로 SRAM data를 읽고, error-bit이 발견될 경우 EDAC을 거쳐 정정하는 scrubbing 기술이 필요하다. 주목해야할 점은 scrubbing를 진행하는 동안 SRAM에 대한 접근이 일시적으로 차단되므로 지나치게 scrubbing 동작의 빈도가 높을 경우 전체 system의 성능이 크게 저하될 수 있다는 것이다. Scrubbing의 빈도가 높을 경우 이로 인한 energy 손실이 클 수 있다는 점도 문제가 될 수 있다. 근래 고집적 공정에 기반한 고성능 system에서는 SRAM의 동작 및 대기모드 공급 전압을 에너지 절약을 위해 최대한 낮추려고 한다. 이로 인하여, soft-error rate (SER)는 크게 증가할 수 있으며, 따라서 신뢰성 요구조건을 충족하기 위한 scrubbing 빈도가 크게 증가할 개연성은 충분하다.

SEU를 대처하기 위한 다른 기존 기술로는 세개의 중복 hardware를 두어 다수의 출력을 선택하는 TMR(Triple Modular Redundancy)을 들 수 있다. TMR의 경우 중복을 두는 granularity 수준에 따라 정정능력은 달라진다. Lower level에서 중복을 둘수록 정정능력은 강해지지만, latency 및 power등의 penalty는 당연히 증가한다. High level의 TMR역시 voting 회로로 인하여 latency 부담은 적지 않으며, power의 경우 3배 이상이 증가하는 문제점이 발생한다. 응용처에 따라서 이러한 문제점은 중요하지 않을 수 있으나, SER이 중요한 일부 응용처들, 예를 들면 위성, 비행기, 자동차 등에 쓰이는 반도체에서는 latency 및 power가 중요하기 때문에 TMR은 효율적인 기술이 아닐 수도 있다. 또한 방사선이 극심한 환경에서는 SER이 크게 증가하기 때문에, TMR의 정정 능력 역시 크게 떨어질 수 있다.

Soft-error Resilient SRAM Cell 관련 기존 연구 요약

-

[Figure 3] 12T DICE SRAM Cell

-

[Figure 4] 10T Quatro SRAM Cell

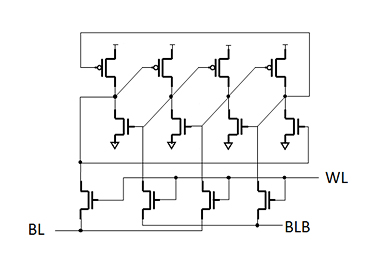

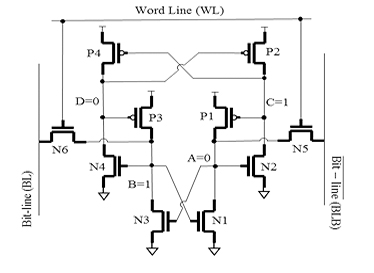

연구자들은 SEU에 대한 저항성이 큰 SRAM 셀에 대한 연구도 지속적으로 수행하여 왔다. 이러한 SRAM 셀을 이용할 경우, latency나 power 관점에서는 손실이 크지 않거나 혹은 개선도 가능할 수 있으므로 매력적이다. 지금까지 수많은 soft-error resilient SRAM 셀이 발표되었지만, 가장 대표적인 것을 소개하면 DICE와 Quatro다 (Fig. 3, 4 참조). 두 SRAM cell 모두 하나의 메모리 node가 하나의 inverter를 구성하는 PMOS와 NMOS를 동시에 driving하는 것이 아니라 다른 inverter의 PMOS와 NMOS의 input이 되는 interlock 구조를 가지고 있다. 이러한 interlock 구조 때문에 SEE 발생 시, feedback inverter의 pull-up과 pull-down이 동시에 영향을 받지 않으며 따라서 SEU에 매우 저항성이 커진다. 위 SRAM 셀들의 SEU 저항성은 많은 연구자들이 실제 측정을 통하여 검증하였다.

이러한 interlock구조는 SEU 저항성 관점에서는 매우 유리하지만, 복잡한 배선에 의해 SRAM셀의 면적이 커지는 문제점이 발생한다. DICE는 12개, Quatro는 10개의 트랜지스터로 이루어지므로, 기본적인 6T SRAM대비 셀면적이 상당히 클 수밖에 없다. 그런데, 배선이 복잡하므로 셀면적은 더욱 커져야 한다. 특히, 고집적 공정에서 쓰이는 thin-cell 타입 layout에서 배선이 복잡한 DICE와 Quatro SRAM 셀들을 구현하기는 무척 어렵다.

본 연구 그룹은 28nm FD-SOI 공정의 Logic Design Rule하에서 6T, DICE, Quatro의 thin-cell 타입 layout 구현을 시도하였다. DICE의 경우 6T대비 4배 이하로 만드는 것이 불가능하였으나, Quatro는 Cell내에서 metal-2 layer까지 배선에 사용할 경우 6T 대비 2.1배의 크기로 thin-cell 타입 layout을 구현할 수가 있었다. 이처럼 Quatro는 DICE대비 셀면적이 작으며, SEU에 대한 저항성은 기존의 연구 결과에 따르면 DICE와 거의 동등한 수준이다. 이러한 이유로 근래에는 Quatro SRAM 셀을 기반으로 한 연구가 매우 활발하다.

Quatro SRAM 셀의 문제점

![[Figure 5] 200번의 Monte-Carlo simulation에서 write 동작오류의 수](./2019/05/resources/images/sub/01/02_05.jpg)

[Figure 5] 200번의 Monte-Carlo simulation에서 write 동작오류의 수

본 연구 그룹은 Quatro SRAM 셀의 동작 안정성을 28nm FD-SOI 및 65nm CMOS 공정에서 Monte-Carlo simulation을 이용하여 검증하였다. 이 과정에서 Quatro SRAM 셀의 쓰기 동작 안정성이 매우 취약함을 발견하였다. Fig. 5는 여러가지 조건 하에서 쓰기동작을 Monte-Carlo simulation을 한 결과이다. 200번의 실험 중 상당한 쓰기 오류가 발생할 만큼 Quatro SRAM 셀은 쓰기 안정성이 취약하다. 이 실험은 65nm CMOS기반으로 이루어졌지만, 28nm FD-SOI 공정에서 실험 결과 역시 동일하다.

Figure 6은 Quatro SRAM 셀의 쓰기 안정성이 취약한 이유를 설명한 것이다. 6T SRAM에서는 access 트랜지스터들의 pull-down이 쓰기 동작을 triggering한다. 하지만, Quatro이 경우 access 트랜지스터의 pull-down이 아닌 pull-up이 쓰기 동작을 triggering한다. Access 트랜지스터는 NMOS로 구현되므로 pull-up 세기가 약하다. 따라서, 쓰기 동작 안정성이 공정 변이에서 크게 저하될 수밖에 없다. 자세한 사항은 본 연구 그룹에서 게재한 논문들을 참조하기 바란다 [1, 2].

![[Figure 6] Quatro와 6T SRAM의 쓰기 동작 비교](./2019/05/resources/images/sub/01/02_06.jpg)

[Figure 6] Quatro와 6T SRAM의 쓰기 동작 비교

we-Quatro SRAM 셀의 제안 및 검증

![[Figure 7] we-Quatro SRAM Cell](./2019/05/resources/images/sub/01/02_07.jpg)

[Figure 7] we-Quatro SRAM Cell

본 연구 그룹은 Quatro와는 달리 공정 변이에 강인하고, soft-error 저항성은 Quatro에 동등할 것으로 예상되는 새로운 SRAM 셀을 제안하였다 (Fig. 7). 제안한 SRAM셀의 이름은 we-Quatro (writability enhanced Quatro의 준말임)이라 명명하였다. 제안한 we-Quatro 셀의 기본 구조는 Quatro와 동일하지만, 모든 memory node들에 access transistor를 연결하여 동시에 접근하도록 한다. 이로 인하여, Quatro SRAM 셀 대비 2개가 더 많은 12개의 트랜지스터가 셀을 구성한다. 이렇게 we-Quatro는 Quatro대비 2개의 추가 트랜지스터가 필요함에도 불구하고, 셀면적은 Quatro와 동일하다 (<표 1> 참조). 그 이유는 Quatro의 layout에서 빈 공간에 트랜지스터를 추가하였기 때문이다.

![[Table 1] Cell 면적 비교 (6T SRAM vs. Quatro vs. we-Quatro)](./2019/05/resources/images/sub/01/02_08.jpg)

[Table 1] Cell 면적 비교 (6T SRAM vs. Quatro vs. we-Quatro)

쓰기 동작에서 4개의 memory node를 동시에 접근하므로, Quatro대비 쓰기 안정성이 크게 개선된다. 이를 검증하기 위하여 28nm FD-SOI 공정에서 Monte-Carlo Simulation을 실시하였다. Fig. 8과 Fig. 9는 세가지 SRAM 셀, 6T SRAM, Quatro, we-Quatro의 쓰기 및 읽기 동작에 대한 안정성을 1000번의 Monte-Carlo Simulation을 통해 비교한 것이다. 공정은 28nm FD-SOI를 이용하여 실험하였다. 언급한 바와 같이 Quatro의 쓰기 안정성은 매우 좋지 않았으며, 6T와 we-Quatro는 매우 안정적인 쓰기 동작을 보였다. 읽기 동작에 대해서는 Quatro가 가장 안정적인 동작을 하였으며, 6T의 읽기 안정성이 가장 불안하였다. SRAM의 경우 읽기와 쓰기 동작 안정성이 서로 상반관계에 있으므로, 두가지 안정성을 동시에 고려해야 한다. 즉 Fig. 8과 Fig. 9의 simulation 결과는 고집적 공정의 공정 변이에서 we-Quatro의 동작 안정성이 가장 우수함을 보여준다.

-

![[Figure 8] 쓰기 동작 안정성 비교 (28nm FD-SOI, VDD = 1.0V, SS Corner, 0°C)](./2019/05/resources/images/sub/01/02_09.jpg)

[Figure 8] 쓰기 동작 안정성 비교 (28nm FD-SOI, VDD = 1.0V, SS Corner, 0°C)

-

![[Figure 9] 읽기 동작 안정성 비교 (28nm FD-SOI, FS Corner, 25°C)](./2019/05/resources/images/sub/01/02_10.jpg)

[Figure 9] 읽기 동작 안정성 비교 (28nm FD-SOI, FS Corner, 25°C)

we-Quatro SRAM 4KB Macro Test-chip 제작 및 soft-error 저항성 성능 검증

본 연구팀은 we-Quatro의 SEU 저항성 성능 검증을 위하여 4KB Macro를 설계, test-chip을 구현하였다. Test-chip 내에는 6T와 Quatro 4KB Macro를 설계하여, 방사선 측정 시 비교군으로 이용하였다. Fig. 10은 Test-chip 사진과 Layout을 보여준다. 설계한 4KB Macro는 잘 동작하였으며 측정 결과 쓰기 및 읽기 안정성은 simulation 결과와 거의 유사 하였다. SEU 저항성 비교를 위한 방사선 측정은 alpha-source를 이용한 실험과 neutron 조사실험을 하였다. Neutron 조사 실험은 경희대학교에 있는 원자로 시설을 이용하였다. 구체적인 실험 결과들은 추후 국제 학술지 및 국제 학술 대회에 발표할 계획이다. 이 뉴스레터에서 실험 결과를 간략히 요약하면 we-Quatro는 Quatro와 동등 수준의 SER을 보였으며, 6T SRAM 대비 SER이 현저하게 낮았다.

![[Figure 10] 4KB we-Quatro, Quatro, 6T SRAM Macro Test-chip 사진 및 Top Layout (28nm FD-SOI 공정 이용)](./2019/05/resources/images/sub/01/02_11.jpg)

[Figure 10] 4KB we-Quatro, Quatro, 6T SRAM Macro Test-chip 사진 및 Top Layout (28nm FD-SOI 공정 이용)

결론

본 뉴스레터에서는 Radiation 환경에서 SRAM의 신뢰성에 미치는 여러가지 효과를 소개하고, 그 중 가장 중요한 SEU의 저항성 확보를 위한 SRAM 설계 기술을 요약하여 설명하였다. 그리고 기존의 soft-error 내성 SRAM 셀을 소개, 문제점을 분석하고, 그 문제점을 극복할 수 있는 새로운 SRAM 셀인 we-Quatro를 제안하였다. 실제 측정 결과 we-Quatro는 고집적 공정의 공정 변이에서 안정적인 동작을 보였으며, soft-error에 대한 저항성 또한 탁월하였다.

- [1]Le Dinh Trang Dang, Myounggon Kang, Jinsang Kim, Ik-Joon Chang, “Studying the Variation Effects of Radiation Hardened Quatro SRAM Bit-Cell,” IEEE Transaction on Nuclear Science, Vol. 63, No. 4, pp. 2399-2401, 2016 July.

- [2]Le Dinh Trang Dang, Jinsang Kim, Ik-Joon Chang, “We-Quatro: Radiation-Hardened SRAM Cell With Parametric Process Variation Tolerance,” IEEE Transaction on Nuclear Science, Vol. 64, No. 9, pp. 2489-2496, 2017 Sep.

-

장 익 준 교수

장 익 준 교수- 소속 경희대학교 전자공학과

- E-mail ichang@khu.ac.kr

-

주 연구분야

Near-threshold logic/memory 설계, Approximate

memory 설계, Radiation hardening logic/memory 설계