EDA Vendor에서 제공하는 Design Kit 활용 방법 및 특징

김 연 태 선임연구원 | IDEC 반도체설계교육센터

조 인 신 책임연구원 | IDEC 반도체설계교육센터

최근 시스템반도체에 대한 관심이 증가함에 따라 석·박사 학생들뿐만 아니라 학부생들 사이에서도 반도체설계를 경험하고자 하는 학생들이 늘어나고 있습니다. 칩 설계는 다른 분야와는 다르게 깊이 있는 지식과 다양한 경험을 요구하는 과정이므로 처음부터 올바른 정보를 바탕으로 기반을 다져가는 것이 중요합니다. 칩 설계 과정을 경험하는 가장 좋은 방법은 실제로 Fab 을 구매하여 관련 자료를 바탕으로 직접 설계 경험을 하는 것입니다. 하지만 이러한 방법은 구매를 통한 계약이 이루어져야 하므로 비용이 많이 들고, 초기 설계에 대한 대략적인 흐름을 잡는 과정에서 사용하기에는 적합하지 않습니다. 사전에 무료에 배포되는 Design Kit를 이용하여 설계 방법에 대한 학습 및 경험을 충분히 쌓고 디자인에 대한 성능이 어느 정도 확인된 후에 공정을 진행하는 것이 시간과 비용을 절약할 수 있는 방법입니다.

"본 고에서는 가장 많이 사용되는 Vendor 사의 EDK (Education Design Kit) 에 대하여 간단한 특징과 사용방법에 대해서 설명 드리고자 합니다."

![[Table 1] Cadence, Mentor, Synopsys GPDK 제공 현황](./2019/09/resources/images/sub/03/img_03_01.jpg)

[Table 1] Cadence, Mentor, Synopsys GPDK 제공 현황

칩 설계에서 가장 많이 활용되는 툴을 제공하는 Cadence, Synopsys, Mentor 에서는 설계자들이 학습에 필요한 자료들을 제공하고 있습니다. 간단한 단일 툴의 사용법은 툴에 포함된 예제나 문서를 통해서 진행이 가능하지만 칩 설계 전체 흐름을 경험 하기 위해서는 Design Kit 가 필요로 합니다. 180nm 부터 28nm 공정까지 다양한 Design Kit 를 활용하여 설계 경험을 해보는 것은 전체 공정을 이해하는데 많은 도움이 될 것 입니다.

Design Flow 에 따른 주요 툴 종류

Electronic Design Automation (EDA) 툴은 칩 설계를 위해서 반드시 사용해야 하는 도구 입니다. 칩의 성능은 EDA 툴의 성능과 툴을 사용하는 사용자의 숙련도에 따라 많은 차이를 보이기도 합니다. 반도체 분야의 규모가 커지고 세계적인 관심을 갖게 됨에 따라 EDA 툴 시장에도 많은 회사들이 진출하고 있습니다. IDEC에서도 툴을 매년 소개하려고 노력하고 있으며 좀 더 새롭고 다양한 분야에 적용될 수 있기를 기대하고 있습니다. 많은 EDA Vendor 들 중에서 오랜 기간 동안 독보적인 위치를 지키고 있는 3곳이 있습니다. 바로 Cadence, Synopsys, Mentor 입니다. 대부분의 Design Kit 는 이 3곳에서 지원하는 툴을 중심으로 설계환경이 제공되고 있고 오랜 기간 동안 연구된 성과를 바탕으로 신뢰성 있는 결과를 보여 줍니다.

![[Figure 1] Full Custom Design Flow](./2019/09/resources/images/sub/03/img_03_02.jpg)

[Figure 1] Full Custom Design Flow

3 곳의 Vendor 에서는 설계 과정에서 필요한 기능들을 정립하고 해당 기능을 수행할 수 있는 라인업을 구축하고 있습니다. Full Custom 설계 에서는 Cadence Tool 이 강점을 보이고 있으나, Synopsys 와 Mentor 에서도 새로운 기능이 추가하여 성능과 Runtime을 향상 시킨 제품군을 지속적으로 발표 하고 있습니다. 실제로 Full Custom 설계에서도 Cadence, Synopsys, Mentor 툴을 모두 사용하고 있으며, 공정사에서도 각각의 환경 설정 파일을 모두 제공하는 경우가 늘어나고 있습니다. 기회가 된다면 다양한 툴을 사용해 보시는 것도 좋은 경험이 될 것으로 생각됩니다.

아래는 Cell Based 설계에 주로 사용되는 툴입니다.

![[Table 2] Cell Based EDA Tools](./2019/09/resources/images/sub/03/img_03_03.jpg)

[Table 2] Cell Based EDA Tools

Cell Based 툴들도 많은 개선과 버전업이 되고 있습니다. Mentor 의 Modelsim 은 Questa-sim으로, Cadence Ncverilog(incisive)는 Xcelium으로 브랜드 네임이 변경되면서 다양한 기능이 추가 되었습니다. Auto PnR툴들도 최근 Nitro-SoC, Innovus, ICC2 등 신규 툴들이 지속적으로 발표되고 있으며 단순한 Place and Route 기능에서 RTL 를 포함한 전체 Design Flow 를 연계한 방식으로 변화되는 추세입니다.

Generic Process Design Kit 다운로드 방법

3곳의 Vendor 에서는 각각의 라인업 툴에서 설계가 가능한 Design Kit 환경을 제공하고 있습니다. Vendor 마다 사용되는 포맷이 조금 다른 경우도 있으나 최근에는 공통된 구조를 사용하려고 하고 있으며 대략적인 구성은 비슷합니다.

-

- - Techfile, Display file

- - Pcell Library : Schematic & Layout

- - Model 및 Cell Library

- - Rule Deck : DRC, LVS, Parasitic Extraction

- - Documents : PDK Usage Guide, Design Rule Guide, Model Guide 등

GPDK 를 다운로드 받은 경로는 아래와 같습니다.

![[Figure 2] GPDK 다운로드 경로](./2019/09/resources/images/sub/03/img_03_04.jpg)

[Figure 2] GPDK 다운로드 경로

Synopsys 는 Solvnet 계정 정보가 필요 합니다. 각 대학별로 2개의 계정 정보를 전달 드리고 있으므로 해당 정보를 통해 접속 후 다운로드가 가능합니다. (Solvnet 이 아닌 Synopsys 홈페이지를 통해서 접근해야 합니다.) Cadence는 Support페이지에서 확인할 수 있으며 접속 권한은 EDA 툴 신청 시 Cadence 교육용 프로그램 신청을 하신 분들에게 계정 정보를 알려 드리고 있습니다. 또는 IDEC Tool FTP 서버에서 다운로드 받아 보실 수 있습니다. Mentor는 대학에 별도로 계정 정보가 제공되지 않으므로, 필요하신 경우 IDEC에 문의 하시면 처리에 드리도록 하겠습니다.

※ 접속 권한과 관련된 내용은 본 메일로 연락 주세요. (eunjuseok@idec.or.kr)

GPDK주요 특징

· Cell Based 설계팀을 위한 Synopsys Generic Design Kit

![[Figure 3] synopsys 32-28nm Digital Library](./2019/09/resources/images/sub/03/img_03_05.jpg)

[Figure 3] synopsys 32-28nm Digital Library

Synopsys는 Cell Based Flow에 보다 강점을 가진 툴들을 많이 보유 하고 있습니다. 공정에서 제공되는 Design Kit를 보더라도 Standard Cell 등의 Setup과 Scripts는 Synopsys를 중심으로 되어 있는 경우가 많이 있습니다. 이러한 성향을 반영하듯 Synopsys에서 제공하는 GPDK 는 Cell Based 환경에서 설계하는 디지털 설계자들에게 유용한 다양한 환경을 제공합니다. 또한 Clock Gating, Power Gating, Multi Voltage, Multi Vth 등 다양한 Example을 제공하여 Design Kit 를 활용한 다양한 설계 방법을 구현해 볼 수 있습니다.

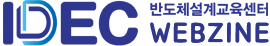

· PLL

최근 제작되는 칩은 고사양의 스펙을 요구하기 때문에 내부에 PLL 을 두고 설계를 진행하는 경우가 많습니다. PLL 없이 진행된다면 300Mhz 정도로 스펙을 낮춰 설계를 진행해야 하기 때문에 전체 시스템을 구성하고 점검하는데 적합하지 않은 경우가 있습니다. Synopsys 32-28nm Design Kit 에는 1Ghz 의 Output Freqency PLL 을 제공합니다. 매크로 형태로 사용이 가능하며 GDS Layout 파일이 포함되어 있어 Physical Verification 을 진행해 볼 수 있습니다.

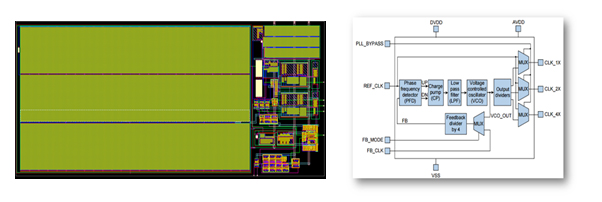

· Memory Compiler

-

- 디지털 설계를 진행하는 과정에서 많이 사용되는 블럭은 메모리입니다. 시스템을 구성하는데 많은 면적과 파워를 소모하게 되므로 공정사에서 제공되는 메모리를 사용하는 것은 칩 전체의 효율성을 높이는데 많은 도움이 됩니다. Synopsys Design Kit 에는 미리 생성해 놓은 35개의 SRAM 이 포함되 있으며 이와는 별개로 사용자가 원하는 메모리를 직접 생성하여 사용할 수 있도록 메모리 컴파일러를 제공합니다. 메모리 컴파일러를 사용하기 위해서는 기본적으로 아래와 같은 작업 환경이 준비되어 있어야 합니다.

-

Environment

- - GNU/Linux operating system (tested on Centos 7 64-bit)

- - Perl 5.8.8 or above

- - Bash

-

Synopsys EDA tools used for test

- - Custom Designer, version J-2014.12-SP2 or above

- - Design Compiler, version J-2014.09-SP3 or above

- - IC Validator, version J-2014.12

- - StarRC, version J-2014.12 or above

- - Library Compiler J-2014.12 or above

-

메모리 컴파일러는 Verilog Model(.v) 뿐만 아니라 Logic Library (.lib, .db), LEF 와 함께 GDS Layout 파일을 같이 제공하므로 최종 검증 과정에서 전체 디자인과 함께 검증이 가능합니다. 다만 생성할 수 있는 메모리의 크기가 한정적이라는 점이 다소 아쉽습니다.

- · memtype = single32 | dual32 | singlelp32 | duallp32 | dual90 | single_90

- · word_count = 16 | 32 | 64 | 128

- · words_bits = 4 ~ 512

· Example Design & Scripts

Low Power 설계를 위해 라이브러리와 함께 사용되는 몇 가지 기법들이 있습니다. 대표적인 방법이 Multi Voltage와 Multi Vth Cell 을 혼합하여 사용하는 방법으로 최근에는 180nm 공정에서도 관련 Cell 들을 제공하는 경우가 많습니다. 동작의 속도가 중요한 모듈은 High Voltage, High Vth를 사용하고 속도 보다는 전력 소모가 중요한 모듈에서는 Low Voltage, Low Vth Cell 을 혼합 사용하여 전체적인 전력 소모를 줄일 수 있습니다. 이러한 설계 기법은 관련 Cell 들을 공정사에서 제공해줘야 구현이 가능한 방법으로 고려해야 할 사항이 많고 검증 과정 역시 Single Voltage 에서 진행하는 것 보다 다소 복잡합니다. 최근 IoT 등 저전력 설계가 많은 이슈가 되면서 Low Power Cell을 별도로 제공하는 공정이 늘어 나는 추세 이므로 관련 된 설계 방식을 습득할 수 있다면 Fab 진행 시 많은 도움이 될 것 입니다. Synopsys GPDK 안에는 관련된 예제 Scripts 와 라이브러리를 포함하고 있어 Low Power 설계자들에게 좋은 자료가 됩니다. 다만 포함되어 있는 Example 은 그대로 사용하기에는 몇몇 부족한 데이터가 있습니다. 관련해서는 추후에 IDEC 블로그 또는 홈페이지에 별도로 설명을 추가 하도록 하겠습니다.

Clock Gating, Multi Voltage, Multi Vth, Power Gating, Flip Chip, Wire bond

Full Custom 설계팀을 위한 Cadence Generic Design Kit

· Finfet & Virtuoso (IC51 & IC61)

Cadence GPDK 는 45nm, 90nm, 180nm 공정에 대한 자료를 제공하고 있으며 RF 와 관련된 내용을 포함하고 있습니다. 또한 추가적으로 Finfet 에 대한 Design Kit 로 제공하니 관심 있는 분들은 참고해도 좋을 듯 합니다.

ADVGPDK (Version 0.5) - Advanced Node 0.8V / 1.8V Finfet / Multi Patterned 8 Metal Generic PDK

최근까지 Full Custom 설계를 위해 가장 많이 사용되고 있는 툴은 Cadence Virtuoso 입니다. Cell Based 설계 방식과는 다르게 설계자가 직접 모든 레이아웃을 진행해야 하므로 설계에 대한 경험 정도에 따라 칩의 성능 및 면적 등에 차이가 발생하기도 합니다. Cadence Design Kit 에는 Full Custom 디자인에서 기본적으로 사용되는 환경 들이 잘 갖춰져 있으며 전체적인 설계 흐름을 이해하는데 부족함이 없습니다. Virtuoso 툴은 대부분의 공정에서 라이브러리를 지원하고 있으므로 후추 공정 진행에서 쉽게 적응하여 설계를 진행할 수 있다는 장점이 있습니다. 설계 과정에서 사용이 필요한 툴은 대부분 IDEC 라이센스로 사용이 가능하므로 Full Custom 으로 설계를 진행하고자 하는 경우에는 Cadence Generic Design Kit는 좋은 학습 자료가 될 것 입니다.

![[Figure 5] Cadence 45nm GPDKs : 2 Poly 11 Metal](./2019/09/resources/images/sub/03/img_03_08.jpg)

[Figure 5] Cadence 45nm GPDKs : 2 Poly 11 Metal

Verification 의 장점을 살린 Mentor Design Kit

· Calibre & Pyxis

Mentor 에서 제공되는 Calibre 는 대부분의 공정에서 Sign Off 툴로 지정되어 있습니다. Calibre 는 검증에 특화 되어 있는 툴로 공정사와 Cross check 과정에서 상호간의 Miss Match 를 줄여 안정된 데이터를 전달 할 수 있도록 합니다. 또한 Design Rule Check (DRC) 정확하게 진행하고 Runtime 속도를 향상 시켜 검증을 위한 시간을 절약 할 수 있도록 도와 줍니다. Calibre 툴의 장점 중의 하나는 다른 회사 툴들과 연동성이 좋다는 점에 있습니다. Cadence Virtuoso 또는 Synopsys Custom Designer 에서 Invoke 를 할 수 있으며, Layout View 에서 문제가 되는 지점을 쉽고 정확하게 확인할 수 있도록 안내합니다.

![[Figure 6] Mentor 130nm Pyxis & Calibre](./2019/09/resources/images/sub/03/img_03_09.jpg)

[Figure 6] Mentor 130nm Pyxis & Calibre

· GPDK 의 장점과 단점

Vendor 사에서 제공되는 Design Kit 는 몇 가지 장단점이 있습니다. 첫 번째 장점은 무료로 다운로드 받아 사용할 수 있다는 점입니다. 각 회사의 Support 페이지를 통해서 쉽게 접근이 가능하며 별도의 비용 지불없이 무료로 다운로드 받아 설계에 대한 경험을 할 수 있습니다. 둘째는 Sign Off 로 사용되는 툴을 익히는데 많은 도움이 됩니다. 다양한 라이브러리와 함께 가이드문서를 같이 제공하여 실재 공정 사용과 상당히 비슷한 설계 환경을 제공합니다. 이는 공정 진행 시 빠르게 적응할 수 있도록 도와줍니다. 세번째로 다양한 툴을 연계하여 사용할 수 있는 경험을 제공합니다. 예를 들어 Cell Based 디자인은 Synopsys 툴을 주로 이용하고 Full Custom 은 Cadence 툴을 사용하고 있으나 Vendor 에서 제공되는 Design Kit 를 통해 Synopsys 툴을 이용한 Full Custom 설계, 또는 Cadence 툴을 이용한 Cell Based 설계를 경험할 수 있게 해줍니다.

물론 단점도 있습니다. 첫번째로 각각의 Vendor 는 각 회사의 툴을 사용한 설계 Flow 를 권장하므로 사용환경이나 자료가 한쪽으로 편중되는 경향을 보입니다. 예를 들어 Cadence Generic Design Kit 의 경우 Full Custom 사용자들에게는 유용하지만 Cell based 설계자들에게는 친절한 설명이 부족합니다. 또한 메모리 컴파일러를 제공하지 않으며 Cell 에 대한 세부 정보 및 툴 셋업에 대한 가이드가 충분하지 않습니다. 두 번째로 유지관리가 완벽하게 되고 있지 않습니다. 대부분 공정사에서 제공되는 Design Kit 는 2013년도 전후에 제작된 것으로 벌써 약 6년의 시간이 흘렀습니다만, 새로운 Design Kit 가 추가로 제공되지 않으며 예제 등 몇몇 사용 환경에서 문제되는 부분들이 업데이트가 완벽하게 이루어 지고 있지는 않습니다. 물론 교육용으로 사용하기에는 전혀 문제가 없으므로 많은 분들이 활용하시면 좋을 듯합니다.

이상으로 Vendor에서 제공되는 Generic Design Kit의 종류와 특징들에 대해서 알아보았습니다. Vendor 별로 제공되는 환경과 주요 기능에 조금씩 차이가 있으므로 설계 환경에 보다 적합한 Design Kit 를 다운로드 받아 활용해 보시면 좋을 것 같습니다.

-

김 연 태 IDEC 선임연구원

김 연 태 IDEC 선임연구원-

담당분야

- MPW 공정 기술 지원 매그나칩/SK하이닉스 180nm 공정

- EDA Tool 기술지원 (Digital back-end)

- ASIC 설계실 지원 (digital) - E-mail ytkim@idec.or.kr

-

담당분야

-

조 인 신 IDEC 책임연구원

조 인 신 IDEC 책임연구원-

담당분야

- MPW 공정 기술 지원 매그나칩/SK하이닉스 350nm 공정

- MPW 공정 기술 지원 삼성 65nm, 매그나칩/SK하이닉스 180nm 공정 Analog 부문

- EDA Tool 기술지원 (Analog) - E-mail ischo@idec.or.kr

-

담당분야