| IP개요 |

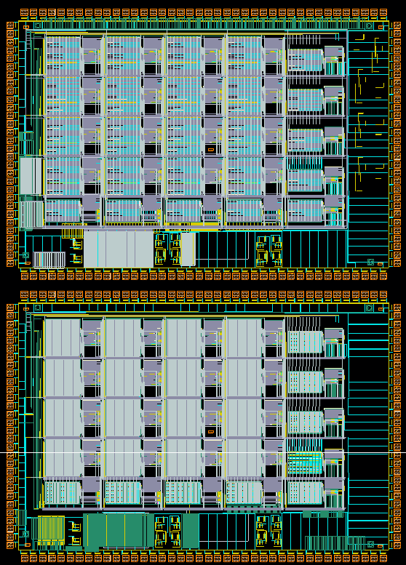

FPGAs are in the spotlight as an advantage in that they can process machine learning algorithms with faster computation speed and lower power consumption than CPU/GPU, and can rapidly apply evolving AI algorithms. However, there are limitations in terms of power consumption and degree of integration due to the high leakage current and large area of SRAM used in FPGAs. In order to overcome the limitations, FPGAs in the form of CMOS logic and monolithic three-dimensional integrated NEMS memory have been proposed, and simulation results have shown that computation speed, degree of integration, and power consumption are improved compared to FPGAs made of CMOS only. However, it has not been implemented yet, and there are limitations to existing research that implements a monolithic three-dimensional integrated architecture in which NEMS memory and CMOS logic are integrated. In this dissertation, we develop a reliable fabrication method for NEMS memory integrated in BEOL. We implement a monolithic 3D integrated architecture of NEMS memory and CMOS logic, and confirm the feasibility of implementing NEMS memory-based FPGAs. |