| IP명 | Implementation of eDRAM for Process-in-Memory | ||

|---|---|---|---|

| Category | Mixed | Application | eDRAM |

| 실설계면적 | 2㎛ X 2㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 400MHz |

| 검증단계 | Silicon | 참여공정 | HM-2201 |

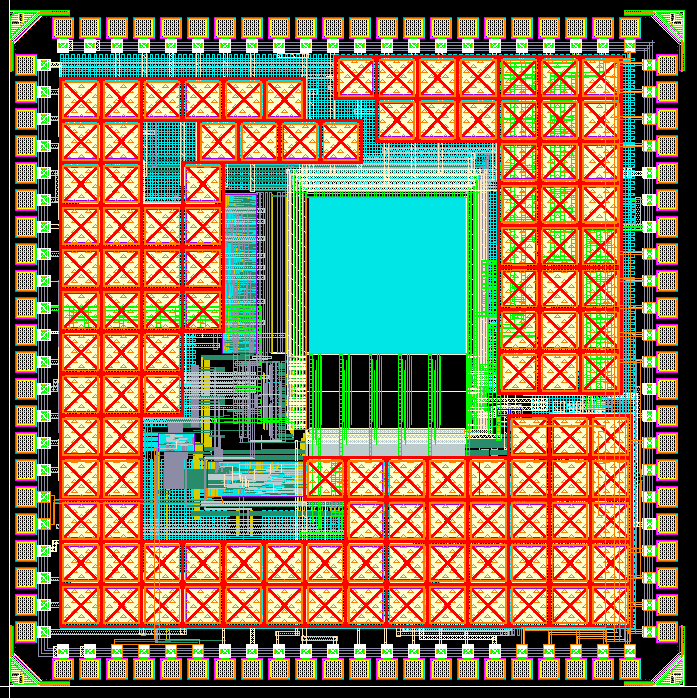

| IP개요 | 본 IP는 Process-in-Memory를 위한 eDRAM 회로로 data의 read와 write 동작에 필요한 Memory Mat, Sense Amplifier, Decoder, Output driver, Digital Commander block 을 포함하고 있습니다. 중앙에 보이는 1T1C 구조의 Memory Mat 에서 사용된 Capacitor는 MOM Capacitor로 interdigitated 구조에 외부 노드에 DC 를 인가할 수 있게 하여 인접한 cell에 의해 해당 memory cell의 storage node voltage가 변하는 것을 최소화하고자 했습니다. Memory Mat 사이에 위치하는 Sense Amplifier는 Charge sharing 된 data를 latch 동작을 통해 0 또는 1로 판단하여 Memory cell을 refresh 하거나 저장된 데이터를 증폭하여 외부로 전달하는 역할을 합니다. Column decoder와 Row decoder는 Commander나 SPI에서 들어오는 주소 값과 일치하는 word line 또는 bitline을 activation 해서 Pre-deteremine된 data가 메모리에 저장할 수 있게 하거나 저장된 data를 output driver에 전달하는 역할을 합니다. Level shifter는 Row Decoder에서 나오는 word line activation 신호가 Memory cell의 TR을 안정적으로 driving 하도록 activation 신호를 1V 에서 1.8V로 승압하는 역할을 합니다. 하단의 Digital commander block 은 SPI에서 나오는 bitstream에 따라 크게 두 가지 동작을 합니다. 첫번째로 Memory Mat 의 순차적인 주소값에 해당하는 memory cell에 데이터를 쓰고 동일한 과정으로 저장한 데이터를 읽는 동작, 두번째는 Memory Mat에 랜덤한 주소값에 해당하는 memory cell에 랜덤한 데이터를 쓰고 읽는 동작 입니다. Memory Mat에 저장된 데이터는 output driver와 PAD를 거쳐 칩 외부에서 DSA와 같은 장비를 통해 직접 확인할 수도 있고 write 한 데이터와 memory cell에서 read한 데이터가 동일한지 확인하는 Pattern checking block을 통해서도 데이터 저장의 여부를 확인할 수 있습니다. 위와 같은 block들을 통해서 PIM 과정에서 생성되는 데이터가 메모리에 제대로 write 또는 read 되는지 확인할 것 입니다. |

||

- 레이아웃 사진 -

|

|||