| IP개요 |

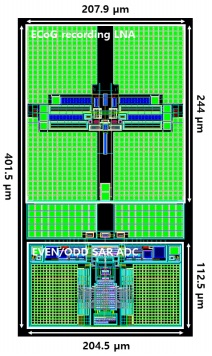

an implantable analog front-end integrated circuit for ECoG recording incorporating LNA and SAR ADC is presented. The LNA designed based on inverter stacking technique achieves excellent NEF performance by using proposed floating body technique. By using the gain boosting topology, CMFB compensation technique, and T-resistor network in capacitive feedback, more accurate frequency response is achieved and enables high-fidelity ECoG recording. The LNA operating at 1-V supply achieves 1.27 of NEF with 40 dB of voltage gain, 520 Hz bandwidth, 6.04 μVrms of integrated input referred noise and 15.5 nW power consumption. The designed SAR ADC uses a VCM-based monotonic capacitor switching scheme saving 97.66 % of switching power with quarter of CDAC area compared to conventional SAR ADC. Proposed EVEN/ODD technique using new dynamic logic block architecture reduces the number of digital logic blocks, digital power consumption, and logic delay. Asynchronous clock and non-binary weight redundant capacitor techniques are used to improve the ADC power efficiency and linearity. The ECoG recording AFE IC designed using TSMC 1P9M 65-nm CMOS process occupies 0.083 mm² of chip area. |