| IP명 | A Two-Step, Cyclic Vernier-Based Time-to-Digital Converter Using Dynamic Element Matching | ||

|---|---|---|---|

| Category | Mixed | Application | Time to Flight |

| 실설계면적 | 2㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 900MHz |

| 검증단계 | Silicon | 참여공정 | SS28-2102 |

| IP개요 | We describe a two-step dynamic element matching (DEM) cyclic time-to-digital converter (TDC) based on the Vernier gated ring oscillator (GRO). The DEM is achieved by storing GRO's state in the previous conversion to be used as the beginning state of the next conversion. The signal propagation path in the two Vernier GRO is changed between two consecutive conversions and depends on the amount of time input. Therefore, the systematic error is randomized and achieving DEM. | ||

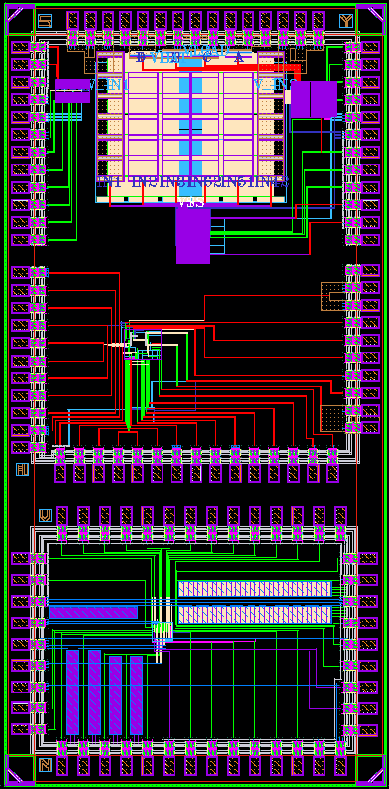

- 레이아웃 사진 -

|

|||