| IP명 | A Low-Jitter 28−31GHz Frequency Synthesizer Based on Digital Sub-Sampling PLL Using Optimally-Spaced Voltage Comparators and Background Loop-Gain Optimization | ||

|---|---|---|---|

| Category | Analog | Application | Wireless/Wireline communication |

| 실설계면적 | 1㎛ X 3.5㎛ | 공급 전압 | 1.2V |

| IP유형 | 동작속도 | 30000000000Hz | |

| 검증단계 | Silicon | 참여공정 | HM-2201 |

| IP개요 | 고속 통신에 대한 수요가 커지면서, low noise clock generator 가 많이 사용되고 있음. 특히 5G 통신의 경우 30GHz 대역의 반송 주파수(carrier frequency)가 필요함. 하지만, 해당 주파수에서 low noise clock을 만드는 것은 어려움. 따라서, 본 Tapeout에서는 PLL와 ILFM의 cascade 구조를 활용하여 최종 아웃풋 신호의 지터를 최소화할 수 있도록 디자인되었음. 특히, 첫 단의 PLL로 SSPLL을 사용하여 더욱 낮은 지터를 달성하였음. | ||

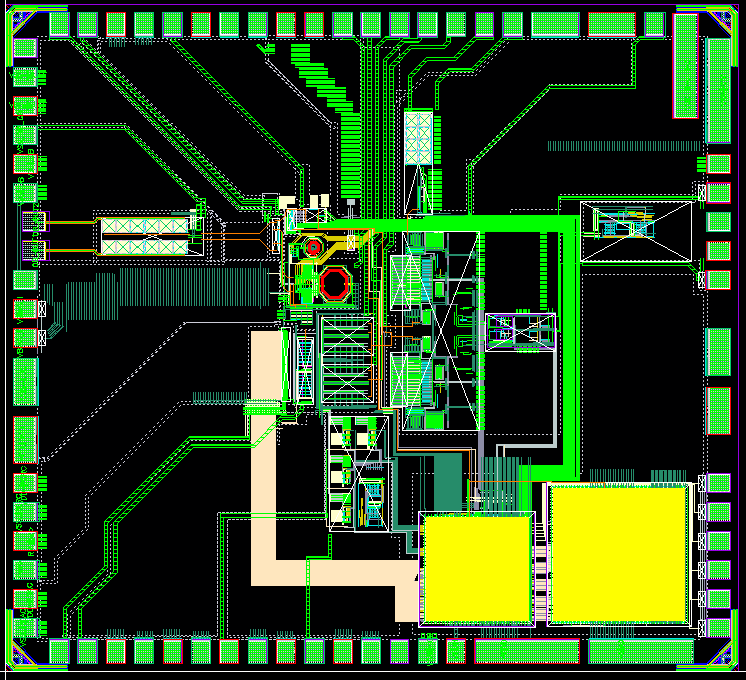

- 레이아웃 사진 -

|

|||