| IP명 | Design of Blocker-Tolerant RF CMOS Receiver Front-End for Next-Generation 5G NR Applications | ||

|---|---|---|---|

| Category | Analog | Application | 4G LTE cellular 및 WiFi |

| 실설계면적 | 2㎛ X 2㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 0.7G-2.7GHz |

| 검증단계 | Silicon | 참여공정 | HM-2102 |

| IP개요 | 이득이나 위상의 별도의 보정 (Calibration) 필요 없는 N-path 필터 기반의 blocker-rejection receiver front-end 구조를 보여준다. 설계된 주경로는 신호와 대역 외 블럭커를 모두 통과 시키는 반면, 보조 경로는 대역 외 블럭커만 통과시킨다. 설계 블럭의 마지막 단에서 두 경로 신호를 반전하여 합함으로써 블럭커만 제거되고 신호가 출력되는 구조를 보여준다. 기존 N-path 기반 블럭커 제거 구조에서는 블럭커 제거의 극대화를 위해 별도의 이득 및 위상 보정을 진행하지만, 제안한 구조에서는 주경로와 보조경로의 위상,이득 변화를 동일하게 유지함으로써 보정없이 블럭커 제거 특성을 구현한 점에서 차별성이 존재한다. | ||

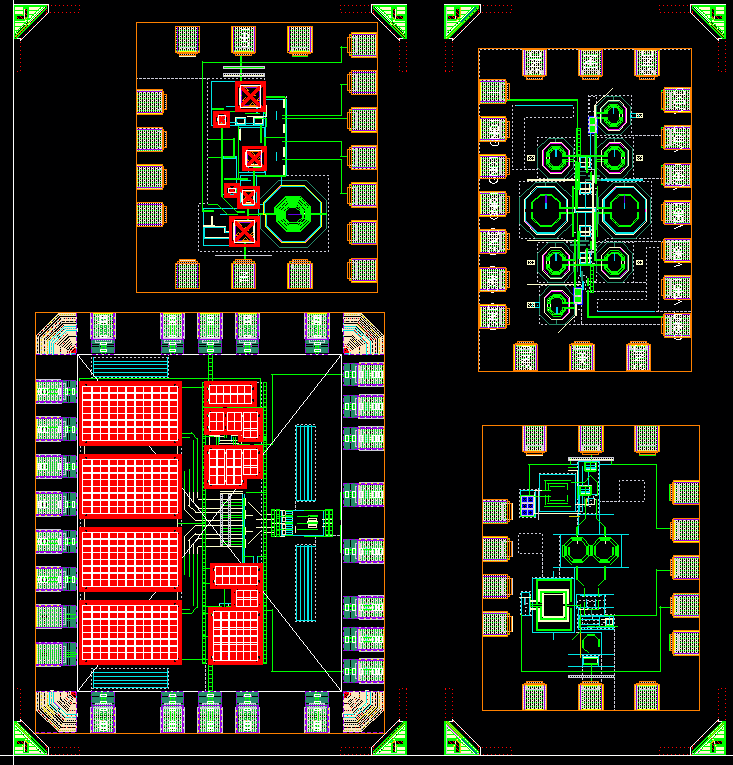

- 레이아웃 사진 -

|

|||