| IP개요 |

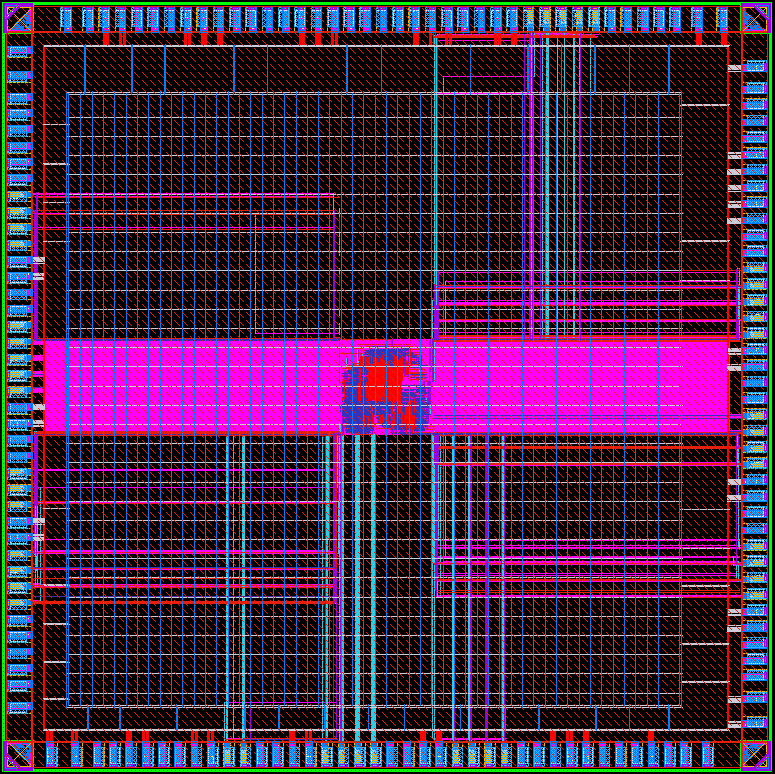

This project newly proposes an ultra-low-latency ordered statistic decoding (OSD) architecture. To reduce the decoding latency of OSD, our architecture optimizes the Gaussian elimination and several condition computation with low resolution fixed-point arithmetic operation. Also, we uses the conventional BCH decoding architecture for early termination of the decoding. As a result, the proposed architecture is fabricated in 28nm CMOS process and this architecture can be realization of the OSD algorithm for B5G/6G URLLC IIOT networks |