| IP명 | Power handling capability enhancement design technique of antenna tuning switch in all-off condition by 28nm RF CMOS technology | ||

|---|---|---|---|

| Category | Analog | Application | 통신 analog |

| 실설계면적 | 4㎛ X 2㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | sub-6GHz |

| 검증단계 | Silicon | 참여공정 | SS28-2102 |

| IP개요 | This research presents strategy of increasing the power handling level of switch under the all-path off condition. The proposed switch is fabricated using a 28nm CMOS RF technology. RF protection technique will be applied to switch with the techniques of a multi-stacked FET, a floating gate/body and a negative biasing. The RF protection is proposed as a simple structure using a capacitor and a stacked-FET. Under the all-path off condition, the proposed switch achieved 37.7 dBm power handling level as high as 5.7 dB compared to the power handling level of conventional switch at 2 GHz based on the previous work. And the switch insertion loss and isolation are achieved 0.31 dB and 42.72 dB at 2 GHz. |

||

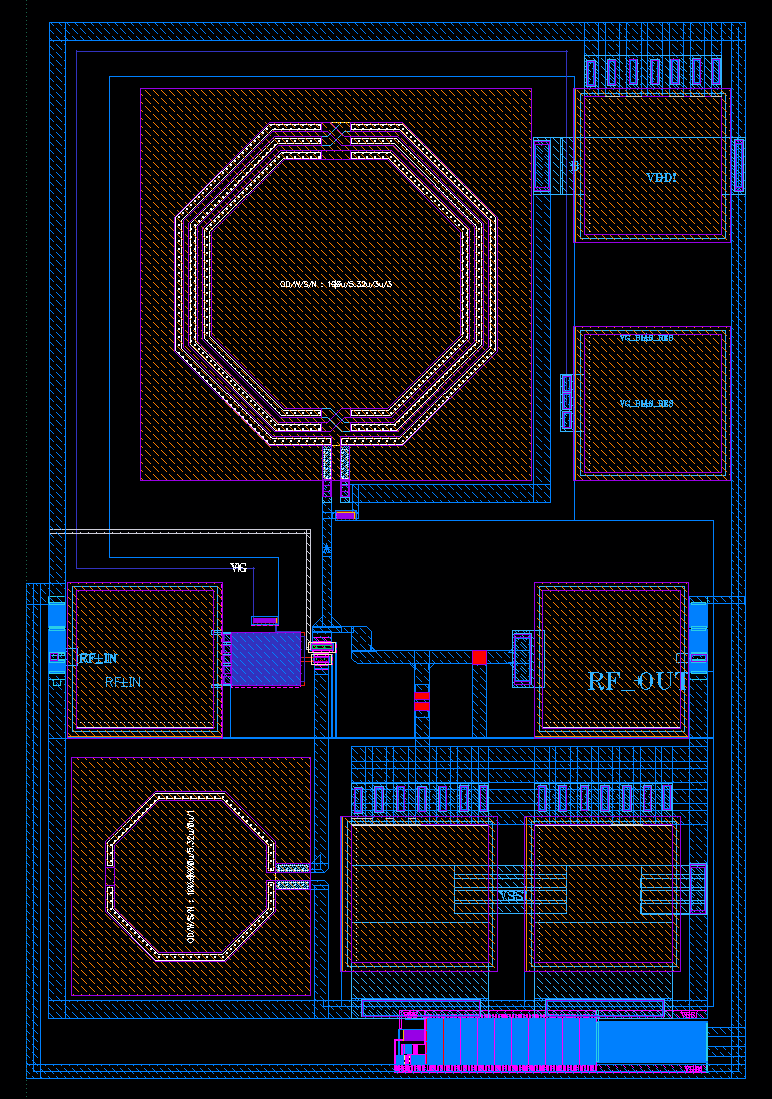

- 레이아웃 사진 -

|

|||