한국과학기술원 바이오및뇌공학과 박사과정 석동열

#### **Session 26 Advanced Biopotential Interfaces**

이번 2025 IEEE CICC의 Session 26, Advanced Biopotential Interfaces에서는 총 7편의 논문이 선정되어 발표되었다. 이 세션에서는 바이오포텐셜(Biopotential)를 수집하는 계측 (instrumentation 또는 recording) 회로와 유발하기 위한 자극기(stimulator)를 주로 다룬다. 전력 효율 증대, 입력 범위 증대, 공통모드 제거 성능향상, 노이즈 감소 등 계측회로 및 자극기가 갖추어야 할 기본적인 성능 지표를 개선하기 위한 연구 논문과 바이오포텐셜 인터페이스의 활용 범위를 넓히고자 하는 응용 연구에 관한 리뷰가 소개되었다.

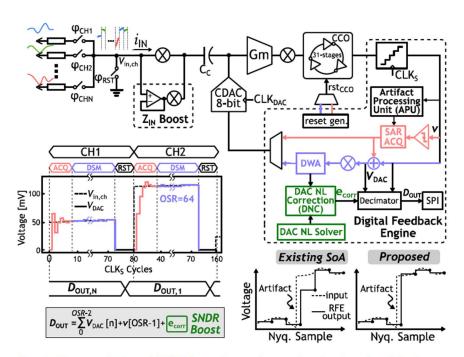

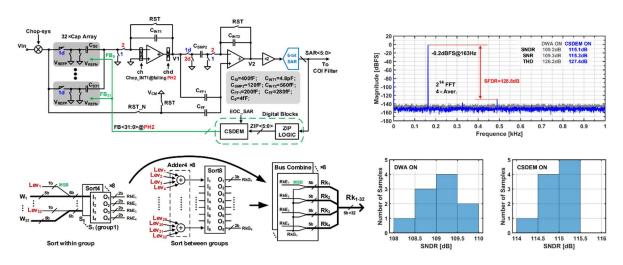

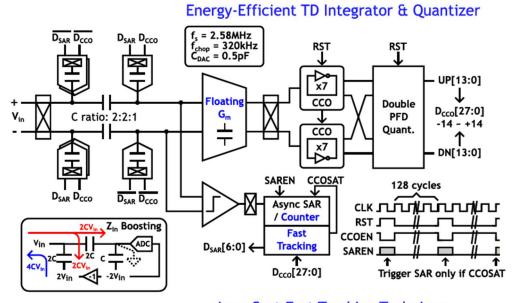

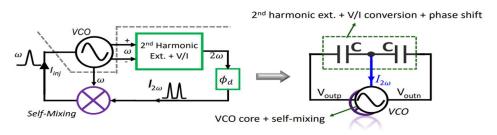

#26-2 본 논문은 조지아텍(Georgia Tech) 및 에머리대학(Emory University)의 연구진이 발표한 논문으로, 32채널의 뉴럴 레코딩을 위한 고해상도 시간-다중화 방식(time-division multiplexing) 방식의 아날로그 프론트엔드(AFE)를 제안한다. 제안된 회로는 85.4dB의 SNDR 성능을 갖추었으며, 자극 아티팩트(stimulation artifact) 발생 시에도 변환 손실 없이 신경 신호를 지속적으로 획득할 수 있는 변환 중 아티팩트 복구(within-conversion artifact recovery) 기능을 탑재한 것이 특징이다. 일반적으로 고밀도 뉴럴 인터페이스 시스템은 전극 수를 늘리는 과정에서 회로 면적과 전력 소모가 급증하게 된다. 이를 해결하기 위한 시간-다중화 기반 구조는 여러 채널을 하나의 변환기와 공유함으로써 효율적인 집적이 가능하지만, 자극 아티팩트(stimulation artifact)로 인한 신호 왜곡이나 샘플 손실 문제가 존재해왔다. 특히 전기 자극이 잦은 폐루프 자극 시스템에서는 이 문제로 인해 실시간 신호 획득이 어렵다.

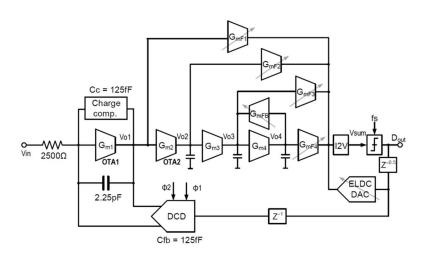

본 연구에서는 이를 극복하기 위해, IDSM(incremental delta-sigma modulation) 기반의 변환 구조를 사용하면서, 변환 주기 내 아티팩트를 실시간 감지하고 무효화된 반쪽 샘플링구간을 자동으로 회피하여 반대쪽 구간으로 전환하는 회복(recovery) 구조를 회로 내에 통합하였다. 이 구조는 8.8μs 이내의 짧은 지연 시간으로 아티팩트를 검출하고 처리할수 있으며, 이를 통해 변환 누락 없이 연속적인 신호 획득이 가능해졌다. 또한, coarse SAR + fine DSM의 듀얼 루프를 활용한 incremental zoom ADC 구조를 사용하여 전력과면적 효율을 동시에 확보하였다. 특히, DAC의 비선형성으로 인한 SNDR 감소를 보완하기위해 데이터 가중 평균(DWA) 기반의 디지털 보정 기법을 4+4bit 세그먼트 DAC에 적용

하였고, 이를 통해 DAC 비선형 누적 오차에 대한 보정을 실시간으로 수행하였다.

회로의 전류 입력단은 차퍼-인버터(chopped inverter) 기반의 Gm-CCO 구조를 사용하여 플리커 잡음(flicker noise)를 억제하고, 100MΩ 이상의 입력 임피던스를 확보하였으며, Gm-CCO의 오프셋 보정 및 디지털 데시메이션(decimation) 필터도 온칩으로 구현되었다. 결과적으로, 제안된 회로는 아티팩트가 수시로 발생하는 폐루프 환경에서도 높은 SNDR과 연속적 신호 획득 성능을 보장하면서, 프로세스 스케일링에 유리한 디지털 친화적 구조를 유지한다. 본 회로는 대규모 전극 어레이 시스템에 적합하며, 고밀도 신경 레코더시스템의 전력 및 신호 충실도 문제를 동시에 해결하는 방향으로 설계되었다. 구체적인 측정 결과로는 85.4dB SNDR, sub-9μs 회복지연, 채널 당 0.92μW 전력 소모, 그리고 고전압 아티팩트 존재 하에서도 지속적인 신호 획득 성공 사례를 제시하였다. 본 회로는 65nm CMOS 공정으로 구현되었으며, 0.055mm²의 면적 위에 구현되었다.

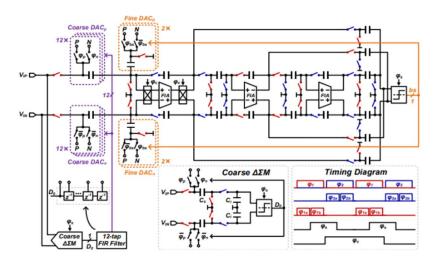

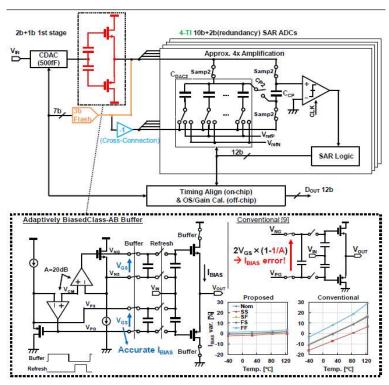

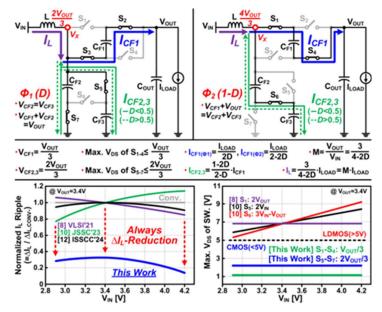

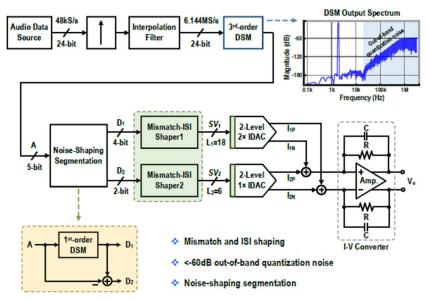

Fig. 1. Time-multiplexed IDSM-based neural recording front-end architecture (top), achieving rapid artifact recovery (bottom-right) and boosted output SNDR (bottom-left).

[그림 1] Mandal 등은 32채널 TDM 기반의 뉴럴 레코딩 프론트엔드에서 변환 중 아티팩트 복구가 가능한 구조를 제안하였다. 제안된 아키텍처는 SAR 기반 추정 과정과 DSM 기반 세부적인 값 추적 과정을 통합하여 높은 SNDR을 확보하면서도, 자극에 의해 발생한 아티팩트를 변환 주기 내에서 검출하고 회피할 수 있도록 한다. 이를 통해 자극 중에도 오랜 복구 지연 없이 신경 신호획득이 가능하며, 고집적 및 저전력 아키텍처를 동시에 달성할 수 있다.

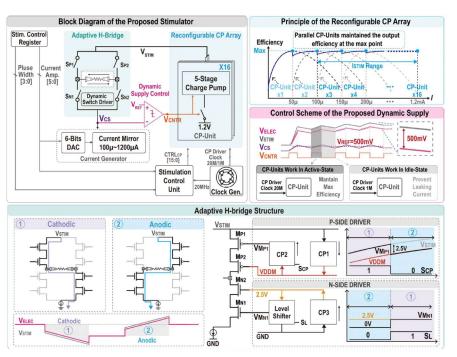

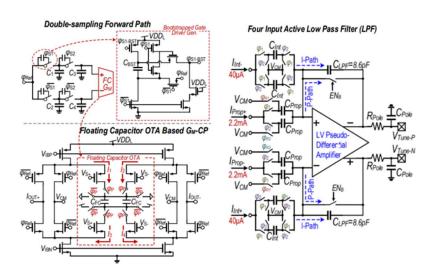

#26-3 본 논문은 중국 동제대(Tongji University)의 연구진이 발표한 논문으로, 전류 제어

방식(current-controlled)의 무선 신경 자극기를 8mm³ 패키지 내에 완전 통합하여 구현하고, 71.7%의 피크 효율 및 전류 범위 전체에서 13.5% 이내의 효율 변동률을 달성한 고효율 구조를 제안하였다. 기존의 무선 이식형 신경 자극기(W-IPNS)들은 이식성은 우수하지만, 넓은 전류 범위에서 전압 조절이 어려워서 출력 손실(power loss)이 크고, 이에 따른조직 과열(tissue heating) 문제가 제기되어 왔다. 특히 전류 제어형 자극기(current-controlled stimulator, CCS) 구조는 자극 정밀도 측면에서 유리하지만, 다양한 전류 수준에 적절히 대응하지 못해 비효율적이었다.

연구진은 이를 해결하기 위해 다중 전하펌프(charge pump, CP) 어레이 기반의 동적 전압 조절 시스템(Dynamic Voltage Scaling)을 설계하였다. 자극 전류의 크기에 따라 CP 유닛이 자동으로 선택되어 공급 전압을 조절하고, 전류원 전압이 기준치보다 높아질 경우 CP 동작을 중단하는 폐루프 제어 구조를 통해 과도한 전압 공급을 방지하였다. 또한, 자극 펄스는 양극성(biphasic) 이중위상으로 구성되며, 100kbps 속도의 초음파 통신을 통해 16 비트 명령어 기반으로 유연하게 설정할 수 있도록 하였다. 회로는 65nm CMOS 공정으로 제작되었으며, 0.44mm² 면적에 구현되었다. 최대 6V 자극 전압, 100µA ~ 1.2mA 자극 전류 범위, 45단계 전류 설정을 지원한다. 회로 전체는 단일 칩 내에 완전 집적되어 8mm³ 크기의 패키지로 구현되었다. 측정 결과, 자극 전류 범위 전반에 걸쳐 최대 71.7% 효율, 13.5% 이내의 효율 변동률, 우수한 전력-면적 균형, 낮은 발열 특성을 확인하였으며, 심부 자극 등 다양한 신경 자극 응용에서의 확장성을 보여주었다.

Fig. 3. Block diagram, circuit implementation, and working principle of the proposed reconfigurable charge-pump-based near-adiabatic stimulator.

[그림 2] 제안된 전류 제어형 신경 자극기의 아키텍처 및 동적 공급 전압 조절 구조. 시스템은 재구성 가능한 charge pump(CP) 어레이와 폐루프 전압 제어 회로를 통합하여, 요구 자극 전류 (ISTIM)에 따라 자극 전압(VSTIM)을 실시간으로 조절한다. 16개의 CP 유닛은 전류원 전압을 감지하여 선택적으로 활성화되며, 이를 통해 전력 손실을 최소화하고 에너지 효율을 극대화한다. 양극성 자극은 초음파 기반 무선 통신으로 수신된 16비트 명령어에 따라 제어된다.

### 저자정보

#### 석동열 박사과정 대학원생

● 소속 : 한국과학기술원

● 연구분야 : 바이오메디컬 응용 회로설계(센서 및 신호처리)

• 이메일 : sukd10@kaist.ac.kr

DGIST 전기전자컴퓨터공학과 박사과정 위정윤

# Session 36 Communication Computing and Sensing Techniques in Biomedical Systems

2025 IEEE CICC의 Session 36에서는 웨어러블 및 이식형 바이오 시스템을 위한 생체 신호 측정, 온칩 신호 처리, 무선 통신 기술을 다룬다. 초저잡음 센서, 공통모드 간섭 억제, RR 간격 분석 등 정밀 측정을 위한 회로 기술이 소개되었다. 전체적으로 의료용 저전력 통합 회로 설계의 실용성과 확장 가능성을 보여준 세션이다.

## **#36-1 RPG-HBC: Reconfigurable Passive Galvanic Human Body Communication for Bioelectronic Implants under Varying Channel Conditions**

본 논문에서는 시간에 따라 변하는 인체 내 채널 환경에서도 안정적인 무선 통신을 구현 하기 위해, 재구성 가능한 수동형 갈바닉 인체 통신 구조인 RPG-HBC를 제안했다. 생체 삽입형 디바이스는 조직 전도도나 전극 접촉 품질이 달라짐에 따라 채널 임피던스가 변 동되므로, 안정적인 통신을 유지하기 어렵다. 이러한 문제를 해결하기 위해 본 논문은 기 본 모드, 인덕티브 로드 모드, 인덕티브 그라운드 모드의 reconfigurable 한 세 가지 동작 모드를 제안했다. 기본 모드는 조직의 전도도가 높고 채널이 주로 저항 성분일 때 적합 하며, 단순한 회로 구성으로 에너지 효율이 높다. 인덕티브 로드 모드는 조직의 전도도가 낮고 커패시턴스 성분이 지배적인 경우에 효과적이며, 인덕터를 직렬로 삽입하여 반사 임피던스를 증가시키고 수신 신호를 증폭한다. 인덕티브 그라운드 모드는 전극 접촉이 불안정하거나 외부 압력이 약해지는 상황에서 유리하며, 인덕터를 저임피던스 경로로 활 용해 반사 손실을 줄이고 신호 세기를 센싱한다. 제안된 구조는 반사된 신호를 직류로 변환하는 6단계 정류기, 아날로그 신호를 디지털로 변환하는 VCO 기반 변환기, 커패시터 뱅크를 제어하는 적응형 제어기, 그리고 세 가지 모드 전환을 위한 스위치들로 구성되어 있다. 커패시터 뱅크의 등가 커패시터는 외부 인덕터와 함께 인덕턴스를 조절하는 역할 을 하며, 제어기는 coarse-to-fine 탐색 방식을 통해 수신 신호의 세기를 기준으로 최적 의 설정을 찾아낸다. 이러한 이중 단계의 탐색 방식은 복잡한 보정 회로 없이도 실시간 으로 환경 변화에 적응할 수 있게 하며, 회로의 전력 소모를 최소화하면서도 안정적인 통신 성능을 유지할 수 있도록 하여 결과적으로 RPG-HBC는 인체 조직 내에서 발생할 수 있는 다양한 채널 조건 변화에 능동적으로 대응할 수 있다는 장점을 가진다.

[그림 4] 제안된 시스템 및 안정적인 통신을 위한 세 가지 모드

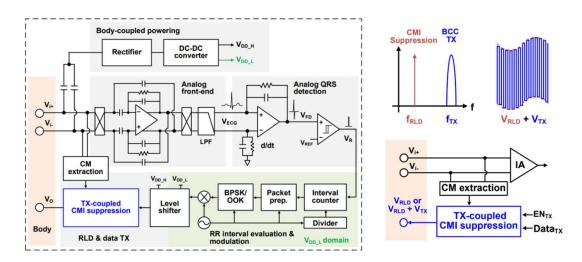

## #36-2 A Wireless Biopotential Sensing Node with Simultaneous Body-Channel Communication by TX-Coupled 21 VPP Common-Mode Interference Suppression

본 논문에서는 웨어러블 생체 신호 측정 시스템에서 저주파 생체 신호를 연속적으로 측 정하고 이를 body-coupled통신을 통해 외부로 전송하는 통합형 시스템을 제안했다. 일 반적인 웨어러블 시스템을 사용하여 생체 신호 측정과 무선 송신을 동시에 수행할 때, 통신회로와 생체 신호 측정회로 간 간섭이 발생하게 된다. BCC 송신기의 고주파 신호가 인체를 통해 RLD (Right-Leg-Driving) 회로의 공통모드 제거 경로로 누설되면서 송신 신 호의 출력이 제한되고 파형이 왜곡되는 문제가 나타난다. 이로 인해 실제 출력 스윙이 감쇄되어 통신 신뢰도가 떨어지게 된다. 이를 해결하기 위해 기존에는 BCC 신호를 회로 접지로 유도하거나 RLD 회로를 제거하고 인체와 회로 사이의 기생 커패시턴스를 활용하 는 방식을 사용했으나, 전력 소모가 크거나 공통모드 제거 성능이 저하되는 한계가 있었 다. 본 논문에서는 이러한 문제를 해결하기 위해 TX-coupled CMI 억제 기법을 제안했다. 이 구조에서는 RLD 출력과 BCC 송신 신호를 시간 영역에서 결합하여 두 회로가 동일한 전극을 공유하면서도 서로 간섭 없이 독립적으로 동작할 수 있게 한다. 두 신호는 다른 주파수 성분을 갖기 때문에 주파수 성분을 그대로 보존할 수 있다. 더불어 또한 RLD의 후단 증폭기와 송신 드라이버 회로를 통합하여 하드웨어 면적을 줄였고 송신이 꺼진 상 태에서는 저전류로 동작하도록 설계하여 전력 소모를 최소화했다. 본 논문은 생체 신호 측정 회로와 BCC 송신 회로 간의 경로 충돌 문제를 근본적으로 해결하면서도 높은 출력 과 안정적인 간섭 억제 성능 저전력 특성을 동시에 만족하는 회로 구조를 제시했다는 점 에서 장점을 가진다.

[그림 5] 제안된 시스템 및 TX-Coupled CM Interference 억제 기술

#### 위정윤 박사과정 대학원생

● 소속 : DGIST 전기전자컴퓨터공학과

● 연구분야: Analog ICs for biomedical application

이메일 : wiejung@dgist.ac.kr홈페이지 : http://ins.dgist.ac.kr

KAIST 전기및전자공학부 박사과정 윤기찬

# Session 36 Communication Computing and Sensing Techniques in Biomedical Systems

이번 2025 IEEE CICC의 Session 30은 Communication Computing and Sensing Techniques in Biomedical Systems라는 주제로 총 7편의 논문이 발표되었다. 그 중, biomedical 분야의 다양한 센서 인터페이스를 활용해 통함 시스템을 구현한 36-5, 36-6, 36-7 논문을 리뷰해보고자 한다.

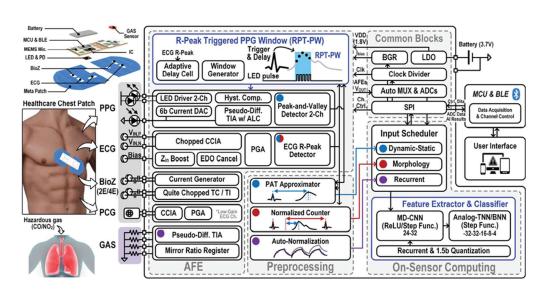

#36-5 본 논문은 UNIST에서 발표한 연구로, 다양한 생체 신호를 저전력으로 측정하고 실시간으로 분석하기 위한 chest patch 인터페이스 IC를 제안하였다. 제안하는 시스템은 PPG, ECG, BioZ, PCG 및 유해 가스를 측정할 수 있으며, 각 센서 인터페이스 회로에 최적화된 on-sensor computing 회로들을 포함하고 있다.

[그림 1] 제안하는 chest patch 인터페이스 IC

PPG 측정 회로는 LED 동작시에 많은 전력을 소모하게 되고, 이를 보완하기 위하여 ECG의 R-peak에 LED의 구동 타이밍을 동기화하는 ECG R-peak triggered PPG windowing (RPT-PW) 방식을 제안하여, 기존 방식에서 지속적인 재동기화의 필요성을 제거하였다. 또한, multi-domain CNN (MD-CNN)과 analog tenary/binary NN (a-TNN/BNN)으로 이루어진 on-sensor computing회로를 사용하여 pulse arrival time(PAT) 기반의 혈압 추정, 심장

부정맥 감지 및 유해 가스 감지 등 low latency로 다양한 작업을 정확하게 수행할 수 있다. 마지막으로, dynamic-static, morphology-based, recurrent 모드를 지원하여, 사용자의 설정에 따라 유연하게 조절할 수 있는 구조를 가진다.

제작된 ASIC은 실제 착용 가능한 chest patch 형태로 제작되었으며, RPT-PW widowing 알고리즘을 통해 약 cardiac cycle 대비 10%만의 윈도우 크기를 사용하며, 결과적은 LED duty cycle은 0.078%로 줄어들어 전력 절감이 가능했다. 또한, 다양한 classification작업에서 모두 sensitivity와 specificity를 90% 이상 달성하였다.

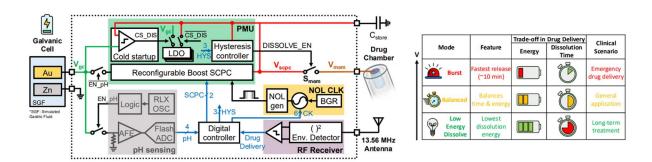

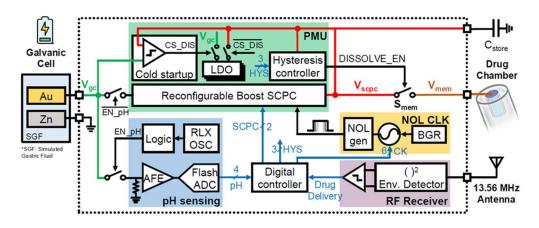

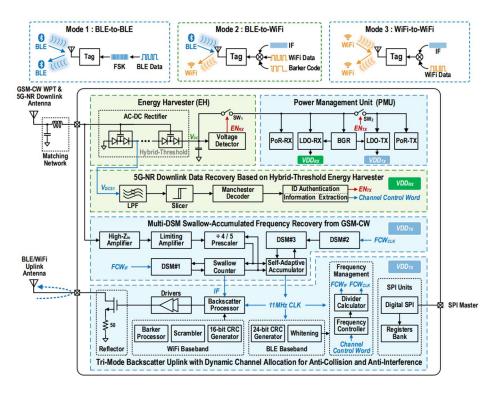

#36-6 본 논문은 Massachusetts Institute of Technology에서 발표한 연구로, 배터리 없이 동작하는 ingestible drug delivery chip을 제안하였다. 배터리 없이 동작하기 위해, galvanic cell (GC)을 활용하는 electrochemical energy harvesting 구조를 사용하여 위산 등의 gastrointestinal (GI) fluid로부터 직접 에너지를 얻는다. 또한, pH 변화에 따라 전력 효율이 달라지기 때문에, pH를 측정하고, 그에 따라 maximum power point tracking (MPPT) 하는 알고리즘 기반 기법을 활용하여 energy harvesting의 효율을 극대화하였다.

[그림 2] 제안하는 ingestible drug delivery IC

또한, 약물 방출은 전기화학적으로 용해되는 금속 membrane을 통해 이루어지며, pH에 따라 용해 전압이 달라지기 때문에 burst, balanced, low-energy의 세 가지 모드를 통해 최적화된 전압 및 clock 주파수를 설정하며, 방출 타이밍은 external RF신호 (13.56MHz ASK)를 통해 제어되었다.

제작된 ASIC은  $6mm^2$ 의 면적을 가졌으며, 전체 capsule size는 직경이 11mm였으며 29mm의 높이를 가졌다. 돼지 위장을 활용한 ex-vivo실험과 pH를 1과 3으로 조절된 simulated gastric fluid (GSF) 실험 환경을 통해 제작된 칩은 테스트되었으며, pH에 따른 MPPT 설정 및 약물 방출 속도 조절이 잘 됨을 확인하였다. Low-energy 모드에서는 burst 모드에 비해  $8\sim90\%$ 가량의 전력을 아낄 수 있었으며,  $10\mu$ W의 cold-start 전력만으로도 동작이 가능하였다.

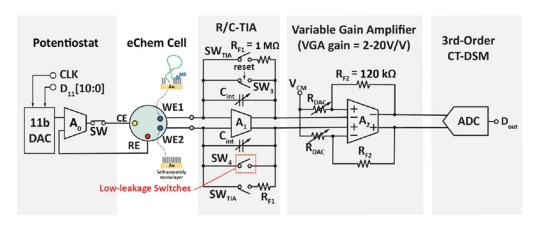

#36-7 본 논문은 University of California에서 발표한 연구로, bioreactor 내부에서 antibody의 농도를 실시간 및 continuous하게 측정할 수 있는 aptamer 기반 electrochemical 센서 및 readout IC를 제안하였다. 또한, structure-switching aptamer 기반의 biosensor를 활용하여 trastuzumab antibody를 선택적으로 검출할 수 있었다. 그리고, [1]에서 제시된 square-wave volcoulometry (SWVC) 기법을 configurable R/C-TIA를 사용하여 구현함으로써 noise-level은 비슷하게 유지되지만 signal을 100배 이상 키울 수 있어 14nM의 검출 한계를 달성하였다.

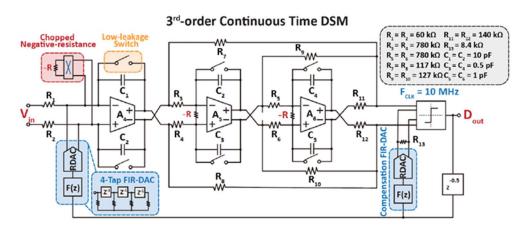

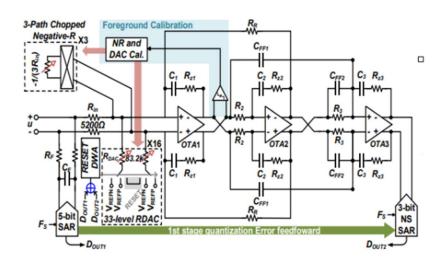

[그림 3] 제안하는 potentiostat IC

Electrochemical 전류는 TIA에 의해 증폭된 후, 고해상도 CT DSM으로 디지털화된다. ADC는 [2]의 구조를 활용하여 3차 noise-shaping이 구현되어 있으며, chopped negative resistance회로를 이용해 integrator 유한한 GBW에 의한 효과를 보정하고, FIR-DAC을 통해 chopping에 의한 noise-aliasing 제거 및 ripple을 제거한다. 결과적으로 91.2dB의 SNR 및 89dB의 SNDR을 20kHz의 대역폭으로 달성하였다.

[그림 4] Potentiostat IC에 사용된 고해상도 CT DSM

전체 current readout IC는 2.3mW를 소모하며 0.7pA<sub>rms</sub> (@2kHz)의 낮은 noise 성능을 도달하고, dynamic range는 83.4dB를 달성하였다. 또한, 검출된 데이터는 2.45GHz ISM 대역의 wireless 통신을 통해 80Mbps의 대역폭으로 외부로 전달되었으며, wireless data의 SNR은 21dB를 보여주었다. Trastuzumab aptamer를 이용한 측정에서는 14.6배 향상된 signal 크기를 보여주었고, aptamer의 농도 응답은 최대 300nM까지 선형이며, 14nM의 낮은 검출 한계를 기록하였다.

#### 참고문헌

[1] Y.-T. Hsiao *et al.*, "A CMOS/Microfluidics Point-of-Care SoC employing Square-Wave Voltcoulometry for Biosensing with Aptamers and CRISPR-Cas12a Enzymes," in *Proc. IEEE Symp. VLSI Circuits*, Jun. 2023, pp. 1–2.

[2] M. Jang, C. Lee and Y. Chae, "A 134-µW 99.4-dB SNDR Audio Continuous-Time Delta-Sigma Modulator With Chopped Negative-R and Tri-Level FIR-DAC," *IEEE J. Solid-State Circuits*, vol. 56, no. 6, pp. 1761-1771, June 2021.

#### 저자정보

#### 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야: Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

• 홈페이지 : https://impact.kaist.ac.kr

DGIST 전기전자컴퓨터공학과 박사과정 위정윤

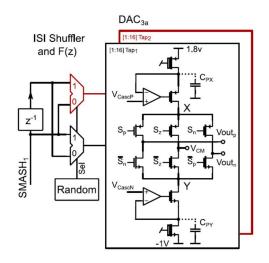

#### **Session 5 Incremental ADCs**

2025 IEEE CICC의 Session 5에서는 "Incremental ADC"를 주제로 총 3편의 기술 논문이 발표되었다. Incremental ADC는 높은 에너지 효율을 제공하는 구조로, multi-step 양자화를통해 정밀도를 향상시키거나, 단일 스텝 구조에서도 기존의 free-running 방식보다 우수한 성능을 달성하려는 다양한 연구가 진행되고 있다. Multi-step 양자화 방식에서는 첫번째와 두 번째 단을 연결하는 residue amplifier의 이득 정확도를 높이거나, 전체 구조의에너지 효율을 극대화하는 방향으로 연구가 집중되고 있다. 반면, 단일 스텝 기반의 구조에서는 루프 필터의 차수 및 OSR(oversampling ratio)을 조정하여 최적의 noise shaping특성을 구현하고, 선형성 저하의 주요 원인이 되는 DAC 설계에 초점을 맞춘 연구가 활발히 이루어지고 있다.

## #5-2 A 133.6-μW 1kHz-BW Multi-bit 2nd-order Incremental ADC Achieving 115.4-dB SNDR with Low-Cost Coarse-Sorting DEM and Zip-Extended-Counting

본 논문에서는 1kHz 대역폭을 갖는 2차 Incremental ADC 구조를 제안하였다. DAC mismatch로 인한 비선형성을 효과적으로 평균화하기 위해 Coarse-Sorting DEM 기법을 도입하였으며, 이를 통해 115.4dB의 높은 SNDR을 달성하였다. 또한, Zip-Extended-Counting 기법과 6bit SAR quantizer를 결합하여 단일 스텝 Incremental ADC에서 extended counting 동작을 구현하였으며, 이는 5bit SAR quantizer, 이득 2의 residue amplifier, 그리고 1회의 extended counting을 조합한 것과 동등한 성능을 제공한다. Incremental ADC는 매 변환마다 적분기가 초기화되기 때문에, free-running ADC와 달리 DEM을 통한 mismatch 평균화 효과가 제한적이다. 특히 루프 필터의 차수가 높고 OSR 이 낮을 경우, 각 샘플의 timing에 따라 mismatch가 출력에 다르게 반영되어 선형성 저하가 더욱 두드러지는 문제가 발생한다. 이를 해결하기 위해 본 논문에서는 저복잡도 구조의 Coarse-Sorting DEM (CSDEM)을 제안하였다. 제안된 기법은 5bit DAC, 즉 32개의 unit element에 대해, 인접한 4개의 element 내부에서 rank를 구하고, 이를 다시 4개씩 그룹화하여 그룹 간 rank를 계산한 뒤, 최종적으로 결합된 rank에 따라 weight를 설정하는 방식으로 동작한다. 이때 각 element는 level register와 weight register를 통해 상태가 추적되며, 해당 정보를 기반으로 partial sorting을 수행한다. 제안된 CSDEM은 기존

[그림 1] 제안된 시스템과 Coarse-Sorting DEM 기술 및 효과

Smart-DEM과 비교할 때 구조적으로 큰 차별성을 가진다. Smart-DEM은 mismatch 평균화 성능이 우수하나, 완전한 정렬(sort)과 고속 클럭(N²×Fs)에 의존하여 하드웨어 복잡도와 전력 소모가 급격히 증가하는 단점이 있다. 반면 본 논문에서 제시한 CSDEM은 partial sorter와 coarse-sorting 알고리즘을 활용하여 이러한 복잡도를 O(N) 수준으로 억제하였으며, 496개의 10-bit comparator가 필요한 기존 구조 대신 48개의 7-bit comparator만으로 충분한 mismatch suppression 효과를 제공함을 보였다. 다만, 제안된기술의 효과를 더욱 명확히 입증하기 위해서는 일반적인 정현파 입력뿐 아니라 다양한입력 시나리오에 대한 PSD(전력 스펙트럼 밀도) 분석 결과가 함께 제시된다면, CSDEM기법의 전반적인 안정성과 범용성을 더욱 설득력 있게 강조할 수 있을 것으로 기대된다.

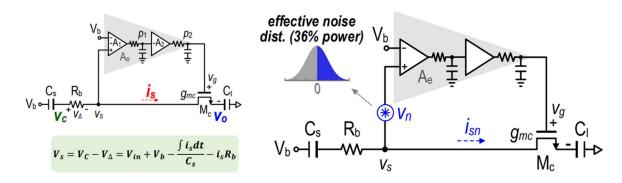

## #5-3 A 16-bit Incremental ADC Enabled by An Efficient Shooting Integrator with Inherent Noise Reduction

본 논문에서는 새로운 "shooting integrator" 구조를 기반으로 한 2차 incremental  $\Delta\Sigma$  ADC (I $\Delta\Sigma$ M)를 제안한다. 기존의 switched-capacitor 기반 integrator는 적분기의 settling 시간, 커패시턴스 크기, 출력 선형성 등 다양한 아날로그 설계 요소에 의해 전력 소모와 성능 간 trade-off가 발생하며, 증폭기 설계의 복잡도 또한 상당히 높은 편이다. 이러한 한계를 극복하기 위해 본 논문에서는 feedback loop와 barrier resistor를 이용해 반복적인 전하 전달(shooting transfer)을 수행하는 shooting integrator를 제안하였다. Shooting integrator는 입력 커패시터( $C_s$ ), barrier resistor(Rb), 그리고 error feedback amplifier(Ae)로 구성되며, 전하가 고속으로  $C_s$ 에서 적분 커패시터  $C_t$ 로 이동하는 과정을 반복함으로써 안정적이고 선형적인 전하 전달을 구현한다. 이 과정에서 comparator나 ring amplifier처럼 과도 응답이나 overshoot를 유발할 수 있는 구조적 불안정성이 제거되어 매우 정밀한 적분 동작이 가능하다. 특히 Ae는 오직 증폭기의 DC 이득과 극점 위치만을 고려해 설계하면 되며, 정착 속도나 커패시턴스의 크기에 크게 영향을 받지 않기 때문에 증폭기

[그림 2] 제안된 shooting 적분기

의 복잡도와 전력 소모를 대폭 줄일 수 있다. 기존의 integrator 설계에서는 선형성, 출력 스윙, 출력 공통 모드 레벨 등의 요소가 매우 민감하게 작용하여 회로 성능을 제한하였으나, shooting integrator 구조에서는 이러한 항목들이 더 이상 주요 제약 요소로 작용하지 않는다. 실제로 제안된 16-bit incremental ADC는 shooting integrator를 핵심으로 채택하여 180nm CMOS 공정에서 제작되었으며, 500kHz 클록 기준으로 6.28µW의 낮은 전력을 소모하면서도 최고 97.5dB의 SNR과 174dB의 Schreier FoM을 달성하였다. 또한 pseudo-differential 구조와 결합될 경우 shooting 과정에서 발생하는 노이즈가 Gumbel 분포를 따르며, 경로 간 최대 노이즈가 상쇄되어 최대 75%까지 노이즈 파워를 억제할수 있음이 확인되었다. 결과적으로, 본 논문에서 제안된 shooting integrator는 기존 SC integrator의 복잡한 설계 제약을 제거하고, 전력 효율을 극대화하면서도 고정밀의 성능을 달성할 수 있는 새로운 적분기 구조로서 우수성을 입증하였다. 향후 이 구조는 고정밀 저전력 데이터 컨버전 시스템의 핵심 요소로 널리 활용될 수 있을 것으로 기대된다.

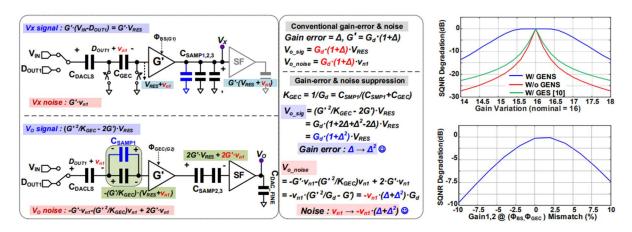

## #5-4 A 50-kHz BW 92.1-dB SNDR Incremental ADC Using a Back-End Sampling Two-Step NS-SAR Architecture with Concurrent Gain-Error + Noise Suppression

본 논문에서는 50kHz 대역폭을 갖는 Noise-Shaping SAR ADC(NS-SAR ADC) 기반의 two-step Incremental ADC 구조를 제안한다. 첫 번째 단계에서는 continuous-time tracking SAR ADC를 활용하여 AC-coupled 입력 신호를 양자화하고, 그 결과는 CDAC 에 샘플링된다. 이후 CDAC 을 입력 노드에 연결하면, 출력에는 첫 번째 단계에서 제거되지 않은 잔류 전압만이 남는다. 이 잔류 전압은 Concurrent Gain-Error and Noise Suppression(CGENS) 기법을 통해 이득 오차를 억제하며 증폭되고, 두 번째 단계에서 NS-SAR ADC 에 의해 정밀하게 양자화된다. Two-step 구조에서 첫 번째와 두 번째 단을 연결하는 residue amplifier의 이득 정확도는 최종 SQNR 성능을 결정하는 핵심 요소이다. 일반적으로 에너지 효율 향상을 위해 floating-inverter 기반 증폭기가 널리 사용되나, 고정된 이득 특성으로 인해 gain error 가 발생하며 이는 SQNR 및 선형성 저하로 이어지는 문제가 있다. 본 논문에서는 이러한 한계를 극복하기 위해, floating amplifier 의

[그림 3] 제안된 이득 에러 효과 억제 기술

gain error 를 효과적으로 억제하는 기법을 제안함으로써, 높은 선형성과 SQNR을 동시에 달성하였다. 제안된 기법은 전력 효율을 유지하면서도 선형성을 개선할 수 있다는 점에서 중요한 장점을 갖는다.

## 저자정보

위정윤 박사과정 대학원생

한국과학기술원 바이오및뇌공학과 박사과정 석동열

#### Session 13 High-Speed Nyquist ADC

이번 2025 IEEE CICC의 Session 13, High-Speed Nyquist ADC에서는 총 5편의 논문이 선정되어 발표되었다. 이 세션에서는 Nyquist 샘플링을 수행하는 고속 ADC의 성능 개선을 주제로 하는 연구를 다루고 있으며, time-interleaved ADC에서의 시간 오차(timing-error)로 인한 노이즈를 극복하기 위해, TD(time-domain), SAR(successive approximation register), pipelined 등 다양한 ADC 기본 구조를 융합 하여 속도 및 해상도 개선을 이루어 낸 사례, 고속 ADC에서 PVT 변화 대응을 위한 연구 등이 소개되고 있다.

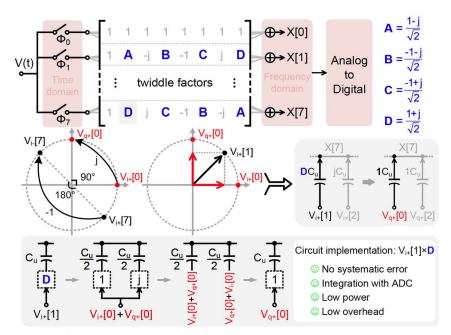

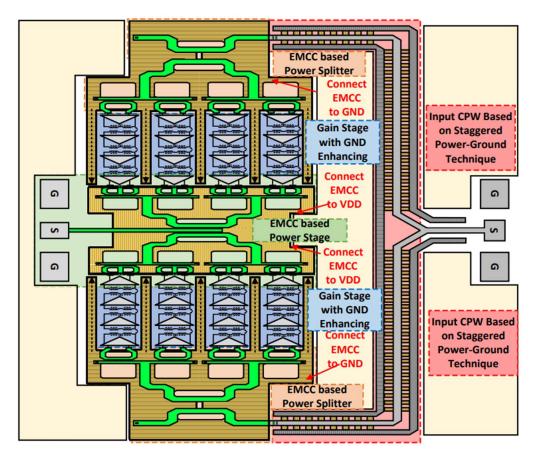

#13-1 본 논문은 중국 전자과기대학(UESTC) 연구진 등이 게재한 논문으로 10b 해상도로 13GS/s 수준 고속 샘플링 성능을 보여주는 주파수-인터리빙(frequency-interleaved) 방식의 ADC 연구를 소개하고 있다. 고속 샘플링에서 자주 활용되는 기법인 시간-인터리빙(time-interleaved)은 병렬로 구성된 ADC가 아주 짧은 시간차를 두고 교대로 샘플링하는 방식으로 고속 샘플링을 구현해 낼 수 있지만, ADC 간 샘플링 시간(timing) 오차가 바로고주파 영역에서의 성능(SNDR 등) 저하로 이어지는 문제가 있다.

연구진은 이를 극복하기 위하여 시간-인터리빙 방식으로 시스템에 유입되는 radix-8의 아날로그 푸리에 연산을 통해 주파수 도메인의 값으로 변환하여 출력하는 방식으로 시간 오차에 대한 ADC의 민감성을 떨어뜨렸다. 또한, 푸리에 변환 연산을 위한 복소수 계수 값을 스위치-커패시터를 활용한 전하 재분배(charge redistribution) 방식을 이용하여 생성하여 대역통과필터를 활용한 기존의 주파수 분할 방식에 비해 전력 효율면에서도 이점을 보여주었다. 그 결과 jitter, bandwidth mismatch, time skew 등 시간 오차가 유발되었을 때, 시간-인터리빙 방식의 샘플링에 비해 나은 성능을 SNDR 등의 지표에서 13GS/s 수준의속도에서 나은 SNDR 지표를 보여주었다. 측정 결과로 SNDR 45.8[dB], SFDR 56.1 수준의성능을 보고했으며, 26.4mW 수준의 전력소모, 12.7 fj/conv.-step 수준의 Walden FoM을 달성하여 기존 연구와의 차별성을 보여주었다. 본 회로는 28nm CMOS 공정으로 제작되었으며 활용한 면적은 0.126mm² 이다.

Fig. 2. Circuit implementation of the radix-8 AFT with irrational coefficients.

[그림 1] Xingchen Chao와 연구팀은 커패시터 충·방전 제어로 실시간 radix-8 푸리에 변환 위한 복소수 계수(complex coefficients)를 구현하였으며, 이를 활용한 주파수-인터리빙 ADC(frequency-interleaved ADC)를 선보였다. 주파수-인터리빙 ADC는 시간오차에 상대적으로 둔감하여 비슷한 조건의 고속 샘플링에서 시간-인터리빙 ADC에 비해 시간오차에 견고하며, 더 나은 A/D 변환 성능을 보여준다.

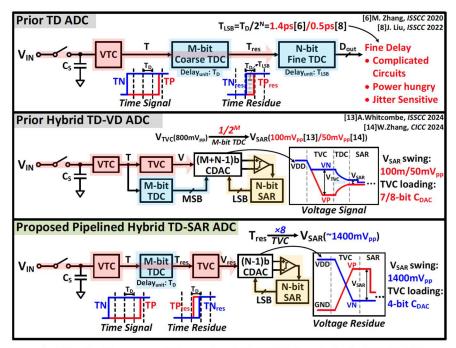

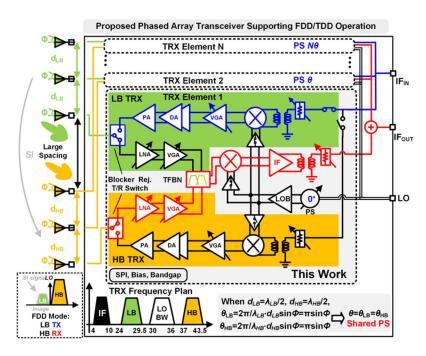

#13-2 본 논문은 마카오 대학을 포함한 총 6개 연구기관의 연구팀이 참여한 연구를 소개하고 있다. 전력효율성이 높은 고속 ADC 설계를 위해 고속 샘플링이 가능한 TD-ADC(time-domain ADC, 시간 도메인 ADC)와 SAR(successive approximation register) ADC를 결합한 하이브리드 TD-SAR ADC를 제안했다. TD-ADC의 경우 고해상도를 얻기위해서 많은 딜레이 셀이 필요하며, 이를 확보하기 위해서 면적, 전력과 같은 자원이 많이 필요하다는 단점이 있으며, PVT 변화에 성능이 민감하게 달라진다는 한계를 가지고있으며, SAR의 경우 전력 효율이 뛰어나고 구조가 단순한 반면 A/D 변환을 위해 여러차례 비교가 필요한 특성을 인해 고속 샘플링에서는 한계에 마주하게 된다.

연구진은 이러한 한계를 극복하고 양 구조의 이점을 충분히 활용하기 위하여 입력단에서는 TD-ADC 구조를 활용하여 고속으로 MSB를 결정하고 나머지 값(residue)에 대해서는 시간-전압 변환 회로(TVC, time-voltage converter)를 활용하여 전압 값으로 변환한 뒤 5-bit SAR를 이용하여 나머지 값을 양자화하는 과정을 거치는 파이프라인을 구성하였다. 제안하는 구조에서는 TD-ADC에서 3bit를 결정하고, 나머지 값을 5-bit SAR(샘플링 속도: 3.125GS/s)로 결정하여 총 7bit의 해상도를 갖는 구조이다. 이러한 방식으로 12.5GS/s 수준의 고속 샘플링을 하면서도 전력 효율을 끌어올려 14.7mW 수준의 전력 소모,

24.3fJ/conv-step의 Waldon FoM을 달성하였다. 또한, 12.5 GS/s의 고속 샘플링에서 35.45[dB] 수준의 SNDR, 48.28[dB] 수준의 SFDR을 달성하였으며, 0.5에서 6.5GHz의 입력 주파수 구간에서 2.7dB 이내의 SNDR 변화, -20℃에서 80℃ 사이의 온도변화에서도 2dB 이내의 SNDR 변화를 보고하였다. 본 회로는 28nm CMOS 공정으로 제작되었으며, 총 0.0126 mm²의 면적 안에 제작되었다.

Fig. 1. Block diagram of the prior TD ADC (top), hybrid TD-VD ADC (middle) and the proposed pipelined hybrid TD-SAR ADC (bottom).

[그림 2] Haoyu Li와 연구팀은 고속 샘플링이 가능한 TD-ADC의 이점과 에너지 효율성이 높은 SAR-ADC의 이점을 모두 활용할 수 있는 하이브리드 형의 파이프라인 하이브리드 TD-ADC를 제안하였다. (그림 2의 가장 아랫상자)

#### 저자정보

#### 석동열 박사과정 대학원생

● 소속 : 한국과학기술원

● 연구분야 : 바이오메디컬 응용 회로설계(센서 및 신호처리)

• 이메일 : sukd10@kaist.ac.kr

KAIST 전기및전자공학부 박사과정 윤기찬

#### **Session 30 Continuous-Time ADCs**

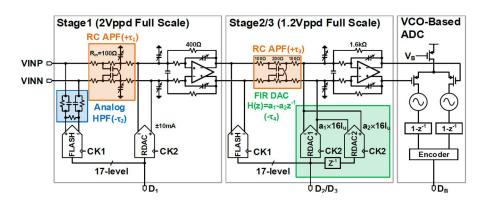

이번 2025 IEEE CICC의 Session 30은 Continuous-Time ADCs라는 주제로 총 4편의 논문이 발표되었다. 3편의 논문은 높은 해상도를 얻기 위해 noise-shaping을 적용한 CT DSM 구조의 논문이었으며, 1개의 논문은 넓은 대역폭을 얻기 위한 CT pipeline ADC를 제안하였다. 본 review에서는 그 중 30-2, 30-3, 30-4를 리뷰하고자 한다.

#30-2 본 논문은 Tsinghua university에서 발표한 연구로, CT pipeline ADC에서 signal path 와 quantization path간 발생하는 delay mismatch 문제를 해결하기 위해 각 stage 별로서로 다른 delay alignment technique을 활용한 hybrid 구조를 제안하였다. CT pipeline ADC에서는 quantization하고, DAC이 동작하기 까지의 delay가 signal에 leakage가 발생하게 된다. 기존에는 LC lattice 구조를 사용하거나 RC all-pass filter (APF)를 사용하였지만, 면적이 너무 크거나 delay alignment가 부정확하였다. Time-interleaving 구조도 제안되었으나 전력소모와 면적이 매우 크게 증가한다는 단점을 가지고 있었다.

제안하는 구조에서 1<sup>st</sup> stage에는 RC APF에 더해 quantization path에 high-pass filter를 추가하여 analog negative delay를 형성함으로써, 필요한 RC APF의 delay 요구사항을 줄일 수 있었다. 2<sup>nd</sup> stage에서는 passive 소자들의 PVT variation을 개선하기 위하여 quantization path에 FIR DAC을 사용하였다. 결과적으로 제안된 hybrid delay alignment 구조를 통해, 73.8dB DR, 450MHz 대역폭, 0.16mm²을 달성하여 우수한 성능을 달성하였으며, PVT variation에 강인하면서도 area-efficient한 delay alignment 방식을 통해 163.2dB의 Schreier FoM을 달성하였다.

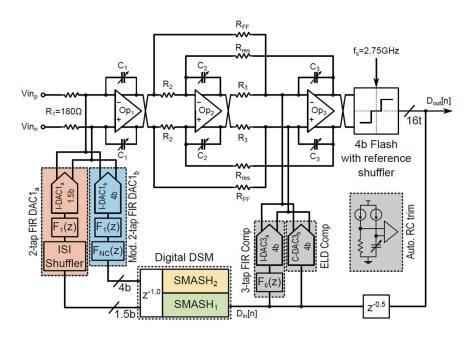

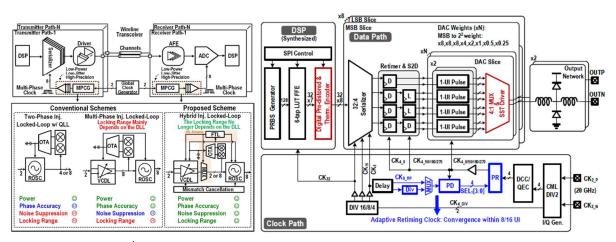

[그림 1] 제안하는 CT Pipeline ADC 구조

#30-3 본 논문은 University of Ulm에서 발표한 연구로, CT DSM에서 multi-bit quantizer 를 사용하였을 때 DAC 간의 mismatch로 인해 발생하는 문제를 dual quantization 기반 sturdy MASH (SMASH) 구조와 inter-symbol interference (ISI) shuffler를 결합한 구조를 제 안하였다. Multi-bit CT DSM은 일반적으로 높은 해상도와 jitter robustness를 가지지만, DAC mismatch로 인해 linearity가 나빠지게 되고, 제안된 구조에서는 2-2 SMASH 구조의 digital DSM (DDSM)를 사용하여 DAC을 2개로 분리하여 구현하였다. DAC1a는 signal path 를 담당하며, 해당 DAC에 해당하는 1.5b quantization noise는 DAC1b에 의해 noise-coupling 되어 고해상도를 도달함과 동시에 linearity requirement를 크게 줄일 수 있었다.

[그림 2] 제안하는 Dual quantization CT DSM 구조

또한, ISI의 영향을 줄이기 위해 FIR DAC인 DAC1a tap 수를 random하게 shuffling하여 logic의 rise time과 fall time을 랜덤화 하였고, headroom과 noise 성능을 위하여 supply voltage를 사용하였다. 또한, reference folding과 zipper reference shuffling [1] 기법을 4b flash quantizer에 추가하여 동작 속도를 향상시킴과 동시에 전력 효율을 높일 수 있었다. 결과적으로 제안된 구조는 2.75GHz의 높은 동작 주파수에, 80MHz 대역폭 및 71dB의 SNDR을 43.3mW의 전력만을 소모하면서 달성하여, 163.7dB의 Schreier FoM을 달성하였다. 또한, mismatch tone들을 shuffling을 통해 제거하여 calibration없이 106.2dB의 높은 SFDR을 달성할 수 있었다.

[그림 3] 제안하는 ISI Shuffler 구조

#30-4 본 논문은 Tsinghua university에서 발표한 연구로, 1-bit CT DSM의 feedback DAC으로 인한 OTA의 높은 전력 소모 및 jitter sensitivity문제를 해결하기 위해 direct charge dump (DCD) technique을 제안하였다. 기존 1-bit CT DSM은 calibration-free하고, loop filter의 loading이 작다는 장점을 가지고 있지만, 첫번째 integrator의 OTA가 1-bit DAC을 빠르게 따라가야 해 전력 소모가 매우 크며, sampling jitter에 민감한 특징을 가지고 있어, Schreier FoM이 multi-bit에 비해 부족하다.

[그림 4] 제안하는 DCD기술이 적용된 CT DSM 구조

제안하는 DCD 구조는 기존 방식과 다르게 OTA가 feedback 경로에 관여하지 않고, feedback capacitor에 저장된 charge를 integration capacitor에 dump하여 integration을 진행하게 된다. 이를 통해 OTA는 input signal에 대해서만 처리하기 때문에 OTA1의 전력 소모를 1.5mW까지 줄일 수 있었다. 또한, 기존 NRZ current DAC을 활용한 구조보다 높

은 jitter tolerance를 달성할 수 있었으며, CT DSM의 anti-aliasing 특성을 유지하기 위해서 ping-pong operation을 적용하여 loop filter의 특성을 유지하고자 하였다. 프로토타입은 4차 noise-shaping을 달성하였으며 3.2GS/s에서 76.3/73.2dB의 SNDR을 25/40MHz 대역폭에서 얻어내었고, 4.2mW만을 사용하여 174.0/172.9dB의 Schreier FoM을 달성하였다.

#### 참고문헌

[1] T. Caldwell *et al.*, "A Reconfigurable  $\Delta\Sigma$  ADC With Up to 100 MHz Bandwidth Using Flash Reference Shuffling," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 8, pp. 2263-2271, Aug. 2014.

#### 저자정보

#### 윤기찬 박사과정 대학원생

● 소속 : KAIST

• 연구분야: Mixed-signal IC & Sensor interface IC

• 이메일 : ygc980215@kaist.ac.kr

• 홈페이지 : https://impact.kaist.ac.kr

단국대학교 파운드리공학과 석사과정 조혁준

#### Session 35 High-Resolution and Noise-Shaping ADCs

Session 35에서는 고해상도 응용 분야에 적합한 고성능 ADC를 주제로 총 8편의 논문이 발표되었다. 최근에는 CT  $\Delta$   $\Sigma$  ADC와 멀티 비트 양자화를 활용한 2단계 Zoom ADC 구조에 관한 연구가 진행되고 있으며, 이러한 구조에서는 DAC mismatch로 인한 선형성 저하가 주요한 과제로 부상하고 있다. 기존에는 이를 해결하기 위해 DEM(Data-Weighted Averaging)이나 MES(Mismatch Error Shaping) 기법이 사용되었으나, 이러한 방식은 낮은 OSR 환경에서 shaping 효과가 감소하고, 입력 주파수가 증가할수록 비선형성이 심화하며, 동시에 회로 복잡성과 전력 소모 증가라는 한계를 갖는다. 이번 세션에서는 이러한 문제를 해결하고자, FIR DAC를 도입하여 DEM이나 MES 없이도 고 선형성을 구현한 Zoom ADC, CT  $\Delta$   $\Sigma$  ADC, 그리고 Tri-level 구조와 보정 기법을 통해 선형성을 개선한 ADC 논문들이 발표되었으며, 본 리뷰에서는 이들 주요 연구를 중심으로 살펴보고자 한다.

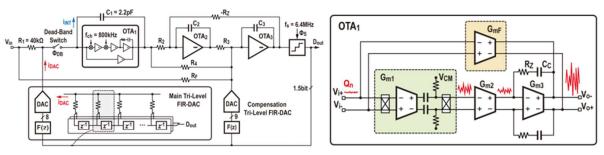

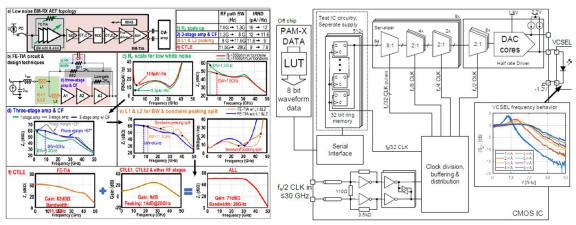

#35-1 본 논문은 마카오대학교에서 발표한 논문으로, 고성능 ADC에서 발생하는 높은 OSR과 전원 전압 요구로 인한 전력 소모, 클럭 오버헤드, 전원/접지 잡음 및 면적 부담 문제를 지적한다. 이를 해결하기 위해, 낮은 OSR에서도 높은 SNDR과 에너지 효율을 달 성할 수 있는 CT-Zoom ADC 구조를 제안한다. 제안된 CT-Zoom ADC는 AA 필터, 5-bit SAR Coarse ADC, 3차 CRFF 루프 필터, 3-bit 2차 NS Fine ADC, 그리고 저항 기반 Tri-level DAC로 구성된다. Zoom 구조를 통해 루프 필터 입력 전 신호를 줄이고, 5차 Noise Shaping을 통해 낮은 OSR에서도 고성능을 유지한다. 하지만 기존 DEM 기반 DAC mismatch shaping은 낮은 OSR 및 고주파 입력에서 성능 저하가 심하다. 이를 해결하기 위해, 본 논문은 Reset Tri-level DWN(RST-TDWA)와 Foreground calibration을 도입한다. RST-TDWA는 포인터 동작의 주기성을 활용해 mismatch 오류를 1차 shaping 된 이진 신 호로 변형시켜 SNR 향상을 달성한다. 또한, Tri-level DAC 구조는 저항 수를 줄이고 안정 성 및 낮은 Flicker Noise를 확보하며, RF와 CF로 구성된 패시브 필터는 약 70dB의 앨리 어싱 억제를 제공한다. Coarse ADC는 패시브 전하 공유 방식으로 Fine ADC에 전달되며, RC 필터를 통해 사전 필터링되어 높은 앨리어싱 억제 성능을 유지한다. 제안된 ADC는 65nm CMOS 공정으로 제작되었으며, 105.4dB SNDR, 105.7dB SNR, 106.3dB DR를 달성하 였고, 최종적으로, 48x OSR 환경에서 186.0dB의 FoM<sub>SNDR</sub>을 기록하였다.

[그림 1] 제안된 CT-Zoom ADC의 회로도

#35-5 본 논문은 중국 베이징대학교에서 발표된 연구로, 고성능 CTDSM에서 멀티 비트양자화기는 해상도 향상에 유리하지만, DAC 불일치로 인해 DEM 회로의 복잡성과 전력소모가 증가하는 한계를 가진다. 반면, 싱글 비트 양자화기는 구조가 단순하고 선형성이우수하나, 큰 양자화 잡음과 적분기 선형성 확보의 어려움이 존재한다. 이를 해결하기 위해 본 논문에서는 Hybrid Gm-Boosting OTA와 Tri-Level FIR DAC를 결합한 CTDSM 구조를제안한다. 제안된 CTDSM은 2단 피드 포워드 구조의 Hybrid Gm-Boosting OTA를 도입하여 잡음과 대역폭을 독립적으로 최적화하며, 각 Gm 블록은 기능에 따라 분리 설계된다. Gm1은 저 잡음과 넓은 대역폭을, Gm2와 Gm3는 높은 DC 이득을 제공하고, GmF는 입력 부스트 OTA를 통해 높은 GBW와 넓은 출력 스윙을 확보하며 주파수 보상을 수행한다. 또한, 양자화기에는 Tri-Level FIR DAC을 적용하여 양자화 잡음을 저감하고 선형성을 향상했으며, FIR 필터에는 Chopping을 통해 Flicker Noise를 억제하고 앨리어싱을 방지한다. DAC는 저 잡음과 구현 용이성을 고려해 저항 기반으로 구성되었다. 제안된 CTDSM은 별도의 DEM이나 보정 회로 없이도 고성능을 구현하며, 180nm 공정에서 제작되어 20kHz 대역폭과 128의 OSR 환경에서 99.5dB의 SNDR, 104dB의 DR, 182.1dB의 FoM<sub>SNDR</sub>을 달성하였다.

[그림 1] 제안된 CTDSM의 구조와 1st 적분기의 OTA 회로도

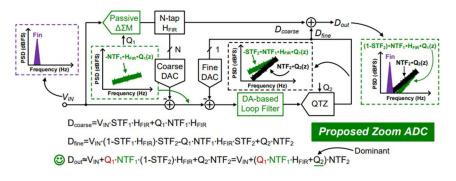

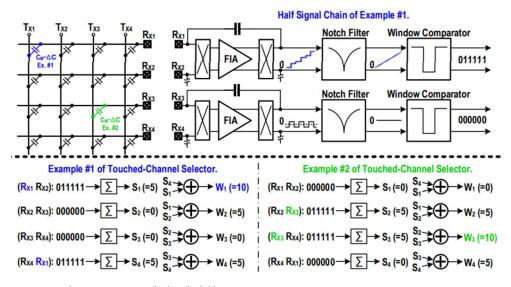

#35-6 본 논문은 중국 시안전자과기대학교에서 발표된 연구로, SAR과 델타-시그마 ADC를 결합한 Zoom ADC 구조에서 발생하는 양자화 잡음 누설과 DAC 선형성 문제를 해결하고자 한다. 이를 위해 Coarse 단계에 완전 패시브 1차 델타-시그마 모듈레이터를 도입하여 증폭기 없이도 Noise Shaping을 구현하고, FIR DAC를 활용해 DAC mismatch를 개선함으로써 고선형·고효율 스위치드 커패시터 Zoom ADC를 제안한다. 제안된 구조는 스테이지 간 양자화 잡음 누설을 억제하면서도 전력 소모를 낮추며, 12 탭 FIR 필터를 통해본질적으로 선형적인 멀티 비트 피드백 경로를 구현하여 DWA나 별도의 보정 없이도 높은 선형성을 확보하였다. Fine 단계는 FIA 기반 증폭기를 사용하는 델타-시그마 모듈레이터로 구성되어, 높은 이득 선형성과 정적 전류 소모 제거, 샘플링 속도에 따른 전력 조절특성을 갖는다. 제안된 ADC는 65nm 공정으로 제작되었으며, 5.12 MS/s 샘플링 속도에서 100.7 μ W를 소모하면서 101.1dB의 SNDR, 123.5dB의 SFDR, 121.2dB의 THD, 183.9dB의 FoMDR 성능을 달성하였다. 특히 별도 보정 없이 -120dB 이하의 THD를 통해 초고선형성을 달성하였다.

[그림 1] 제안된 Zoom ADC

[그림 2] 제안된 Zoom ADC의 상세 회로 및 타이밍 다이어그램

## 저자정보

### 조혁준 석사과정 대학원생

● 소속 : 단국대학교 파운드리공학부

● 연구분야: Biomedical Circuits ● 이메일: sdi5236@dankook.ac.kr

● 홈페이지: https://sites.google.com/dankook.ac.kr/acs-lab

포항공과대학교 반도체대학원 박사과정 박은빈

#### **Session 11 ASIC and Accelerator**

이번 CICC 2025의 Session 11에서는 AI 가속기 및 특화된 ASIC 설계를 주제로 총 8편의 논문이 발표되었다. 다양한 응용 분야에서 요구되는 고효율, 저전력 연산을 실현하기 위해, 각 논문은 특화된 데이터 표현 방식, 연산 아키텍처, 그리고 하드웨어-소프트웨어 협력 최적화 전략을 제안하였다. 특히 신경망 압축, reinforcement learning, spiking neural networks, LLM fine-tuning, 그리고 mmWave 기반의 OTA 레이더 처리까지 폭넓은 기술스펙트럼이 다루어졌다.

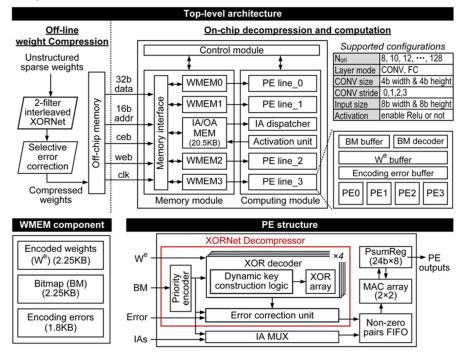

#11-3 본 논문은 상하이교통대와 콜롬비아대 공동 연구팀이 발표한 것으로, 고압축 희소 신경망 모델의 온칩 비복원 압축 해제 구조를 갖춘 NN 가속기 SparseTrim을 제안한다. 기존 희소 가중치 압축 방식은 압축률이 낮거나 직렬 해제가 병렬 연산 구조에 비효율적인 문제가 있었으나, SparseTrim은 XORNet 기반 압축 포맷을 활용해 이러한 문제를 해결하였다. XORNet은 fine-grained sparsity를 활용하여 압축 중 일부 오류를 허용한 뒤, 중요오류만 선택적으로 복구하는 방식으로 고압축을 실현하며, 최대 5.3배 (INT8 기준)의 압축률을 제공한다.

[그림 1] SparseTrim 과 PE의 전반적인 구조

이 논문에서는 해당 포맷에 맞춘 경량 동적 해제 키 생성 하드웨어를 설계하여 기존 LUT 기반 해제 방식 대비 면적을 52배 감소시켰고, PE 간 연산 부하 불균형 문제를 완화하기 위해 filter-pair 기반 부하 균형 기법도 함께 제안하였다. SparseTrim은 28nm 공정으로 제작되었으며, INT8 기준 최대 10.1 TOPS/W의 시스템 에너지 효율을 달성하였다. 이는 기존 COO, RLC, CFO 기반 방식 대비 평균 23~24% 높은 효율을 보였고, ResNet50 기준 throughput이 22% 개선되는 효과도 함께 입증되었다. 본 연구는 압축된 희소 신경망의 실시간 처리에 적합한 가속기 구조를 제시함으로써, 메모리 대역폭 제약과 에너지 병목을 동시에 해결한다는 점에서 의의가 크다.

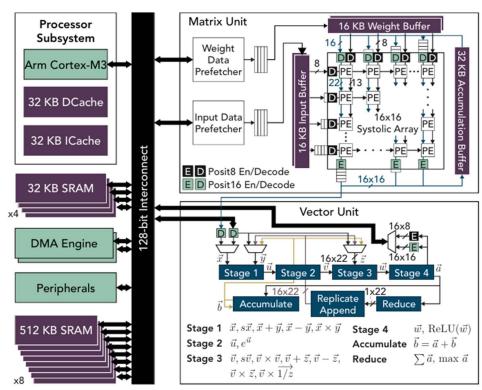

#11-4 본 논문은 스탠퍼드대학교에서 발표한 것으로, 확장현실(XR) 환경에서 실시간 인식 작업을 위한 통합형 가속기 SoC인 Aspen을 제안한다. 기존 XR 기기에서는 시각관성 측위(VIO), 시선 추적, 객체 인식 등 다양한 인식 파이프라인을 별도의 하드웨어로 처리했으나, 이로 인한 전력 소모 증가가 문제였다. 이를 해결하기 위해 본 논문은 모든 인식 작업을 DNN 기반으로 통합 처리할 수 있는 통합형 DNN 가속기 구조를 설계하였다.

[그림 2] Aspen의 전반적인 구조

Aspen의 주요 기술로는, 정밀도 손실 없이 메모리 사용량을 줄이기 위한 Posit 기반의 mixed-precision quantization 전략이 있다. 특히 정밀도가 중요한 VIO의 경우, 입력 특성에 따라 Posit8과 Posit16을 계층적으로 혼합하여 활용하며, 전용 vector unit과 systolic array 기반의 matrix unit을 통해 고성능 연산을 영역별로 최적 수행한다. 또한, 데이터

layout 일관성 유지와 효율적인 prefetching을 통해 메모리 접근 병목을 해소하였다. 그결과, Aspen은 VIO 98.9 FPS, 시선 추적 630 FPS, 객체 인식 31 FPS의 실시간 성능을 달성하였고, 모델 전체를 온 칩 4MB SRAM에 수용함으로써 외부 메모리 접근을 제거하였다. 특히 Posit quantization을 통해 FP32 대비 74% 메모리 절감, 오차는 0.0002m/0.014° 수준으로 억제하여 정확도도 유지하였다. 본 논문은 다양한 실시간 XR 인식 작업을 하나의 하드웨어 구조로 통합 처리할 수 있는 실용적 DNN SoC를 구현하였다는 점에서 높은실용성과 확장 가능성을 지닌다.

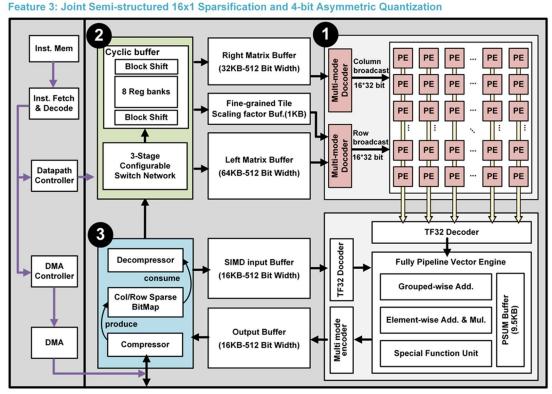

#11-6 본 논문은 칭화대학교에서 발표한 것으로, 대규모 언어 모델(LLM)의 로컬 파인튜 닝을 위한 고효율 전용 프로세서 구조를 제안한다. 최근 QLoRA, QA-LoRA와 같은 Parameter-Efficient Fine-Tuning(PEFT) 기법이 부상하면서, 메모리 제약이 있는 AI PC 환경에서도 LLM을 미세 조정하려는 수요가 증가하고 있다. 그러나 기존의 신경망 가속기 (NPU)는 비대칭 양자화 연산에 대한 지원이 미비하고, 낮은 정밀도의 데이터 전치 (transposition) 및 외부 메모리 접근 비용이 크다는 문제를 안고 있다.

Feature 1: 16\*16 Asymmetric Format Computing Optimized Reconfig. Systolic Array with Multi-mode Decoder Feature 2: 3-stage Configurable Switch Network with Cyclic buffer for 4/8/16b Transposition

[그림 3] 본 논문에서 제안하는 fine-tuning 과정

이를 해결하기 위해 본 논문은 QLoRA 연산 흐름을 분석한 뒤, 세 가지 핵심 기술을 기반으로 한 전용 파인튜닝 프로세서를 설계하였다. 첫째, 제안된 텐서 어레이는 비대칭 양자화 연산에 최적화된 구조로, 4비트 곱셈기와 5비트 누산기를 기반으로 다양한 연산 모

드(BF16×INT4, FP9×FP16 등)를 지원하는 재구성 가능한 연산 소자(PE)를 포함한다. 이를 통해 높은 연산 효율과 유연성을 동시에 확보하였다. 둘째, 다중 형식 지원 전치 엔진은 3단계 스위칭 네트워크와 순환 버퍼(cyclic buffer)를 활용하여 4/8/16비트 데이터에 대한 전치 연산을 효율적으로 수행하며, 기존 GPU 대비 8배 높은 어레이 활용도를 달성한다. 셋째, 반구조화 sparsity 기반의 압축 기법을 적용하여, QLoRA의 INT4 가중치 및 BF16 어댑터 연산에서 외부 메모리 접근을 최소화하면서도 정확도를 유지할 수 있도록 하였다. 해당 프로세서는 28nm 공정으로 구현되었으며, 3.14 TFLOP/W의 에너지 효율을 기록하였다. LLaMA2-7B 모델에 대해 GPTQ 기반의 QLoRA 파인튜닝을 수행한 결과, 기존 GPU 대비 1.475배 높은 에너지 효율과 8배 향상된 데이터 전치 성능을 보였으며, 누적 오차는 -95dB 수준으로 억제되었다. 본 연구는 LLM의 로컬 파인튜닝이라는 최신 응용에 대응하기 위해 비대칭 양자화, 형식 전치, 압축을 통합 설계한 점에서 큰 의의가 있으며, 향후 AI PC 및 엣지 디바이스에서의 실용적 LLM 적용에 중요한 기여를 할 수 있다.

#### 저자정보

#### 박은빈 박사과정 대학원생

● 소속 : 포항공과대학교

● 연구분야 : 딥러닝 가속기 설계● 이메일 : eunbin@postech.ac.kr

• 홈페이지 : https://sites.google.com/view/epiclab

KAIST 전기및전자공학부 석사과정 박민하

#### **Session 18 Digital Compute-in-Memory**

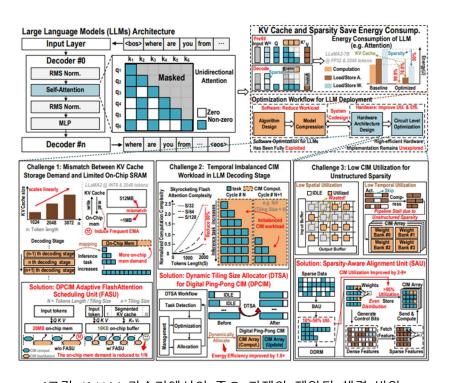

#18-4 본 논문은 중국 Southeast University와 EDA 국가혁신센터가 공동으로 발표한 연구로, FlashAttention 기반 DCIM(Digital Compute-in-Memory) 가속기를 제안한다. 수십억 개의 파라미터와 복잡한 연산을 요구하는 LLM의 추론을 edge 환경에서도 효율적으로 수행하기 위해, 본 구조는 FlashAttention, KV 캐시 최적화, 희소성 정렬(sparsity-aware alignment) 기법을 통합한 DCIM 아키텍처로 설계되었다.

[그림 1] LLM 가속기에서의 주요 과제와 제안된 해결 방안

Fig.1은 제안된 구조가 decoder-only 기반의 LLM 아키텍처임을 보여주며, unidirectional attention 방식이 적용된 다수의 디코더 계층으로 구성되어 있음을 나타낸다. 핵심 연산은 Query/Key/Value 생성을 위한 WEngine, Attention 연산을 위한 AEngine, SAU, DTSA, Post Processing Unit(PPU) 등으로 구성된다.

WEngine은 16개의 1Kb 디지털 Ping-Pong CIM(DPCIM) 매크로로 구성되어 있으며, 8-bit 가중치와 2-bit 활성화 간 병렬 곱셈 연산을 수행한다. DPCIM은 연산과 가중치 업데이트를 병행하며, 근사화와 오차 보상 기법을 통해 에너지 및 면적 효율을 높인다. AEngine은 FlashAttention 방식에 따라 QKT, PV 연산을 처리하며, KV 캐시는 on-chip에 저장된다.

또한 FASU는 이전 스테이지의 K/V를 재사용하고, Q만 계산에 포함함으로써 연산량을 줄이며, 타일링 및 세그먼트화된 KV 캐시 구조는 DRAM 접근을 93.8%까지 줄이고 on-chip 메모리 사용량도 크게 감소시킨다. 전체적으로 기존 FlashAttention 대비 최대 3.1×속도 향상을 달성하였다.

비정형 희소성에 대응하기 위한 SAU 구조는 최대 87.5% sparsity를 지원하며, prefix popcount 기반의 정렬 방식과 weight-stationary 구조를 통해 3.2× 처리량 개선을 이끌었다. 28nm 칩 측정 결과, 최대 52.03 TOPS/W의 연산 효율과 기존 SOTA 대비 최대 2.54× 에너지 효율을 달성했다.

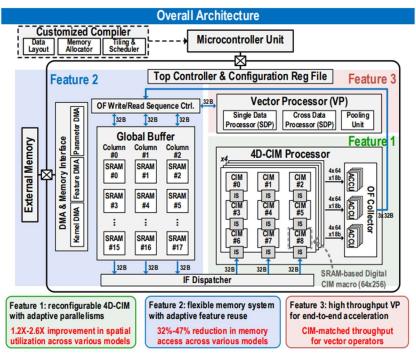

#18-5 본 논문은 CNN과 Transformer 모델을 모두 고효율로 가속할 수 있는 22nm 공정기반 CIM-utilization-aware 가속기를 제안한다. 다양한 연산 차원과 접근 패턴을 갖는 최신 네트워크 모델을 위해, 재구성 가능한 4D-CIM 구조, 유연한 feature reuse 메모리 시스템, 고속 벡터 프로세서 등을 결합하였다.

[그림 1] 제안된 재구성 가능한 가속기의 전체 아키텍처

Fig. 1는 전체 아키텍처를 보여주며, 본 구조가 4D-CIM 프로세서, 글로벌 버퍼, SIMD 벡터 프로세서, DMA 모듈, 설정 레지스터 등으로 구성되어 있음을 나타낸다. 4개의 CIM 코어는 각각 9개의 64×256 SRAM 기반 CIM 매크로를 포함하고 있으며, H-tree 기반 네트워크를 통해 동적으로 병렬도를 조절할 수 있다. 입력과 출력 feature는 dispatcher와 collector를 통해 관리되며, SIMD 벡터 프로세서는 Softmax, LayerNorm, Pooling 등 다양한 연산을 수행한다.

본 구조는 다양한 연산자에 맞춰 병렬도를 적응적으로 조절할 수 있어, ResNet-50과 BERT-base에서 기존 고정형 구조 대비 각각 2.6배, 1.5배의 CIM 활용률 향상을 달성하였다. 또한 feature reuse를 위한 유연한 메모리 계층 설계로 VGG-16과 BERT-base에서 최대 47%의 메모리 접근 감소 효과를 보였다. Softmax 및 LayerNorm 같은 연산에서는 online 알고리즘 기반의 벡터 프로세서를 적용하여 지연 시간은 59%, 메모리 접근은 33% 줄였다.

최종적으로 22nm에서 구현된 본 칩은 VGG-16 기준 최대 29.3TOPS/W, BERT-base 기준 25.4TOPS/W의 에너지 효율을 달성하였으며, CNN과 Transformer 모두를 고효율로 가속할 수 있는 최초의 범용 CIM 기반 구조로 평가된다.

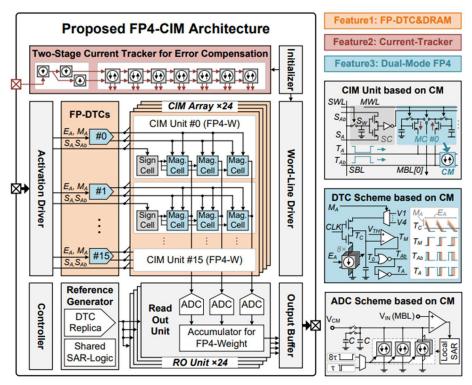

#18-6 본 논문은 Edge 환경에서 대규모 언어 모델(LLM)의 효율적인 추론을 가능하게 하기 위해, FP4 기반의 One-Shot Compute-in-Memory(CIM) 매크로를 제안한다. 최근 LLM의 복잡성과 매개변수 수가 급격히 증가함에 따라, 클라우드에서 에지로의 실행 전환이요구되고 있으나, 에지 디바이스는 제한된 전력과 저장 용량으로 인해 고정밀 연산을 감당하기 어렵다. FP4는 INT8 대비 더 나은 정확도를 제공하면서도 절반의 저장 공간만 요구하여, LLM 추론을 위한 유망한 저정밀 포맷으로 주목받고 있다.

이 논문에서 제안하는 아키텍처는 입력값을 시간 신호로 변환하는 FP-DTC, 곱셈 누산을 수행하는 CIM array, 아날로그 출력을 디지털로 변환하는 Read-out 유닛, PVT 및 mismatch 보정을 위한 2단계 Current Tracker(CT), 그리고 입출력 스케줄링을 담당하는 제어 로직 블록으로 구성된다. 특히 CIM array는 부호 셀과 크기 셀로 구성된 전류 기반 아날로그 구조로, one-shot 방식의 FP MAC 연산을 수행하며, 이 구조는 이후 소개될 세가지 핵심 기술의 기반이 된다. 전체 구성은 Fig. 2에 나타나 있다.

[그림 1] 제안된 FP4-CIM 매크로의 전체 아키텍처

기존 FP-CIM은 주로 FP16/FP32 포맷에 최적화되어 있어 FP4 연산에 비효율적이며, pre-alignment에 의한 전력 소모, 아날로그 회로의 PVT 및 mismatch 민감성, LLM 계층 별 hybrid-FP4 처리가 어려운 문제가 있다.

이를 해결하기 위해 본 논문은 세 가지 핵심 기술을 통합하여 설계된 아키텍처를 제안한다. 먼저, 입력값과 가중치를 아날로그로 변환해 곧바로 곱셈-누산(MAC) 연산을 수행하는 One-Shot FP-MAC 구조를 도입하였다. 이 구조에서는 FP-DTC가 디지털 FP4 입력을시간 신호로 변환하고, 변환된 신호는 24개의 CIM array로 전달되어 eDRAM 기반 전류연산을 거친다. 연산 결과는 Read-out 유닛을 통해 디지털로 변환된 후 병합되며, 전체연산 경로의 전류 일관성은 CT 회로를 통해 보정된다.

또한, \*\*전류 기반 연산 경로 전반의 PVT 변화 및 디바이스 mismatch에 대응하기 위한 2단계 전류 보정 회로(CT)\*\*를 설계하였다. 이 회로는 Current Memory 기반으로 모든 연산 유닛의 전류를 정규화하며, 공급 전압의 ±10% 변동과 −20℃~85℃의 온도 변화에도 MAC 출력의 안정성을 유지한다. 이를 통해 칩 간 편차는 1LSB 이하로 억제된다.

마지막으로, LLM 계층별 정밀도 요구에 대응할 수 있도록 Dual-mode Hybrid-FP4 MAC 구조를 채택하였다. 제안된 구조는 E2M1과 E1M2 포맷을 모두 지원하며, FP-DTC와 FP-DRAM의 간단한 설정 변경만으로 포맷 전환이 가능하다. 이를 통해 다양한 정밀도 요구

에 유연하게 대응하면서도 양자화 오차를 최소화할 수 있다.

28nm CMOS 공정에서 구현된 본 매크로는 0.012mm²의 면적, 0.8~1.0V 구동 전압에서 동작하며, 최대 581.8 TFLOPS/W 및 9.1 TFLOPS/mm²의 에너지·면적 효율을 기록하였다. 기존 INT8-CIM 대비 최대 5.2배 더 높은 에너지 효율과 2.2배의 면적 효율, 그리고 더우수한 LLM 추론 정확도를 달성하였다.

따라서 본 논문은 one-shot 연산, 전류 기반 보정, hybrid-FP4 지원이라는 세 가지 기술을 통합함으로써, 에지 LLM 추론을 위한 고효율·고정밀·고신뢰 하드웨어 솔루션을 제시한다.

#### 저자정보

#### 박민하 석사과정 대학원생

● 소속 : KAIST

● 연구분야 : 디지털 회로 설계 ● 이메일 : mhpark@ics.kaist.ac.kr

● 홈페이지: https://idec.or.k

KAIST 전기및전자공학부 석사과정 권재훈

#### Session 37 Machine Learning and Energy Efficient SoCs

이번 2025 IEEE CICC의 Session 37은 Machine Learning and Energy Efficient SoCs라는 주 제로 총 8편의 논문이 발표되었다. 이 세션에서는 고성능 신호 처리 및 효율적인 메모리 활용을 통해 inference throughput과 energy efficiency를 극대화하는 데 중점을 두었다.

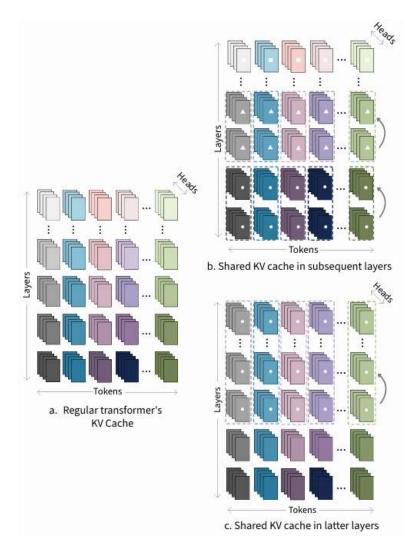

#37-1 본 논문은 UC San Diego와 NVIDIA의 공동 연구로, Key-Value (KV) cache compression에 대한 분석과 implementation strategy를 다룬 논문이다. 최근 Large language models (LLMs)에서 긴 context를 효율적으로 처리하는 것이 점점 더 중요해짐에 따라, KV cache의 저장 및 연산 효율을 개선하기 위한 다양한 방법들이 제안되어 왔다. 본 연구에서는 KV cache compression method를 layer, head, token, hidden dimension 이라는 4개의 category로 분류하고, 각각의 method들이 inference latency와 model 정확도에 미치는 영향을 평가하였다. 특히 본 논문에서는 post-training과 training-free 방식모두를 포함하며, 실제 LLM benchmark를 통해 compression 기법 간 trade-off를 정량적으로 비교하고자 하였다. 실험 결과, YOCO 기반 cross-layer compression 기법으로 latency를 최대 2.87배 가속할 수 있었으며, CPC 및 LongLLMLingua 같은 training-free token compression 기법은 end-to-end inference를 최대 10.93배 까지 단축함으로써, long-context scenarios에서 GPU memory footprint를 획기적으로 절감하고 inference throughput을 개선할 수 있음을 확인했다.

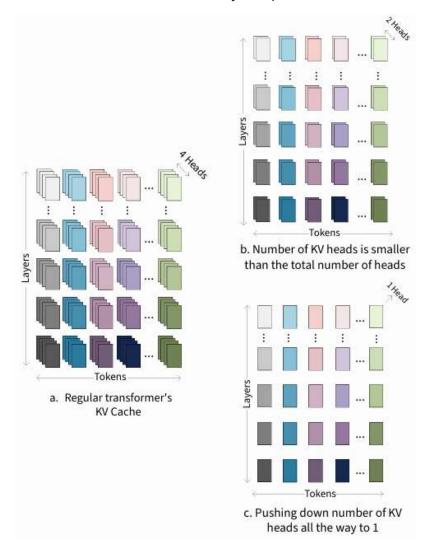

[그림 1] Cross-Layer Attention이 적용된 KV Cache

[그림 1]은 Cross-Layer Attention을 통해 KV cache를 layer 간에 공유하는 세 가지 방식을 보여준다. regular transformer는 각 layer가 독립적으로 KV cache를 저장하고, subsequent layers 방식은 첫 layer의 key-value를 이후 모든 layer에서 재사용하며, latter layers 방식은 decoder 후반 layer에만 공유 범위를 제한해 메모리와 연산을 줄이면서 성능 저하를 최소화한다. 본 논문의 contribution을 구체적으로 정리하면 다음과 같다. 일단 Layer dimension에서는 Cross-Layer Attention을 통해 KV cache를 공유하는데, subsequent layers sharing 방식과 latter layers sharing 방식을 도입하여 redundant storage와 compute overhead를 줄였다. 다음으로 dimension에서는 Multi-Query Attention을 통해 모든 head에 하나의 key/value를 공유하거나, Grouped-Query Attention을 통해 head를 그룹별로 묶어서 key/value 수를 줄임으로써 메모리 사용량을 감소시켰다. 그리고 Token dimension에서는 Compressed Past Context (CPC)와 LongLLMLingua를 활용하여 유사도가 낮은 과거 Token 의 KV entry를 pruning하거나 summarization하여 Token 수를 크게 축소함으로써 end-to-end inference latency를 단축하였다. 마지막으로 Hidden Dimension에

서는 low-rank factorization과 8-bit quantization 기반의 압축 기법을 적용해 KV representation의 차원을 축소하고 GPU memory footprint를 효과적으로 낮추었다.

[그림 2] Head Dimension에서의 KV Cache Compression (Multi-Query & Grouped-Query Attention)

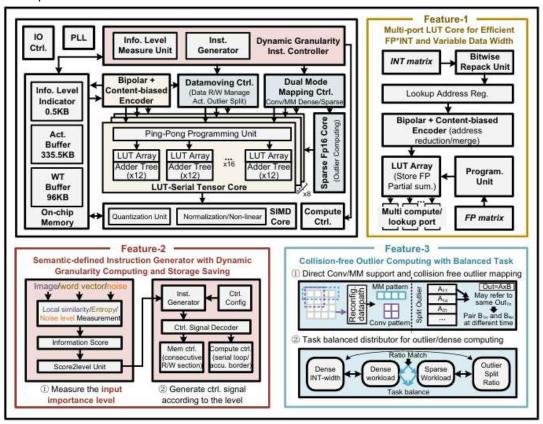

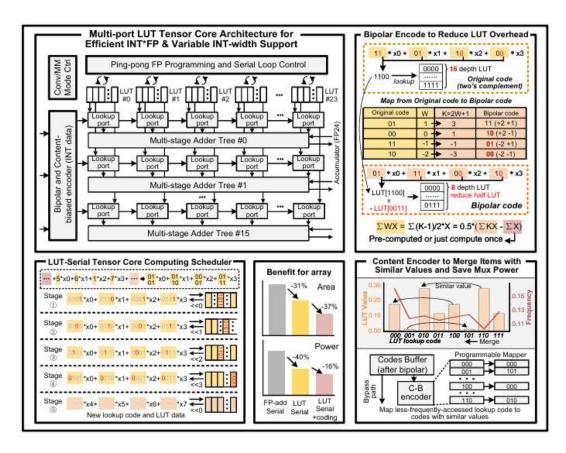

#37-4 본 논문은 Tsinghua University에서 발표한 연구로, 비디오 생성을 위한 Content Creation Engine (CCE)의 회로 구현 및 최적화를 다룬다. 최근 diffusion model, transformer, super-resolution (SR) model과 같은 대규모 생성 모델들이 고화질 동영상 생성에 활용됨에 따라, 이를 효율적으로 가속할 수 있는 저전력, 고성능 하드웨어 설계가 요구되고 있다. 본 연구에서는 asymmetric INT\*FP 연산을 지원하는 LUT-based tensor core와 semantic-driven instruction generator, collision-free outlier mapper를 통합한 구조를 제안하여, heterogeneous 연산 특성을 통합적으로 처리할 수 있는 아키텍처를 구현하였다. 특히 LUT-serial core는 bipolar-content encoding 및 multi-port 구조를 통해 power 와 area overhead를 최소화하였으며, input redundancy 제거를 위한 information-level

scoring과 granularity control을 통해 연산 효율을 극대화하였다. 실험 결과, diffusion task 에서 3.58배, SR에서 2배, transformer에서는 12%의 평균 energy efficiency 향상시켰고, inference power는 최대 87.6%까지 감소되었다.

[그림 3] Head Dimension에서의 KV Cache Compression (Multi-Query & Grouped-Query Attention)

본 논문의 contribution을 구체적으로 정리하면 다음과 같다. 먼저 bipolar-content encoding 및 multi-port LUT-serial tensor core 기반의 FP\*INT computing cell을 도입하여, 입력 feature를 ±1 bit로 표현함으로써 accumulation 연산을 XNOR 및 popcount 연산으로 대체하고, multi-port LUT-serial tensor core 구조를 통해 하나의 LUT에서 여러 input stream을 serial processing하도록 설계하여, 기존 FP MAC와 비교했을 때 area 및 power 절감을 동시에 달성하였다. 또한 semantic-defined instruction generator를 도입하여, 모델레벨에서 feature map의 channel 중요도를 semantic score로 계산한 뒤 낮은 점수의 채널 블록을 pruning하고, 남은 블록에 대해 dynamic granularity control을 적용하여 연산분해 수준을 조정함으로써 instruction issue 시점에 필요한 compute와 on-chip storage를 최소화하며, 16-entry deep FIFO와 4-stage pipelined control path로 매 사이클 최적화된 명령어 스트림을 연속 발행할 수 있도록 설계하였다. 그리고 Collision-free Sparse Mapper 기반의 unified dense/outlier architecture를 제안하여, input feature의 non-zero sparsity 정보를 사전 분석해 8-bank interleaved on-chip SRAM의 write 주소를 remapping함으로써 dense core와 outlier core 간 memory bank write 충돌을 방지했다.

마지막으로 Diffusion, Super-Resolution, Transformer 워크로드별로 compute와 memory 요구 특성을 분석하여 adaptive resource allocation 기반의 balanced scheduling 알고리즘을 제안하고, 여기에 dynamic voltage and frequency scaling (DVFS)를 결합하여 각 task의 critical path에 맞춰 전압, 주파수를 실시간 조정함으로써 energy efficiency 개선과 높은 throughput을 구현하였다.

[그림 4] bipolar-content encoder를 활용한 Multi-port LUT-serial core

### 저자정보

### 권재훈 석사과정 대학원생

● 소속: KAIST 전기및전자공학부

• 연구분야 : Digital Circuit Design, ECC Hardware Design

이메일 : jhkwon@ics.kaist.ac.kr홈페이지 : https://ics.kaist.ac.kr/

KAIST 인공지능반도체대학원 석사과정 윤지원

### Session 37 Machine Learning and Energy Efficient SoCs

이번 2025 IEEE CICC Session 37은 Machine Learning and Energy Efficient SoC라는 주제로 총 8개의 논문이 발표되었다. 이 Section은 인공지능 연산의 고도화와 함께, 엣지 디바이스 및 임베디드 시스템에서의 전력 효율성과 연산 성능 간의 균형을 달성하기 위한다양한 하드웨어 최적화 연구를 중심으로 소개되었다.

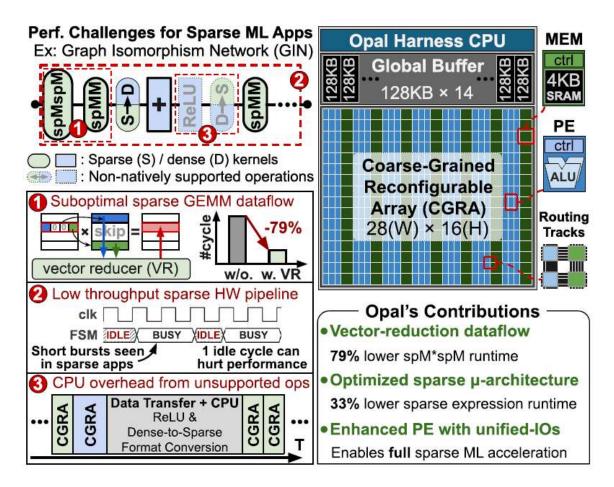

#37-8 본 논문은 스탠포드 대학교에서 발표한 내용으로, Gustavson dataflow와 통합 PE(Processing Element)를 이용하여 sparse와 dense 연산 모두를 효율적으로 처리할 수 있는 Opal을 제안한다. 최근 ML 모델은 정확도를 높이기 위하여 연산량과 자원 소모가 크게 증가하고 있다. 이에 입력과 가중치에 Sparse 연산을 도입함으로써 이러한 비용을 줄이고자 하였으나 기존 Sparse Accelerator는 특정 모델에 종속되며, CGRA (Coarse-Grained Reconfigurable Array)는 dense 연산에 최적화되어 있어 sparse 연산에서 성능 저하가 발생하는 문제가 있었다.

본 논문에서 제안하는 Opal은 sparse ML 연산을 위해 특화된 CGRA SoC로 sparse, dense 연산을 함께 가속할 수 있는 유연성을 가지며 그림 2에서 제시된 바와 같이 다음의 세 가지를 주요 기여로 제안한다. 첫 번째, vector reducer primitive를 도입해 Gustavson dataflow를 지원하여, sparse matrix multiplication에서도 최대 79% runtime감소를 보였다. 두 번째, Coordinate Dropper, Repeater, Level Scanner, Level Writer 등에서 발생하는 주요 Pipeline Bubble을 제거해 최대 33%의 성능 향상을 달성했다. 셋째, 통합형 PE구조를 통해 RELU, SoftMax와 같은 비선형 연산 및 dense와 sparse 사이 데이터 변환을 CPU 호출 없이 직접 수행 가능하게 하여 최대 89%의 실행 시간 단축 효과를 얻었다.

이러한 구조는 실제 sparse ML 모델인 GCN 과 GIN에도 적용되어 각각 68%, 79%의 runtime과 에너지 소비 감소를 이끌었으며, 주요 8개 sparse 연산 kernel에서도 평균 35%의 실행 시간 단축을 보였다. 결론적으로 Opal은 높은 동작 주파수 (720MHz)와 유연한 연산 지원을 바탕으로, 차세대 sparse ML 가속을 위한 유망한 CGRA 기반 아키텍처로 자리매김한다.

[그림 1] Opal의 SoC아키텍처와 sparse ML 애플리케이션의 성능 문제를 해결하기 위한 본 논문의 기여 내용

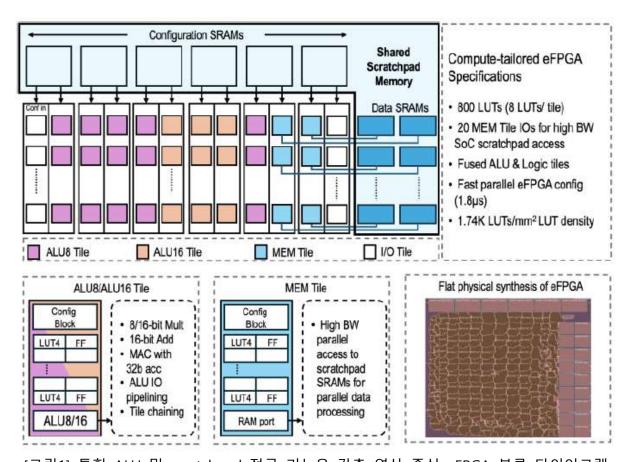

#37-6 본 논문은 카네기 멜론 대학교에서 발표한 내용으로, 다양한 연산 집약적 애플리케이션을 효율적으로 처리할 수 있도록 RISC-V CPU와 고도로 최적화된 eFPGA를 밀접하게 통합한 SoC 아키텍처를 제안한다. 기존의 fixed-function accelerator는 유연성이 부족하고, 범용 eFPGA는 성능과 에너지 효율이 낮은 한계가 있었던 반면, 본 아키텍처는 두 방식의 장점을 통합함으로써 높은 성능과 유연성을 동시에 확보할 수 있도록 하였다. 제안된 SoC는 VexRISC-V CPU와 eFPGA를 CFU (Custom Function Unit) 인터페이스로 연결하고, 비동기 FIFO를 통해 서로 다른 클럭 도메인에서도 안정적인 통신이 가능하도록설계되었다. 또한, eFPGA 내부에 ALU8/ALU16 유닛 (MAC + Adder + Accumulator)을 logic tile에 직접 융합하여, 기존의 LUT구조보다 훨씬 높은 계산 성능과 밀도를 확보하였다. 이러한 구조는 22.3G0PS/mm²의 연산 밀도를 달성하며, ALU chaining과 Pipelining을 통해 260MHz의 고속 동작이 가능하다.

Scratchpad Memory (96KB)는 CPU와 eFPGA 사이에서 고속 병렬 데이터 공유를 가능하게 하며, DMA (Direct Memory Access) 와 CFU Manager를 통해 bitstream 전송 및 제어

가 자동화되도록 설계되었다 특히 scratchpad를 통해 eFPGA 전체를 병렬로 구성함으로 써  $1.8\mu s$  이내의 초고속 재구성이 가능하며, 이는 문헌상 최단 시간으로 초당 1000회까지 애플리케이션 전환이 가능하다.

실제 구현된 애플리케이션 성능 측정 결과, NTT(Number Theoretic Transform) — 256은 CPU 대비 29배의 처리량, 66배의 에너지 효율, FFT(Fast Fourier Transform) — 64는 각각 108배, 228배 향상을 기록하였다. FIR 필터와 CRC32 또한 RISC-V기반 소프트웨어 구현 대비 높은 성능을 보였다.

마지막으로 본 연구는 기존 상용 및 학계의 eFPGA SoC들과 비교해, 에너지 효율 (747.83 GOPS/W for INT8), 연산 밀도(22.3 GOPS/mm²), 재구성 속도 (1.8μs) 측면에서 모두 최고 수준의 결과를 달성하였으며, 이는 다양한 엣지 연산 환경에서 실시간 가속기전환 및 높은 처리 성능이 요구되는 응용에 매우 적합함을 입증하였다.

[그림1] 통합 ALU 및 scratchpad 접근 기능을 갖춘 연산 중심 eFPGA 블록 다이어그램

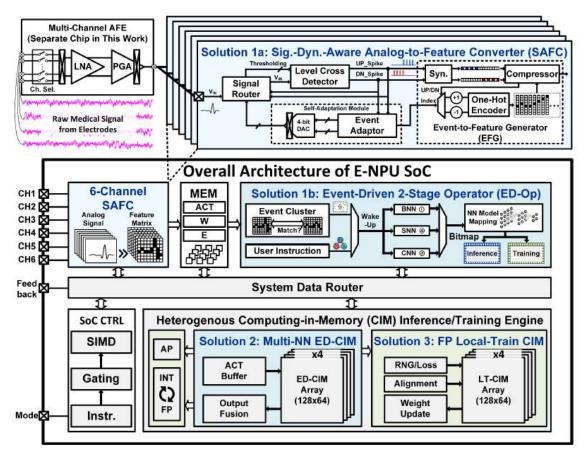

#37-7 본 논문은 칭화대학교에서 발표한 내용으로, 신호 변화에 따라 연산을 수행하고, In-Memory 추론 및 환자 맞춤형 On-Chip 학습을 지원하는 초 저전력 의료 웨어러블용 neural SoC(E-NPU)를 제안한다. 의료 웨어러블 기기는 생체 신호를 장시간 모니터링하고 정확하게 해석해야 하므로 낮은 에너지 소비, 높은 정확도, 사용자 맞춤형 학습이 가능한

연산 구조를 요구한다. 최근에는 BNN, SNN, CNN 등의 경량 신경망과 NAS(Neural Architecture Search) 기반 설계 기법이 발전하고 있지만, 신호 특성에 따라 유연하게 작동하고, 다양한 신경망 모델을 동시에 지원하며, 환자별 특성에 적응할 수 있는 SoC 설계는 여전히 도전 과제로 남아있다.

이를 해결하기 위해 E-NPU는 그림 1과 같이 설계되었으며, 다음 세가지 핵심 기술을 통합하였다. 첫째, SAFC (Signal-Dynamics-Aware Analog-to-Feature Converter) 기반의 동적 신호 처리 아키텍처를 통해 신호 변화가 있을 때만 연산을 수행함으로써, 기존의 항상-활성화 방식 대비 평균 1.7배 이상의 에너지 절감을 달성한다. 둘째, 다양한 정밀도설정이 가능한 다중 모델 In-Memory 연산 (ED-CIM) 구조를 통해 BNN, SNN, CNN을 모두 처리하며, 병렬 Column 구조와 ping-pong SRAM 기반의 파이프라인으로 고속 및 고효율 연산을 지원한다. 셋째, Direct Feedback 기반의 On-chip 학습 엔진 (LT-CIM)을 통해 cross-layer dependency 없이 layer 단위로 병렬 학습을 수행하며 정밀도 변환, 에러 예측, 가중치 업데이트까지 전체 학습 흐름을 칩 내부에서 완결할 수 있다.

E-NPU는 40nm CMOS 공정으로 제작되었으며, 수정된 LeNet 모델 기반 실험에서 추론지연 3.03배 감소, 학습 지연 2.49배 감소, 외부 메모리 접근 3.41배 감소 등의 성능 향상을 보였고, EEG, EMG, ECG 관련 4개 공개 데이터셋에서 ED-Op 기반 처리로 평균 1.7배 이상의 에너지 효율을 보였다. 결론적으로, E-NPU는 신호 변화 기반 연산, 다중 정밀도의 In-Memory 추론, 환자 맞춤형 On-Chip 학습을 하나의 SoC에 통합하여, 개인 의료웨어러블 기기에 최적화된 고성능 및 초저전력 뉴럴 하드웨어 플랫폼을 구현하였다.

[그림 1] 제안된 event-driven neural SoC (e-NPU)의 전체 아키텍처 및 세 가지 기여점

### 저자정보

### 윤지원 석사과정 대학원생

● 소속 : 한국과학기술원 (KAIST)

● 연구분야 : 디지털 회로 설계

• 이메일 : jwyoon@kaist.ac.kr

● 홈페이지: https://ics.kaist.ac.kr

경북대학교 전자전기공학부 박사과정 박승현

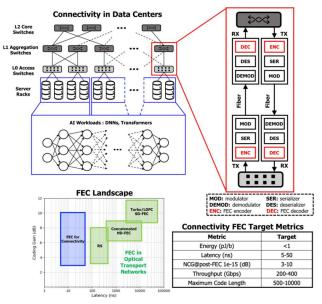

### Session 17 Next-Generation Systems: From Datacenters to the Edge

CICC 2025 세션 17의 논문들은 각기 다른 시스템들의 성능을 저전력 설계 관점에서 창의적으로 향상시키는 방법을 제시한다. 첫 번째 논문은 아날로그 도메인에서 직접 JPEG 압축을 수행해 디지털화 이전의 연산으로 전력 소모를 획기적으로 줄였고, 두 번째 논문은 강화학습 기반 자율주행에 특화된 프로세서를 설계해 실시간 제어와 효율적인 학습을 동시에 가능하게 했다. 세 번째 논문은 데이터센터 고속 통신에 필요한 FEC 조건을 정의하고 이를 만족하는 BCH 디코더를 구현해 고성능과 에너지 효율을 모두 확보했다. 각각의 접근 방식이 문제의 본질을 정확히 짚고 실용적인 해법을 제시하고 있어 인상 깊었다.

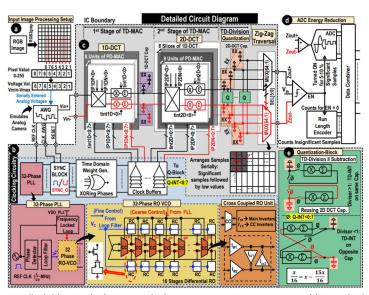

# #17-1 TD-dAJC: A 2pJ/pixel Time-Domain Weight and Integrating-MAC based direct-Analog-to-MJPEG Compression for Video Sensor Nodes

[그림 1] 제안하는 아날로그 기반 MJPEG Compression 회로 다이어그램

본 논문은 초저전력 IoT 영상 센서 노드를 위한 새로운 아날로그 기반 JPEG 압축 구조를 제안한다. 기존의 디지털 카메라 시스템은 영상 데이터를 완전히 디지털화한 후 압축을 수행하는 방식으로, 높은 ADC 전력 소모, 중간 저장소의 면적/전력 부담, 복잡한 연산 과정 등의 문제를 안고 있다. 특히 엣지 디바이스에서는 이러한 전력과 자원의 비효율성이 심각한 제약으로 작용하며, 실시간 처리가 요구되는 상황에서 MJPEG과 같은 압축 방식도 여전히 높은 연산 복잡도와 저장소 부담이 존재한다. 저자는 이러한 문제를

해결하기 위해, DCT 기반의 JPEG 압축을 디지털화 이전 단계, 즉 센서 출력 직후의 아날로그 도메인에서 직접 수행하는 TD-dAJC(Time-Domain direct Analog-to-JPEG Compression) 구조를 고안하였다.

제안된 시스템은 Time-Domain 기반의 Multiply-and-Accumulate(MAC) 연산 및 Division 구조를 활용하여, 영상 데이터를 디지털화 없이 압축 가능하게 한다. DCT 가중치는 시간 펄스로 변환되어 공정/전압/온도(PVT) 변화에 강인하게 동작하며, 기존 SC 방식에서 필요하던 큰 커패시턴스나 버퍼 없이 소형 저전력 구현이 가능하다. 또한, 선택적으로 유의미한 신호에만 ADC를 작동시키는 구조를 통해 ADC 전력 소모를 최소화한다. 구현된 시스템은 4K 12fps 해상도를 지원하며, 기존 디지털 방식 대비 25배, 기존 아날로그 방식대비 13배 향상된 2pJ/pixel의 에너지 효율을 달성하였다. PSNR 30dB 수준의 영상 품질도 확보하였으며, 0.856mm²의 소형 칩 영역 내에 모든 연산을 집적함으로써 초소형 엣지 비전 시스템에 실질적인 활용 가능성을 제시하였다. 본 논문은 아날로그 컴퓨팅과 시간영역 신호 처리를 융합하여, 센서 노드의 전력 병목을 근본적으로 해결할 수 있는 새로운 영상 압축 패러다임을 제시한다는 점에서 큰 의미가 있다.

# #17-2 A 28-nm Real-Time Reinforcement Learning Processor for Mapless Autonomous Navigation with Unified Actor-Critic Network and Inference-on-Request Scheduling

[그림 2] 제안한 강화학습 프로세서의 전체 아키텍처

본 논문은 은 지도 없이 자율 주행을 수행하는 로봇을 위한 실시간 강화학습 전용 프로 세서를 제안한다. 지도 기반의 자율 주행이 어려운 환경에서는 로컬 센서 정보와 목표 위치만을 기반으로 하는 mapless navigation 기술이 요구되며, 이때 강화학습(Deep Reinforcement Learning, DRL)은 환경 적응력 측면에서 효과적인 접근법이다. 그러나 실제

로봇에 DRL 알고리즘을 적용하는 데에는 연산량, 외부 메모리 접근, 에너지 소모 등의 문제가 존재한다. 본 논문은 이러한 문제를 해결하기 위해, DRL 알고리즘 중 Distributional RL(D4PG)를 지원하며, 학습과 추론을 효율적으로 통합 수행할 수 있는 전 용 하드웨어를 설계하였다.

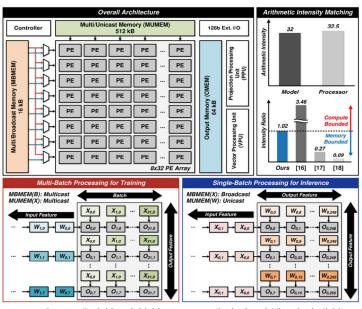

제안된 프로세서는 Actor-Critic 네트워크를 통합한 구조, Inference-on-Request 스케줄링, 배치 크기 적응형 데이터 흐름, Zero-skipping 기반 범주 투사(Categorical Projection) 등을 통해 최적화되어 있다. Actor와 Critic의 구조적 유사성을 활용하여 대부분의 신경망계층을 공유함으로써 연산량과 EMA를 약 85% 줄였으며, 실시간 제어를 위해 inference는 센서 입력 시마다 요청되고, training은 백그라운드에서 유휴 시간에 수행되는 구조로설계되었다. 이 Inference-on-Request 스케줄링은 하드웨어 유휴 시간을 최소화하고, 필요한 동작 주파수를 86.4%까지 낮추는 데 기여한다. 8×32 PE 배열 기반의 연산 구조는네트워크와 아키텍처 간 산술 강도를 일치시켜 병목 없이 연산을 수행하며, 실제 로봇에적용하여 지도 없이 장애물을 회피하며 주행하는 데 성공하였다. 28nm 공정으로 제작된 집은 2.68mW의 저전력으로 동작하며, 이는 이전 강화학습 전용 프로세서 대비 최고 수준의 PE 활용도(71%)와 EMA 절감 효과(84.1%)를 달성하였다. 본 논문은 실시간 자율 주행을 위한 에너지 효율적이며 학습까지 가능한 강화학습 프로세서의 새로운 기준을 제시한 논문이라 할 수 있다.

### #17-3 Forward Error Correction Requirements for Data Center Connectivity

[그림 3] 데이터 센터 연결을 위한 FEC 시스템

이 논문은 차세대 AI 모델 학습을 위한 데이터센터 간 고속 연결에서 요구되는 FEC(Forward Error Correction) 조건을 체계적으로 분석하고, 이에 적합한 설계로 16nm FinFET 공정 기반의 BCH(255,207) 디코더를 구현한 연구이다. 최근 데이터센터는 수천 개의 GPU가 동시에 협업하여 학습을 수행하는 대규모 분산 플랫폼으로 진화하고 있으며, 이러한 시스템에서는 높은 데이터 전송률, 낮은 지연 시간, 그리고 에너지 효율적인 통신인프라가 필수적이다. FEC는 아날로그 프론트엔드의 SNR 요구를 완화시켜 수백 Gbps급전송 속도를 가능하게 하는 핵심 기술로 자리잡고 있지만, 데이터센터 연결을 위한 정확한 FEC 요구 조건은 충분히 규명되지 않았다. 이 논문은 이를 해결하기 위해 1) FEC 설계 사양 정의, 2) BCH 코드의 우수성에 대한 가설 제시, 3) 실제 BCH 디코더 설계를 통한 검증을 수행하였다.

제안된 BCH(255,207,6) 디코더는 0.29 pJ/b의 에너지 효율, 14.4ns의 짧은 지연 시간, 30.8 Gbps의 처리 속도, 그리고 1.04 GHz에서 동작 가능한 고성능 디코더로, 데이터센터 단거리(<100m) 광링크에 필요한 3~10dB의 코딩 게인, sub-50ns 지연, sub-pJ/b 에너지 요구조건을 모두 만족한다. 설계는 RiBM 기반 Berlekamp-Massey 알고리즘을 활용하여 복잡도를 낮췄고, odd iteration을 생략함으로써 사이클 수를 46% 절감했다. 또한 51개의 병렬 처리 엔진을 활용해 고속 처리를 가능하게 하였으며, 에러 탐지와 성능 검증을 위한내장 테스트 회로도 포함하였다. 결과적으로 본 디코더는 LDPC나 Polar, GRAND 기반 구조보다 훨씬 높은 영역 효율(1922 Gbps/mm²)과 지속적이고 일정한 처리 시간을 제공하며, 데이터센터 환경에서 FEC의 기준점으로서 매우 적합한 설계임을 입증하였다. 이 연구는 고속 네트워크에서의 FEC 설계가 단순히 부가 기능이 아닌 핵심 인프라의 성능을 결정짓는 요소임을 강조한다는 점에서 높은 의의가 있다.

### 저자정보

### 박승현 박사과정 대학원생

● 소속 : 경북대학교

● 연구분야 : 딥러닝 가속기 설계● 이메일 : ijjh0435@gmail.com

• 홈페이지 : https://ai-soc.github.io/

포항공과대학교 반도체대학원 박사과정 박은빈

# Session 28 Next-Generation Systems: Hardware for Quantum and Secure Computing

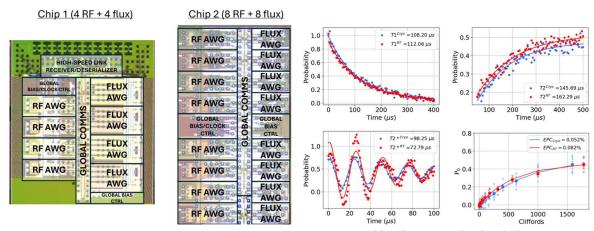

이번 CICC 2025의 Session 28에서는 양자 컴퓨팅과 보안 컴퓨팅을 위한 차세대 시스템 아키텍처를 주제로 총 4편의 논문이 발표되었다. 이 세션은 물리적 복제 방지(PUF), 측면 채널 공격(SCA) 방지 회로, 보안 해시 가속기, 그리고 초전도 논리 회로 등 다양한 보안 및 양자 하드웨어 기술을 다루며, 고신뢰성, 고속 연산, 회로 규모 효율을 동시에 달성하려는 최신 연구 흐름을 반영하였다

#28-1 본 논문은 UC 버클리와 Google Quantum AI 팀이 공동으로 발표한 것으로, 초전도 큐비트 제어를 위한 Cryo-CMOS 기반 다채널 제어 및 측정 회로를 제안한다. 기존 양자 컴퓨터는 수천 개의 큐비트를 제어하기 위해 다수의 고성능 AWG와 ADC 장비를 사용해야 하며, 이는 상온 장비에서 저온 냉각 시스템까지의 케이블 연결에 따른 복잡한 인터페이스, 전력 소모, 지연 문제를 초래한다.

[그림 1] 제안된 RF-AWG two multi-channel 칩 및 qubit 측정 결과

이를 해결하기 위해 본 논문은 1.6K에서 동작 가능한 CMOS 기반 양자 제어 칩을 설계하고, cryogenic 환경에서 동작하는 다채널 송수신 회로를 집적화하였다. 주요 기술로는 다음이 있다. 첫째, 4채널, 1GS/s waveform generator는 9비트 분해능의 비동기 델타-시그마 DAC 구조를 채택하여 고주파 신호 생성 시 low-power 및 low-area를 동시에 만족시킨다. 둘째, 3채널 측정 프론트엔드 회로는 1.2GS/s의 샘플링 속도를 가지는 low-noise ADC와 연동되며, in-phase/quadrature 신호를 안정적으로 분리·측정하는 데 최적화되어

있다. 셋째, 스위치 매트릭스와 on-chip biasing 회로를 통해 여러 큐비트를 선택적으로 제어·측정할 수 있는 확장성을 갖춘 구조를 제공한다.

이 회로는 GlobalFoundries 22nm FDSOI 공정으로 제작되었으며, 총 9.2mm² 면적 내에 전체 회로를 집적하였다. 냉각 환경에서의 실험 결과, 전체 시스템은 15.2mW의 전력으로 안정적으로 동작하였으며, 실제 초전도 큐비트를 사용한 실험에서도 정확한 파형 출력 및 측정 결과 재현이 가능함을 입증하였다.

본 연구는 cryogenic 환경에서 동작하는 제어 회로의 소형화, 저전력화, 고집적화라는 핵심 요구를 만족시키면서, 향후 수천~수만 큐비트 스케일의 양자 시스템 구현을 위한 핵심 하드웨어 플랫폼을 제시한 점에서 중요한 의의를 지닌다.

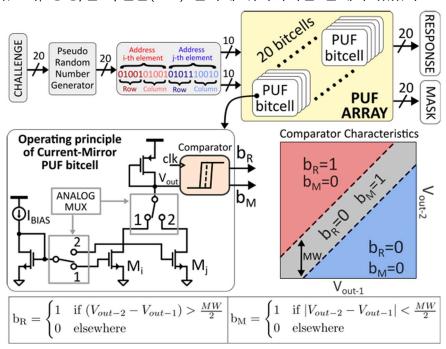

#28-2 본 논문은 KAIST와 삼성전자에서 공동으로 발표한 것으로, 초소형 면적과 높은 엔트로피를 동시에 달성하는 아날로그 기반 PUF(Physical Unclonable Function) 구조를 제안한다. 기존 디지털 PUF는 회로 복잡도 및 낮은 랜덤성으로 인해 보안성과 재현성에서 한계가 있으며, 아날로그 PUF는 민감한 전류/전압 편차를 기반으로 높은 엔트로피를 구현할 수 있으나, 공정/온도/전압(PVT) 변화에 취약하다는 문제가 있었다.

[그림 2] 제안된 Physical Unclonable Function 구조 및 동작원리

이를 해결하기 위해 본 논문은 sub-threshold 전류 미러 기반 아날로그 PUF 셀을 설계하고, 여기에 Bit Masking 및 Digital Post-Processing 기법을 결합하여 환경 변화에 강건한 비트 출력을 생성하였다. 특히, 인접한 셀 간 상대적 전류 크기를 비교하여 비트를 생성하는 구조를 채택해 절대 전류값의 PVT 민감도를 효과적으로 제거하였다. 이 구조는 standard 65nm CMOS 공정 기반에서 구현되었으며, 단일 셀 기준 166 F²/bit의 면적 효

율을 달성하였다.

추가로, 디지털 후처리 회로를 통해 불안정한 비트들을 제거하고, 재현성을 높이기 위한 신뢰도 기반 비트 선택 알고리즘을 적용하여 0.22%의 Bit Error Rate (BER), 49.8%의 평균 Hamming Distance, 0.998의 normalized intra-class similarity를 달성하였다.

본 논문은 아날로그 회로의 고유 전류 편차 특성을 활용하면서도, 디지털 보정 기법을 통해 환경 변화에 강인하고 신뢰성 높은 PUF를 초소형 면적으로 구현한 사례로, 차세대 IoT 및 보안 인증용 칩에서 요구되는 경량, 고엔트로피, 고재현성 PUF 설계의 현실적인 대안을 제시한다.

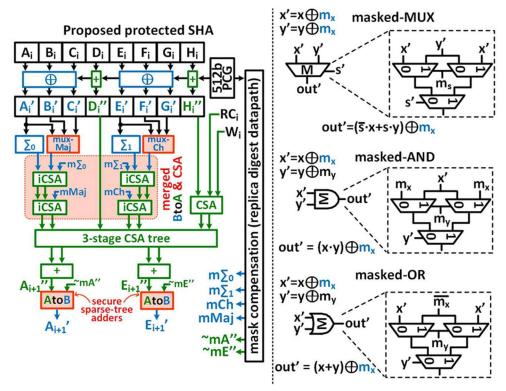

#28-3 본 논문은 인텔에서 발표한 것으로, 측면 채널 공격(SCA)에 강인한 마스킹 기반 HMAC-SHA256 해시 가속기를 제안한다. 기존 해시 연산 하드웨어는 고속성과 에너지 효율에는 강점을 가지지만, 물리적 프로빙이나 전력 분석을 통한 측면 채널 공격에 매우취약한 단점을 지닌다. 이를 해결하기 위해, 본 연구는 masking을 하드웨어 수준에서 정교하게 통합한 SHA256 연산 구조를 설계하고 실제 실리콘 수준에서의 공격 내성까지 입증하였다.

[그림 1] 제안된 SCA-resistant SHA-2 digest datapath 방식

제안된 가속기는 Intel 4 공정을 기반으로 하며, 총 3단계의 masking 기술을 채택한다. 첫째, Boolean-to-Arithmetic 변환기(BA-Converters)를 활용해 논리 연산 기반 회로에 산술 마스킹을 적용함으로써 연산 중간 단계의 정보 노출을 차단한다. 둘째, sparse-tree 기반의 Adder 구조를 채택하여 마스킹 값의 확산을 최소화하고, 물리적 프로빙에 의한 차

동 분석(DPA)에 강인한 구조를 형성한다. 셋째, 각 단계마다 난수 마스크를 실시간으로 재생성하여 고정 마스크로 인한 공격 가능성을 제거하였다.

실험 결과, 해당 가속기는 1.7Gbps의 처리 속도와 6.1pJ/bit의 에너지 효율을 달성하며, 성능 저하 없이 마스킹을 적용한 구조임에도 불구하고 비마스킹 가속기 대비 약 73배 이상의 SCA 저항성을 실측 기반으로 입증하였다. 이는 TVLA(Test Vector Leakage Assessment) 기준을 모두 통과하였으며, 실제 프로빙 장비를 이용한 고전압 EM 분석에 서도 정보 누출이 관찰되지 않았다.

본 연구는 HMAC-SHA256이라는 널리 사용되는 보안 알고리즘에 대해 ASIC 수준에서의 정량적 SCA 저항성 확보를 실현했다는 점에서, IoT 및 엣지 컴퓨팅 기기에서 요구되는 경량, 고신뢰 보안 하드웨어 설계의 실용적 이정표를 제시한다.

### 저자정보

# 박은빈 박사과정 대학원생

● 소속 : 포항공과대학교

● 연구분야 : 딥러닝 가속기 설계● 이메일 : eunbin@postech.ac.kr

• 홈페이지 : https://sites.google.com/view/epiclab

KAIST 전기및전자공학부 박사과정 엄소연

### Session 33 Advancing System Designs with Chiplet Technology

이번 2025 CICC의 Session 33은 "Advancing System Designs with Chiplet Technology"라는 주제로 총 5편의 논문이 발표되었다. 본 세션에서는 칩렛 기반 시스템의 효율성과 확장성을 개선하기 위한 다양한 접근들이 소개되었으며, 각 논문은 테스트 비용 절감, 비정형데이터 흐름 최적화, 동적 디스패칭 구조, 고속 시리얼링크 설계, AI 추론을 위한 레이턴시-에너지 트레이드오프 등 시스템 수준의 문제 해결을 지향한다. 이 후기를 통해 각 논문을 간단히 정리하고자 한다.

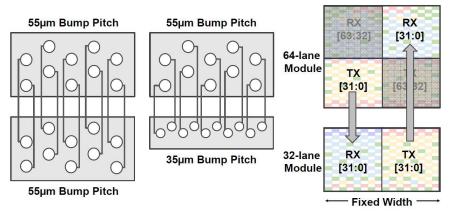

#33-1은 TSMC에서 발표한 논문으로, 차세대 칩렛 간 상호 운용성과 대역폭 밀도를 제공하는 UCle (Universal Chiplet Interconnect Express) 표준에 기반한 인터페이스 설계를 다룬다. 본 논문은 다양한 패키징 기술 및 동작 속도 조건 하에서 UCle 규격을 만족하는 인터페이스를 효율적으로 구현하기 위한 네 가지 핵심 설계 관점을 중심으로 구성된다. 첫째, 송수신 인터페이스 회로 아키텍처 설계에서는 링크의 전력과 성능 간의 균형을 고려한 구성 방식이 제시된다. 둘째, 실리콘 다이 내부에서 PHY 영역 배치를 최적화하고 패키지 경로를 단축하기 위한 floorplanning 전략이 설명된다. 셋째, 패키지 레벨 채널 최적화를 위해 redistribution layer (RDL), interposer 기반 설계, 다중 리피터 삽입 등 다양한 기술의 효과를 비교 분석한다. 넷째, power delivery network(PDN) 분석을 통해 고속 링크 동작 중 발생할 수 있는 전력 노이즈 문제를 해결할 수 있는 설계 방법이 제안된다. 본 논문은 다양한 패키지 기술(CoWoS, InFO, EMIB 등)에 대응하는 최적화된 UCle 설계 전략을 제시하며, 패키지와 실리콘을 아우르는 통합적 설계 접근의 중요성을 강조한다.

[그림 1] #33-1에서 제안한 상호운용성을 위한 UCle 범프 배치 계획

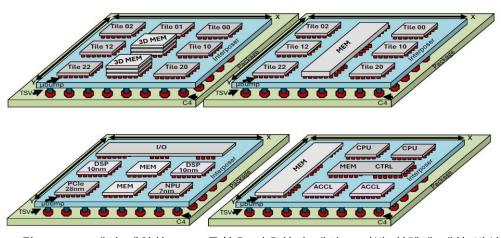

#33-2는 Intel에서 발표한 논문으로, 다이-투-다이(D2D) 통신을 기반으로 한 이기종 칩렛기반 AI/미디어 가속 시스템을 위한 고성능 패시브 베이스 다이 설계를 다룬다. 본 논문은 다양한 프로세스 노드(TSMC, Intel 등)에서 제조된 칩렛들을 통합하는 고성능 시스템을 구현하기 위해, 재구성 가능한 다중 칩렛 구조와 커스터마이즈된 D2D I/O 구조를 제안한다. 특히, 인공지능 및 비디오 인코딩 워크로드에 적합하도록 설계된 이 시스템은, UCle (Universal Chiplet Interconnect Express)와 호환되며 2Gbps/wire 전송 속도, 0.85pJ/bit의 에너지 효율을 달성하였다. 본 논문은 베이스 다이 설계부터 패키징 및 어셈블리 과정까지의 전반적인 플로우를 다루며, 상이한 파운드리 기반의 칩렛 간 통신을위한 전기적 및 물리적 설계 최적화 전략을 소개한다. 이 구조는 향후 새로운 애플리케이션을 위한 top-die 교체에도 유연하게 대응 가능하도록 설계되었으며, 분산형 AI/미디어 가속 시스템에 적합한 확장성과 재사용성을 갖춘 베이스 플랫폼을 제공한다.

[그림 2] #33-2에서 제안한 2.5D 통합을 사용하여 패시브 기반 칩렛에 대한 방식

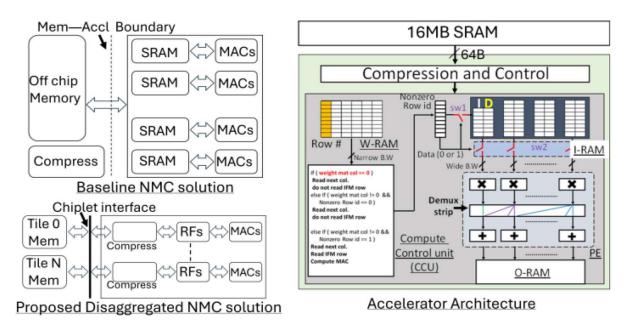

#33-3은 Intel에서 발표한 논문으로, 대형 AI 모델의 Sparse GEMM 연산을 고효율로 가속하기 위해, 16개의 Near Memory Compute(NMC) 칩렛을 기반으로 한 2.5D 이기종 시스템을 제안한다. 각 NMC 칩렛은 16MB SRAM과 INT8 연산을 위한 Sparse GEMM 가속기를 내장하고, 전체 시스템은 총 256MB의 온칩 SRAM과 68 TOPS/W의 효율을 달성한다. 데이터 이동을 최소화하기 위해, 입력 행렬은 압축 포맷(COO/CSC)으로 변환되어 저장되며, MAC과 RF 간 2.048Tbps의 대역폭을 통해 고속 연산이 가능하다. 또한, 각 칩렛간 인터커넥트는 0.8pJ/bit의 에너지로 168Gbps 속도를 지원하며, 메모리-연산의 비율을 1Byte:4096 MACs로 유지한다. 실제 ResNet50 및 Llama3 8B 모델을 기반으로 한 실험에서는 50₩~75%의 sparsity를 활용해 최대 3.82배의 속도 향상과 평균 8배의 throughput 개선을 보였고, 전체 시스템은 Sparse 연산 기준 68 TOPS/W를 실현하였다. 본 구조는 확장 가능성이 높으며, 다양한 sequence length 및 sparsity 조건에서도 성능 저하 없이 유연하게 대응할 수 있는 구조로 설계되었다.

[그림 3] #33-3에서 제안한 데이터 이동 및 연산 감소 기법들을 활용하는 NMC SPGEMM 가속기

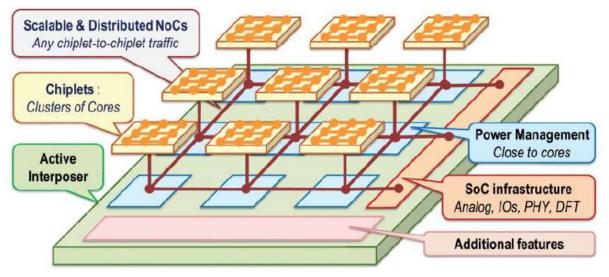

#33-4는 Tsinghua University에서 발표한 논문으로, 3D-IC 및 칩렛 기반 SoC에서 전력 공급의 주요 문제를 해결하기 위해 다양한 전력 변환 회로(LDO, SCVR, Buck DC-DC)를 통합한 전원 아키텍처를 제안한다. 고집적 이기종 통합 환경에서 패키지, 재배선층(RDL), 칩스택 레이어를 통한 전력 분배는 전압 강하, 열 문제, 공급 효율 등 복합적인 제약이 따른다. 본 논문은 이러한 전력 벽(power wall)을 극복하기 위해 세 가지 주요 전원 변환기를 집적하고, 각 방식에 적합한 변환 토폴로지, 제어 방식, 최적화 전략을 함께 분석하였다. 특히 칩렛 기반의 계층적 전력 분배를 위한 scalable integration 기법과 함께, 각 회로의 특성에 따라 효율성과 응답성을 비교하여 실질적인 설계 인사이트를 제공하였다. 제안된 프레임워크는 3D-IC 전력 설계에서 회로-시스템 수준의 통합적 접근을 통해 차세대 고성능 SoC의 에너지 효율 극대화를 위한 방향성을 제시한다.

[그림 4] #33-4에서 제안한 다중 전압 도메인 및 VPD 기능을 갖춘 액티브 인터포저

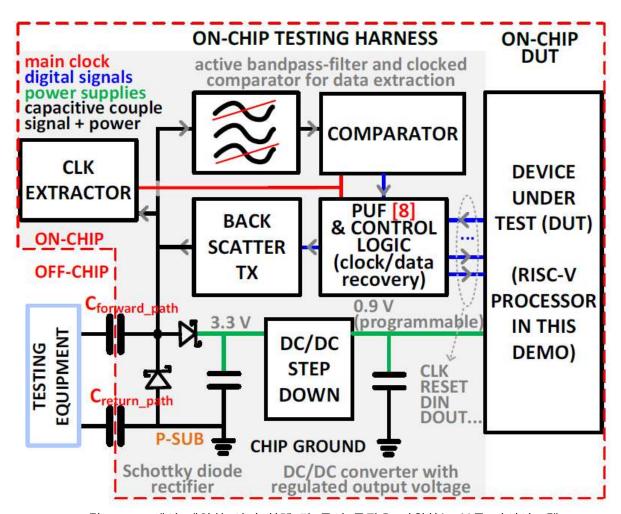

#33-5은 싱가포르국립대학교(NUS)에서 발표한 연구로, 초저가 IoT 칩렛을 위한 완전 무접촉, 위치 불변성 테스트 방법을 제안한다. 기존 칩렛 테스트는 고정밀 프로브 기반이거나 정렬 요구가 있는 비접촉 방식에 의존하여, 단가 대비 테스트 비용이 과도하다는 문제가 있었다. 본 논문에서는 칩렛 전면과 후면 모두에 정전용량(capacitive) 인터페이스를형성하고, 별도 정렬 없이도 동작 가능한 테스트 구조를 구현하였다. 전면 전극은 최상단금속층이나 3D 프린팅으로 형성되며, 후면은 실리콘 기판 자체를 이용한다. ASK 변조 기반 전력 및 데이터 전송, Manchester 인코딩 기반 클럭 동기화를 모두 동일 커패시터 경로에서 수행함으로써 인터페이스를 간소화하였다. 또한 각 칩렛은 PUF 기반 ID를 통해충돌 없이 자신을 식별하고, varactor를 활용한 backscatter 통신을 통해 응답 신호를 송신한다. 제안된 구조는 65nm 공정으로 구현되었으며, 실제 테스트 결과 10mm 이내에서위치에 관계없이 reliable한 통신 및 테스트가 가능함을 보였다.

[그림 5] #33-에서 제안한 여러 칩렛 간 동시 동작을 지원하는 블록 다이어그램

# 저자정보

### 엄소연 박사정 대학원생

● 소속 : KAIST 전기및전자공학부

● 연구분야 : Computing-In-Memory Processor

● 이메일 : soyeon.um@kaist.ac.kr

● 홈페이지 : https://ssl.kaist.ac.kr/

고려대학교 전기전자공학과 박사과정 한창우

### Session 10: Emerging Paradigms for AI, HPC, and Edge Computation

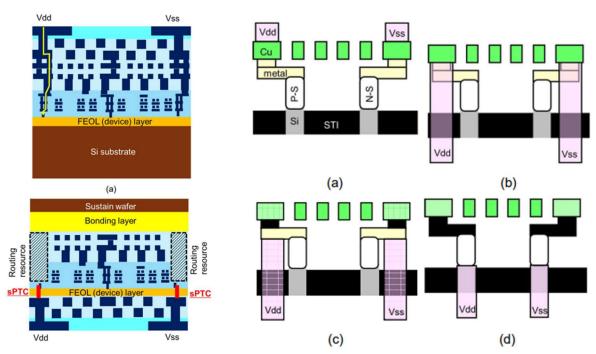

이번 IEEE CICC 2025의 Session 10에서는 AI, 고성능 컴퓨팅(HPC), 엣지 컴퓨팅 등 차세대 컴퓨팅 패러다임을 위한 새로운 회로 설계 기술들을 중심으로 총 6편의 논문이 발표되었다. 본 세션에서는 디지털 및 아날로그 회로, 신소자 기반 구조 등을 통해 연산 효율성과 확장성, 내구성을 동시에 확보하기 위한 다양한 접근법이 제시되었으며, AI 추론 가속기, 최적화 문제 해결 회로, 메모리 기반 연산 구조 등 실용적인 응용 중심의 연구들이 포함되었다. Session 10 중에서도, BSPDN 기반의 전력 공급 회로 설계 및 STT-MRAM 기반 고신뢰성 비휘발성 메모리 설계를 다룬 2편의 논문을 중심으로 살펴보고자 한다.

#10-4 본 논문은 삼성전자에서 발표한 논문으로, 2nm 이후 노드의 SoC 및 HPC 응용을 위해 1세대 Back Side Power Delivery Network (BSPDN)을 적용한 표준 셀 기반 로직 블록의 PPA (성능-전력-면적) 향상 효과를 실리콘 기반으로 실증하였다. 기존 Front Side Power Delivery Network (FSPDN)는 상단 메탈층에서 하단 파워 레일까지 전력을 공급하면서 복잡한 배선 경로와 큰 IR-drop이 발생하였으며, 이로 인해 블록 레벨에서의 성능한계가 존재했다.

이에 비해 BSPDN은 후면에서 전력을 직접 공급하는 구조로 IR-drop을 줄이고, 전면 배선 공간을 확보할 수 있어 로직 블록 성능을 향상시킬 수 있다. 본 논문에서는 특히 초박막 실리콘 기판과 소형 Power Tap Cell (sPTC) 기반의 BSPDN 구조를 구현하고, 다양한 셀 높이 및 배선 조건 하에서의 INV/NAND/NOR Ring Oscillator를 실측하였다. 그 결과, 기존 FSPDN 대비 최대 6% 속도 향상, 7.5% 성능 개선, 5%의 동적 전력 절감이 가능함을 보였으며, 셀 높이를 18%까지 축소하는 데에도 성공하였다.

또한 BSPDN 적용 시 우려되었던 주변 트랜지스터 특성 변화는 Vth의 변화량을 20% 이내로 억제하며 안정성을 확보하였고, 초박막 실리콘 기반에서도 standby leakage 증가 없이 성능을 유지함으로써 고집적 로직 블록에서 면적과 전력을 동시에 최적화할 수 있는 가능성을 실험적으로 입증하였다.

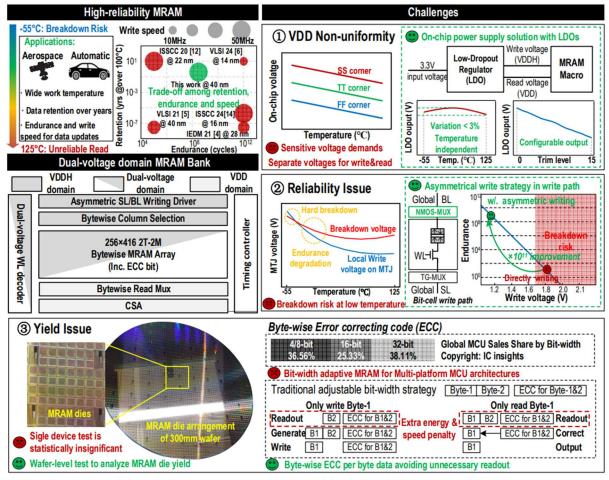

[그림 1] 10-4. 기존 FSPDN과 제안된 BSPDN 구조 및 다양한 BSPDN 옵션 비교

#10-5 본 논문은 Southeast University와 Hong Kong University of Science and Technology, 그리고 ACCESS (AI Chip Center for Emerging Smart Systems) 연구팀에서 발표한 것으로, -55°C에서 125°C까지 동작 가능한 고신뢰성 4Mb STT-MRAM을 40nm 공정 기반으로 설계·제작하고, 94.9%의 웨이퍼 레벨 다이 수율을 실리콘에서 실증한 결과를 담고 있다. 특히, 극한 환경에서도 동작 가능한 신뢰성 확보와 18ns의 빠른 쓰기 시간, 6ns의 읽기 시간 (Error correcting code 포함), 20년 데이터 유지 (retention), 10<sup>8</sup> 이상의 내구성 (endurance)을 동시에 달성한 점이 핵심이다.

이를 위해 본 논문은 세 가지 핵심 기술을 도입하였다. 첫째, 온칩 전력 솔루션으로 온도 및 공정 변화에 독립적인 low-dropout regulators (LDOs) 회로를 활용해 읽기와 쓰기전압을 안정적으로 생성하였으며, 최대 부하 전류 174.6mA에서 62µs의 빠른 기동 속도를 달성하였다. 둘째, asymmetrical write path를 도입하여 P2AP 및 AP2P 쓰기 상황에 따라 회로를 최적화함으로써, AP2P 쓰기에서 28.9%의 전력 소모 감소와 MTJ breakdown 위험 완화를 실현하였다. 셋째, Byte-wise ECC 구조를 도입해 8/16/24/32비트 MCU에 유연하게 대응할 수 있도록 하였으며, 이를 통해 다이 수율이 약 27.1% 향상됨을 실리콘기반 측정을 통해 입증하였다.

또한, MTJ 열 안정성 향상을 위해 2T-2M 구조를 적용하여 기존 1T-1M 대비 고온 (125°C)에서의 읽기 마진이 102% 증가하였고, 300mm 웨이퍼 기반 전체 실측 분석에서 magnetic immunity, retention time, endurance 등의 항목에서도 자동차 및 항공우주급 신뢰성 요구사항을 만족하는 결과를 보여주었다.

[그림 2] 10-5. 제안된 4Mb STT-MRAM의 시스템 구조 및 신뢰성 확보를 위한 핵심 기술 요약

### 저자정보

#### 한창우 박사과정 대학원생

● 소속 : 고려대학교 전기전자공학과

● 연구분야 : 차세대 반도체 소자 및 회로

• 이메일 : cwoo0105@naver.com

● 홈페이지: https://sites.google.com/view/kudclab

한양대학교 신소재공학과 통합과정 송충석

### **Session 23 Cryogenic and Silicon Photonic ICs**

이번 2025 IEEE CICC의 Session 23은 Cryogenic and Silicon Photonic ICs라는 주제로 총 3 편의 논문이 발표되었다.

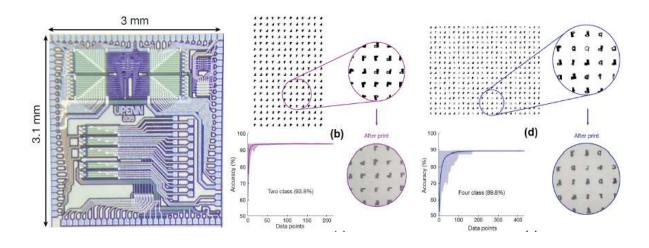

#23-1 이 논문은 펜실베니아 대학교에서 개발한 완전 통합형 photonic deep neural network (PDNN)에 관한 연구이다. 기존의 PDNN에서는 빠른 선형 동작과 낮은 전파 손실에서 장점을 가지지만 부분적으로 통합된 형태로 구현되거나 비선형 함수에 대한 구현이 부족하였다. 본 논문에서는 이러한 단점을 보완하여 비선형 함수를 탑재한 완전히 통합된 PDNN을 제시한다. 570ps의 매우 빠른 이미지 classification 시간을 달성했으며, 광학적 전파를 이용한 계산으로 빠르고 에너지 효율적인 classification을 수행하며, MNIST dataset에 대하여 2클래스에서 93.8%, 4클래스에서 89.8%의 정확도를 달성했다.

이 연구의 핵심은 reconfigurable, trainable한 광학 비선형 함수 (NLAF)를 45nm CMOS SOI 공정에서 집적시킨 것으로 6GHz 대역폭에서 ReLU와 Sigmoid 함수를 모두 지원하며, 임계 값, 기울기, 포화수준을 훈련 가능한 매개변수로 조정할 수 있어 PVT 변화에 대한 강건성을 제공한다. NLAF의 순방향 바이어스 모드로 ReLU가 구현되며 입력 전압이 임계전압보다 작은 경우에는 NLAF의 p-n 접합이 꺼진 상태로 유지되어 출력이 낮게 유지되고, 임계전압보다 클 경우에는 접합이 켜져 출력이 증가하게 된다. 이와 반대로 역방향바이어스 모드로 Sigmoid가 구현된다. 더불어 매개변수들이 네트워크 훈련 중에 최적화되어 PVT 변화의 영향을 효과적으로 보상하게 된다. MNIST 실험에서 단 40에서 452개의 NLAF 매개변수만 조정함으로써 수만 개의 네트워크 가중치에 대한 PVT 보상을 달성했다.

이 연구는 광학 신경망 분야에서 중요한 기술적 진전을 보여주며 특히 PVT 변화에 대한 강건성 문제를 효과적으로 해결한 점이 인상적이다. 그러나 현재 실험이 상대적으로 단순한 MNIST에 대해서만 이루어졌으며, 이는 더 복잡한 실제 응용에서의 성능 검증과확장성에 대한 추가 연구가 요구된다.

[그림 1] 제안된 통합 집적형 PDNN 칩. 2-class 분류와(b) 4-class 분류예시(d)

#23-2 이 논문은 극저온부터 고온까지 동작 가능한 파이프라인 TI-SAR-ADC를 제시한다. 양자 컴퓨팅과 광대역 항공우주/자동차 무선통신의 증가하는 요구에 따라 4K부터 상온까지의 넓은 온도 범위에서 작동하면서 높은 샘플링 속도와 해상도를 달성할 수 있는 ADC 기술이 요구되었는데 기존 ADC는 극저온에서 문턱전압이 약 100mV 가까이 변화하고, 캐리어의 모빌리티가 1.5배 이상 증가하는 등 소자 매개변수의 극단적인 변화로인해 기존 ADC의 활용성이 심각하게 제한되었다.

해당 논문은 Buffer-then-Amplify (BTA) 소스 팔로워(SF) 증폭 방식을 제안한다. 기존의 Amplify-then-Buffer (ATB) 방식과 달리, BTA 방식은 커패시터 차지 펌프를 SF 출력단에 배치하여 SF가 작은 신호만 처리하도록 함으로써 SF의 선형성을 최대한 활용한다. 이를 통해 2차 단계부터 time-interleaving을 적용하여 증폭 전 양자화 문제를 해결하고(기존의 ATB 방식은 증폭되지 않은 작은 신호를 2차 단계의 sub-ADC를 통해 양자화 해야 하는데, 작은 신호를 양자화하기 어렵고 노이즈에 취약함), 고차 보정 없이도 낮은 단계의 보정만으로 10비트 이상의 선형성을 달성할 수 있게 된다. 이를 통해 간단한 회로만으로 고속동작과 높은 효율의 calibration을 구현하게 되어 극저온에서의 소자 특성이 변하는 상황에서 장점을 발휘하게 된다.

12nm FinFET 공정에서 제작된 프로토타입은 0.024mm^2의 면적으로, 4.6K부터 373K까지의 온도 범위에서 800MS/s 샘플링 속도로 54.7dB 이상의 SNDR을 달성한다. 300MS/s 이상, 10비트 이상 ADC 중 가장 넓은 동작 온도 범위를 가지며, 100K 미만에서 작동하는 극저온 ADC 중 최고의 FoM (15.4fJ/conversion-step)을 달성한다.

[그림 2] 프로토타입 ADC에 적용된 회로 schematic.

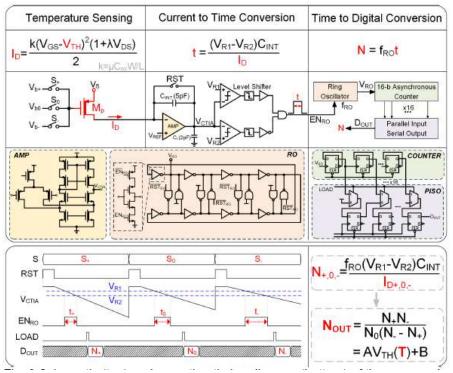

#23-3 이 논문은 PMOS 기본 극저온 CMOS 온도 센서에 관한 연구이다. 초전도 양자 컴퓨팅 제어기나 적외선 천문학 검출기 등의 집적회로 칩들이 액체 질소나 액체 헬륨 온도 범위에서 동작해야 하는 요구가 증가하면서, 온칩 극저온 온도 모니터링을 위한 센서 개발이 요구되었다. 기존의 BJT 기반, 저항 기반, NMOS 기반 센서들은 모두 약 50-60K 이하에서 선형성을 잃거나 포화 현상을 보이는 한계가 있었는데, 반면 PMOS 트랜지스터의 문턱전압은 임계온도 이상에서는 페르미 전위에 기반한 선형적 온도 의존성을 보이고,임계온도 이하에서는 더욱 높은 온도 민감도를 나타내는 특징을 가진다.

본 논문에서 제안하는 센서는 0.13um 공정의 PMOS 트랜지스터를 이용하여 PMOS 트랜지스터 다음에 capacitive trans-impedance amplifier (CTIA)를 배치하여 전류를 전압 신호로 변환하고, 두 개의 비교기와 조합 논리 회로를 통해 전압 신호를 시간 간격으로 변환한 후, 링 오실레이터와 비동기 카운터를 사용하여 디지털 코드로 변환한다. 최종적으로 PMOS 의 문턱전압에만 의존하는 함수를 도출해낸다. 이는 기존의 MOSFET의 전류방정식을 이용해 온도를 측정하기 위해서는 mobility와 문턱전압이 모두 온도에 따라 변하기 때문에 측정하기 어려웠다면 본 논문에서 제시한 방식으로 인해 문턱전압으로만 온도를 측정할 수 있게 된다.

0.13um CMOS 공정으로 제작된 센서는 0.084mm^2 의 면적을 차지하며, 32 개의 센서 칩을 10K 부터 410K 까지 측정한 결과 10K 에서 평균 41uW 의 전력 소모와 20ms 변환 시간으로 295mK 의 RMS 해상도를 달성한다. 10K 부터 410K 까지의 초광대역 동작범위에서 0.5%의 상대 정확도를 보여준다.

이 연구는 극저온 온도 센싱 분야에서 PMOS 트랜지스터의 독특한 물리적 특성을 활용한 혁신적인 접근법을 제시한다. 특히 기존 센서들에서 한계를 보인 극저온 영역에서 동작하는 센서를 구현한 점은 추후 응용분야에서 활용될 가능성이 높아 보인다. 단, 장기간 신뢰성과 공정 변화에 대한 PVS 강건성에 대해서는 추가 연구가 필요해보인다.

[그림 3] 제안한 온도 센서의 스키마틱과 동작 timing diagram.

### 저자정보

### 송충석 통합과정 대학원생

● 소속 : 한양대학교

● 연구분야 : 딥러닝 가속기 설계

• 이메일 : scs940430@hanyang.ac.kr

• 홈페이지 : https://sites.google.com/site/dsjeonglab1/home

KAIST 전기및전자공학부 박사과정 박수언

#### **Session 4 SC-based Power Conversion**

인덕터와 비교하여 높은 energy density를 갖는 커패시터는, datacenter와 같은 고부하, 고밀도, 고효율의 application에서 에너지 저장 및 전달 소자로서 각광받고 있다. 이번 CICC에서는 고밀도 전력 변환을 주제로 한 4편의 커패시터 기반 전력 변환 컨버터 논문이 Session 4에 분류, 발표되어, 이를 간략히 살펴보고자 한다.

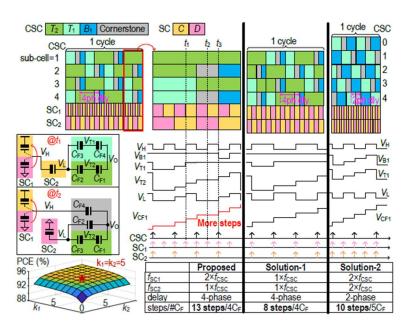

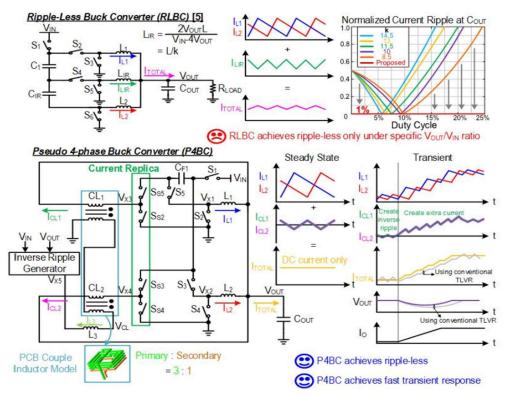

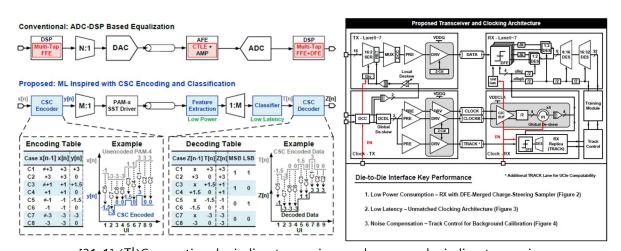

#4-1 은 Macau¹ 대학에서 발표된 논문으로, 적은 수의 off-chip MLCC를 사용하며 Continuously Scalable Conversion (이하 CSC) converter의 flying capacitor의 전압 변화 step 수를 증가시키는 아이디어를 제안하였다. 플라잉 커패시터의 세분화된 전압 레벨 (VB1, ..., VBN, VT1, ... VTN) 수를 증가시키기 위해 그림 1 왼쪽 아래의 2:1 SC1, SC2 컨버터를 CSC 컨버터의 x2, x1배 주파수로 동작시켜, VCF step 수를 증가시킨 점이 주목할만하다. 본 논문은 종래에 발표된 CSC (Butzen [1])에서 세분화된 전압 레벨과 직결되는 많은 수의 Flying capacitor와 switch의 낮은 활용률 문제와 많은 자원 사용의 문제를 해결한 점에서 의미가 있다. 스위칭 주파수의 증가는 효율 감소를 야기하지만, 감소된 플라잉 커패시터와 스위치 수에 의해 전체 면적 대비 실제 powering에 사용되는 스위치 수의 비율증가와 감소된 PCB I/O 포트 수로 인한 PCB trace 면적 증가는 고부하 상황에서 고효율을 달성하는 데 긍정적인 효과를 가져온다.

[그림 1] 2:1 SC1, SC2 converter의 x1, x2 f<sub>CSC</sub> assignment로 증가한 CSC의 V<sub>CF</sub> step

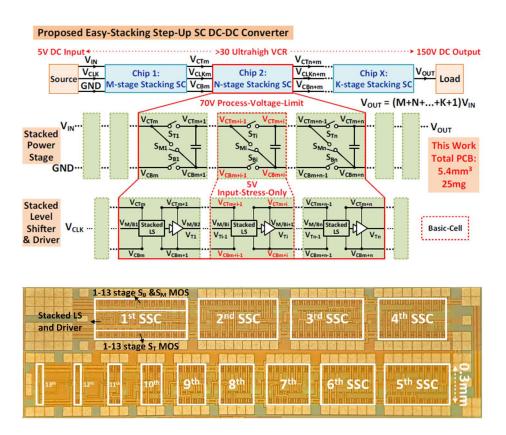

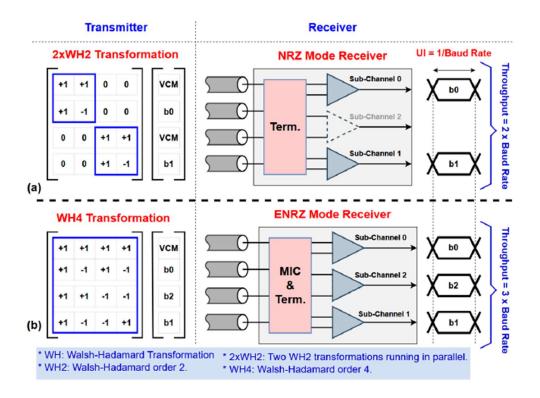

#4-2 는 Tsinghua¹ 대학에서 발표된 논문으로, 5V 입력 전원으로부터 150V의 높은 VCR을 갖는 Boost Converter를 Unit SC-Cell의 stacking 방식으로 구현하는 scalable-VCR의 SC Converter를 발표하였다. 150V에 해당하는 고전압 converter를 높은 energy density를 갖는 capacitor만으로 구현한 점에서 의미가 있으며, 고전압을 5V domain의 저전압 domain으로 나누어, 고효율 특성의 저전압 소자로 고전압 converter의 전력 변환을 가능하게 한 점이 주목할만하다. Unit-Cell을 구성하는 switch들의 gate driving은 unit cell 내부의 flying capacitor를 활용하여 bootstrapping이 필요 없고, level shifter 및 gate driver를 Unit-Cell 내부에서 모두 구현하여 scalability를 유지한 점이 특징이다. 그림 2 아래는 Unit-Cell 들로 구성된 stackable한 chip인데, step-up 컨버터의 특성상 출력에 가까워질수록 작은 전류에 의해 Unit-SC-Cell의 크기가 감소하는 것을(1st→13th) 확인할 수 있다. 높은 VCR을 만들기 위해 chip을 stacking할 경우 후순위의 chip의 1st SC-Cell의 크기는 이전의 chip의 13th SC-Cell보다 큰 상태이기 때문에 Chip-stacking을 할수록 효율 감소 폭이 증가하는 점은 큰 아쉬움으로 보인다.

[그림 2] 저전압 domain의 Unit-Cell 기반의 stackable SC-Converter 구성과(위) 칩 사진(아래)

# 저자정보

# 박수언 박사과정 대학원생

● 소속 : KAIST

● 연구분야 : Power Management IC 설계

● 이메일 : tndjs12221@kaist.ac.kr

● 홈페이지 : https://icdesignlab.net

고려대학교 전기전자공학과 박사과정 이윤호

### **Session 9 : Power Converter Techniques**

이번 2025 IEEE CICC의 Session 9는 Power Converter Techniques 주제로 총 8편의 논문이 발표되었다. 본 세션에서는 데이터 센터, 웨어러블 기기, LiDAR 시스템, 광전 소자 바이어스 회로 등 다양한 응용 환경에 요구되는 전력 변환기의 효율성과 집적도를 향상시키기위한 회로 기술들이 중점적으로 논의되었다. 각 논문은 고전압 혹은 높은 전압 변환비(Conversion Ratio)의 제한을 극복하거나, 경부하 조건에서의 효율을 개선하기 위한 설계기법들을 제안하고 있으며, 대부분의 연구는 GaN 소자, 혼성 토폴로지, 능동 정류기, 적응형 센싱 회로 등 최신 기술을 적극 활용한 것이 특징이다. 본 리뷰에서는 이 중 대표적인 두 논문을 선정하여, 각 구조의 회로적 기술을 중심으로 정리하고자 한다.

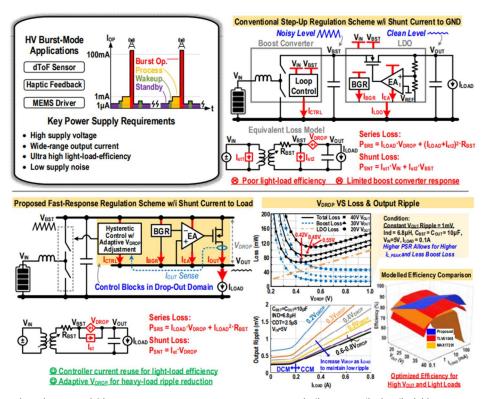

#9-1은 마카오대학교에서 발표한 논문으로, light-load에서도 높은 효율을 유지할 수 있도록 설계된 shunt current-reuse 피드백 구조를 적용한 30V 출력의 step-up regulator를 제안하였다. 제안된 회로는 200μA에서 100mA에 이르는 넓은 부하 범위에서도 85% 이상의 효율을 달성하며, 초저전력 IoT 및 웨어러블 시스템에 적합한 고효율 전력 솔루션을 구현한다. 그림 1의 위과 같이 기존 구조는 switching 방식의 boost converter를 이용해고전압을 생성한 후, 후단의 LDO를 통해 ripple을 제거하는 방식으로 안정적인 출력을 제공하는 방식이다. 그러나 이 구조는 LDO 및 boost converter의 제어 회로에 사용되는 전류가 GND로 소모되기 때문에, 경부하 조건에서는 시스템 전체의 효율이 크게 저하되는 단점이 있다. 이에 반해 본 논문에서는 그림 1 하단에 제시된 바와 같이, LDO 및 converter 제어 회로의 GND rail을 출력 전압에 연결함으로써, 제어 회로에 사용되는 전류를 출력 부하로 그대로 전달할 수 있도록 하였다. 이를 통해 LDO의 전류 효율을 최대 100%까지 향상시켜, 경부하에서도 높은 시스템 효율을 유지할 수 있도록 하였다.

[그림 1] (위) 기존 고전압 step-up low-ripple regulator (아래) #9-1에서 제안한 shunt-currentreuse controller를 이용한 고전압 step-up regulator

아래 그림 2는 #9-1에서 제안한 고전압 step-up regulator의 회로도와 주요 동작 파형을 보여준다. Boost converter는 경부하 조건에서의 효율을 극대화하기 위해, 부하 전류가 매우 낮을 경우 PFM (Pulse Frequency Modulation) 방식으로 동작하며, 부하가 증가하면 COT (Constant On-Time) 기반의 CCM (Continuous Conduction Mode) 으로 전환된다. 또한, 후단 LDO의 dropout 전압은 고정되어 있지 않고, 부하 조건에 따라 CMP1의 threshold를 조절하여 가변적으로 제어된다. 이를 통해, 경부하에서는 dropout 전압을 낮게 유지하여 전력 손실을 최소화하고, 부하가 증가함에 따라 dropout 전압을 점진적으로 증가시켜 출력 출력 전압의 ripple을 효과적으로 저감할 수 있다. 이러한 current-reuse 구조를 통해 제안된 regulator는 0.2mA에서 100mA까지의 넓은 부하 범위에서 85% 이상의 높은 효율을 유지하며, 최대 90.4%의 피크 효율을 달성하였고, 2mV 이하의 출력 전압 리플과 45dB의 노이즈 제거 성능을 확보하였다.

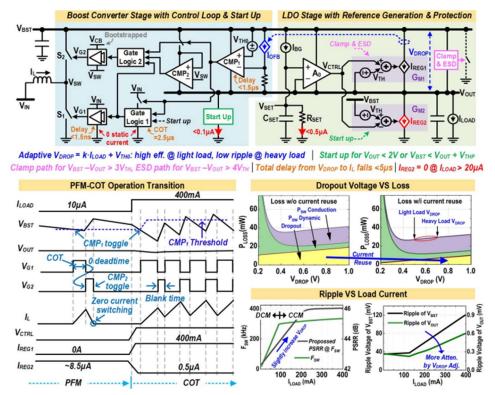

[그림 2] #9-1에서 제안한 shunt-current-reuse 방식의 고전압 step-up regulator의 회로도 및 동작 파형

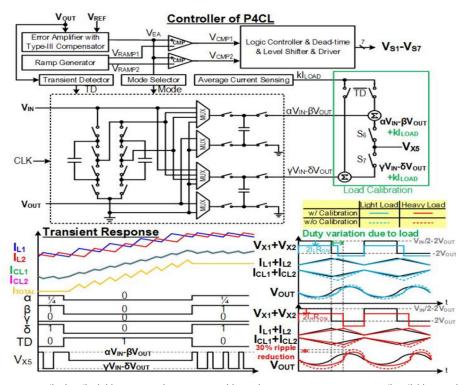

#9-3은 양밍 자오퉁 대학교와 Realtek Semiconductor 등에서 공동 발표한 논문으로, 21V-30V의 고전압 입력으로부터 고전류의 1V 저전압을 출력하며, 낮은 출력 전압 리플과 빠른 과도응답을 동시에 달성하는 pseudo-4-phase Buck Converter를 제안하였다. 해당 연구는 6G 통신 시스템과 같은 LEO (Low Earth Orbit) 위성 전력 시스템을 대상으로하며, 대전류 구간에서도 1mV 이내의 낮은 출력 리플과 94.1%의 높은 효율, 빠른 응답속도를 모두 만족하는 것이 특징이다. 그림 3의 위와 같이 기존 multi-phase buck 구조들은 낮은 리플 특성을 가지지만, 동작 조건에 따라 리플 상쇄의 정도가 달라지는 구조로 인해 특정 동작점에서만 출력 리플이 작다는 제약이 있었다. 본 논문에서는 그림 3의 아래와 같이 pseudo-4-phase 기반의 multi-phase 구조를 제안하여, PCB내의 coupling된인터터 (CL1, CL2) 와 switched-capacitor 기반 inverse ripple generator를 통해 각 phase의전류 리플을 능동적으로 상쇄하고, 출력 리플을 최소화하였다. 특히, 각 위상별 전압 및전류 경로를 정량적으로 분석하여, 리플 상쇄율을 극대화하기 위한 switched-capacitor의 출력을 조절할 수 있도록 한 점이 돋보인다. 본 논문에서 제안한 구조는 이를 기반으로, L1과 L2를 통해 출력으로 전달되는 전류와 각각 반대 위상이 되도록 CL1과 CL2의 전류를 제어하여 이상적으로 출력 전류 리플을 0에 가깝게 만들었다.

[그림 3] (위) 기존의 Ripple-Less Buck Converter (RLBC) (아래) #9-3에서 제안한 Pseudo 4-phase Buck Converter (P4BC)

아래 그림 4는 #9-3에서 제안한 P4BC의 제어 회로 및 inverse ripple generator의 구조와, load transient 상황에서의 동작 파형을 보여준다. 정상 상태에서는 coupling 인덕터인  $CL_1$ 과  $CL_2$ 의 전류가 0A의 DC 전류로  $L_1$ 과  $L_2$ 의 전류 리플을 상쇄하여 출력 전압 리플을 최소화하도록 inverse ripple generator가 동작한다. 반면, 부하 변화가 발생하면 transient 상황을 감지하여 VX5 노드를 순간적으로 0V로 만들고, 이에 따라  $CL_1$ 과  $CL_2$ 의 전류가 일시적으로 증가하여 출력 전압의 강하를 빠르게 보상한다.

또한, 부하 전류에 따라 PWM 듀티가 변동되면,  $CL_1$ 과  $CL_2$ 의 리플 상쇄 효과가 저하될 수 있다. 이를 해결하기 위해, 본 논문에서는 load calibration 회로를 통해 부하에 따른 듀티 변화를 실시간으로 감지하고, inverse ripple generator의 출력을 보상함으로써 모든 동작 범위에서 리플 상쇄 효과를 유지하였다. 이와 같은 회로 기법을 통해 제안된 P4BC는 전 동작 범위에서 1mV 이하의 출력 리플을 유지하였으며, 33V 입력 조건에서 1A-to-10A 부하 변화에 대해 75mV 언더슛 및  $0.8\mu$ s의 복구 시간, 반대 조건에서는 70mV 오 버슛 및  $1\mu$ s의 복구 시간을 달성하였다.

[그림 4] #9-3에서 제안한 P4BC의 control 회로와 transient response에 대한 동작 파형

# 저자정보

# 이윤호 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : Power management ICs

• 이메일 : uknow@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

고려대학교 전기전자공학과 박사과정 이윤호

#### **Session 16: Application-Specific Power Management**

이번 2025 IEEE CICC의 Session 16은 Application-Specific Power Management라는 주제로 총 8편의 논문이 발표되었다. 본 세션에서는 LiDAR 시스템, 삽입형 의료기기(IMD), 압전기반 에너지 하베스팅 (PEH) 회로 등 다양한 응용 분야에 적용되는 PMIC의 기존 문제들을 회로적 기법을 통해 해결하고자 하는 접근이 중심을 이루었다. 특히 LiDAR는 전기차, 드론, 로봇 등 다양한 분야에서 폭넓게 활용되며, 최근 전력 관리 회로 분야에서도 관련연구가 활발히 진행되고 있다. 이번 세션에서는 LiDAR 시스템용 회로에 관한 논문이 2편발표되었으며, 본 리뷰에서는 이들에 대해 간략히 살펴보고자 한다.

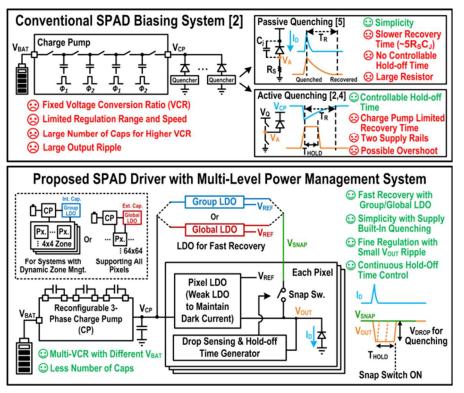

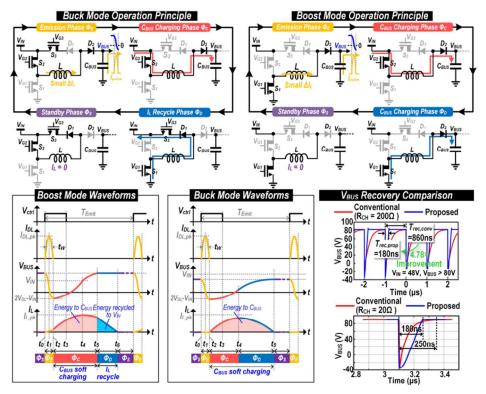

#16-1은 lowa 주립대학과 IBM 왓슨 연구소에서 발표한 논문으로, 배터리 기반 LiDAR 시스템에서 사용되는 SPAD (Single-Photon Avalanche Diode) 드라이버를 위한 멀티레벨전력 관리 구조를 제안하였다. 본 회로는 전원 공급과 quenching 회로를 통합적으로 설계하여 10ns의 초고속 dead time을 달성함으로써, 기존 방식의 긴 회복 시간과 큰 overshoot 및 undershoot을 극복하고자 하였다. 아래 그림 5와 같이, 기존 SPAD biasing 시스템은 charge pump를 통한 높은 전압을 이용하나, 전압 변환 비의 한계, 느린 응답속도, 큰 출력 전압 리플 등의 문제로 인해 SPAD의 동작이 불안정하고 dead time이 길어지는 단점이 있다. 본 논문에서는 이러한 문제를 해결하기 위해, avalanche가 발생하지않는 정상 상태에서는 charge pump를 통해 고전압을 생성하고, 이를 입력으로 하는 pixel 단위의 저전력 LDO를 이용하여 SPAD에 dark current를 공급하는 방식을 제안한다. 아울러, dead time을 최소화하기 위해 avalanche 발생 시 전압 droop을 감지하고, charge pump 출력에 연결된 group 및 global LDO가 이를 능동적으로 활용하여 quenching을 수행하는 회로 기법도 함께 제안하였다.

[그림 5] (위) 기존 2019년 TCAS-1에 소개된 SPAD Biasing system (아래) #16-1에서 제안한 SPAD driver를 위한 multi-level 전력 관리 시스템

아래 그림 6은 그림 5에서 제안한 SPAD driver를 위한 multi-level 전력 관리 시스템의 회로 구성과 동작 원리를 보여준다. 제안된 시스템에서의 quenching 및 recovery 동작은 다음과 같다. 정상 상태 동작 시, 전류 구동 능력이 약한 Pixel LDO를 이용하여 SPAD에 bias를 인가하고, dark current를 공급한다. 이후 SPAD에 avalanche가 발생하면, SPAD의 bias 전압에 급격한 droop이 발생하며, 이러한 droop은 skewed inverter를 통해 감지된다. 감지된 신호는 current starved inverter로 구성된 delay cell에 전달되며, 설정된 hold-off 시간이 지난 후에는 구동 능력이 강한 group 및 global LDO를 통해 SPAD bias 전압이 빠르게 복구된다. 이러한 동작 원리를 기반으로, 전력 관리 시스템은 측정 결과 최대 91.5% 전력 효율을 달성하였으며, 3×3 SPAD array가 동시에 avalanche 된 조건에서 10ns의 최소 dead time을 구현하였다.

[그림 6] #16-1에서 제안한 SPAD quenching과 recovery를 위한 회로도 및 동작 원리

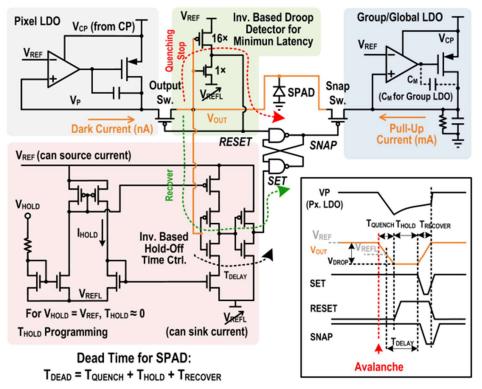

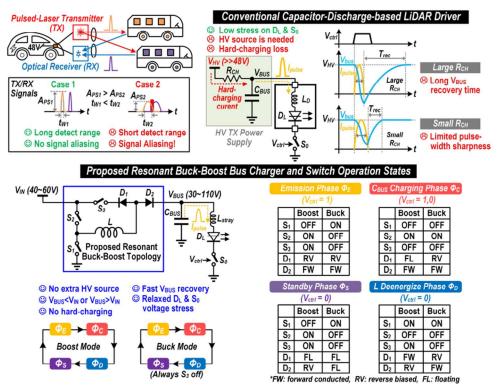

#16-3은 마카오대학교와 UM Hetao IC Research Institute, 리스본대학교에서 발표한 논문으로, 자동차용 MHz 주파수 LiDAR 송신기를 위한 고속, 고전류의 레이저 펄스 구동이가능한 공진형 벅-부스트 충전기를 제안하였다. LiDAR는 자율주행차량, 드론 등의 분야에서 핵심적인 거리 인식 및 3D 센싱 기술로 각광받고 있으며, 이를 위해 송신기 측에서는수 ns 단위의 짧은 펄스 폭과 수십 암페어의 피크 전류를 안정적으로 생성할 수 있는 LiDAR driver가 요구된다. 아래 그림 7의 우측 상단과 같이, 기존에는 버스 커패시터의 전하를 레이저 다이오드를 통해 방전하며 전류 펄스를 생성하는 방식이 사용되었으며, 이방식은 디바이스의 과전압 스트레스를 방지하는 장점이 있었다. 그러나, 높은 내압을 견디는 대용량 커패시터가 필요하며, 이를 위한 고전압 source가 요구되며, 커패시터 충전시 발생하는 hard-charging 손실과 전류 펄스 폭 간의 trade-off로 인해 고속 구동에 제약이 있었다. 이러한 기존의 문제점을 극복하고자, 본 논문에서는 그림 7의 아래와 같이추가적인 고전압 source와 버스 커패시터의 hard-charging 없이, 버스 전압을 빠르게 복구할 수 있는 공진형 벅-부스트 구조를 제안했다.

[그림 7] (위) 기존 커패시터 방전 방식의 LiDAR driver의 한계 (아래) #16-3에서 제안한 공진형 벅-부스트 버스 충전기 구조

아래 그림 8은 본 논문에서 제안한 공진형 벅-부스트 버스 충전기의 동작 원리를 보여준 다. 본 구조는 벅 모드와 부스트 모드 모두에서 동작하며, 공통적으로 emission phase, 버스 커패시터 충전 phase, standby phase로 구성된다. 여기에 더해, 벅 모드에서는 인덕 터 전류 재활용 phase가, 부스트 모드에서는 추가적인 버스 커패시터 충전 phase가 포 함된다. 동작 예로 벅 모드를 살펴보면 다음과 같다. 먼저, 고전류 펄스를 생성하는 emission phase에서는 버스 커패시터와 레이저 다이오드의 기생 인덕턴스가 공진을 이루 며, 버스 커패시터의 전하가 다이오드를 통해 방전되면서 고전류의 펄스가 형성된다. 이 후 전류 펄스 생성이 거의 종료되면, 인덕터는 입력 전압으로부터 에너지를 저장하며 버 스 커패시터를 충전한다. 버스 전압이 목표 전압에 도달한 이후에는, 인덕터 전류가 0에 이를 때까지 입력으로 다시 방전되며 에너지가 재활용된다. 이러한 공진 기반의 동작 방 식을 통해, 제안된 구조는 별도의 고전압 소스나 버스 커패시터의 hard-charging 없이 고전류 펄스를 안정적으로 생성하며, 기존 방식에서 문제가 되었던 hard-charging에 의 한 손실을 효과적으로 감소시켰다. 아울러, 기존 구조에서 고전압 source와 버스 커패시 터 간의 큰 inrush 전류를 줄이기 위해 삽입되었던 path 저항을 제거함으로써, 보다 빠른 버스 전압 복구가 가능해졌다. 이러한 공진형 벅-부스트 버스 충전기의 장점을 바탕으로, 기존 path 저항 삽입형 커패시터 방전 구조 대비 최대 43%의 전력 손실 저감을 달성하 였고, MHz급 구동에서도 안정된 버스 전압 충전 및 방전을 가능하게 하였다.

[그림 8] #16-3에서 제안하는 공진형 벅-부스트 버스 충전기의 동작 원리 및 파형

# 저자정보

## 이윤호 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : Power management ICs

• 이메일 : uknow@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

고려대학교 전기및전자공학부 박사과정 안재웅

#### **Session 24 Hybrid DC-DC Converters**

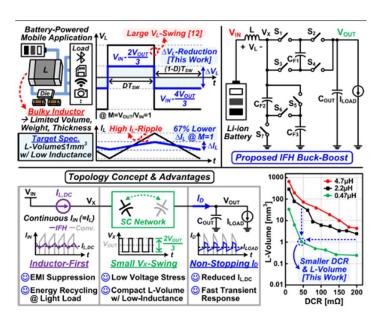

이번 2025 CICC의 Session 24에서는 Hybrid DC-DC Converters라는 주제로 총 4편의 논문이 발표되었다. 이 중 #24-1은 hybrid converter의 발전과 새로운 FoM을 제시하였으며 #24-3은 데이터 센터용 conveter를 발표하였다. 또한 #24-5는 모바일용 buck-boost converter를 발표하였다.

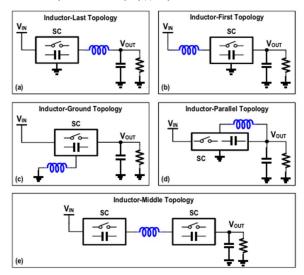

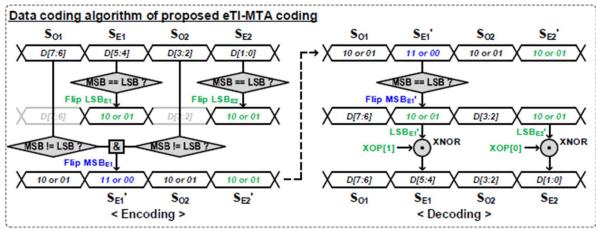

#24-1 논문은 switched-capacitor(SC)와 인덕터 기반의 구조를 결합한 SCI hybrid DC-DC buck topology들을 비교·분석하였다. 기존의 buck 또는 SC 기반 컨버터가 각각 갖는 한계를 극복하기 위해, 인덕터 위치를 기준으로 구조를 다음과 같이 분류하였다: Inductorlast, Inductor-first, Inductor-ground, Inductor-parallel, Inductor-middle. 각 구조는 인덕터의 전류 스트레스, 출력 리플, VCR 등의 관점에서 장단점을 가진다.

예를 들어, Inductor-last 구조는 전압 리플과 스위치의 전압 스트레스를 줄일 수 있는 장점이 있지만, 인덕터가 출력 전류 전체를 감당해야 한다는 부담이 있다. 반면 Inductor-first 구조는 입력 전류의 연속성을 확보할 수 있어 EMI 저감에 유리하지만, 전압 변환비가 제한적이어서 다양한 응용에는 부적합하다는 단점이 있다.

또한 이 논문에서는 효율과 전력 밀도를 함께 고려한 pre-design FoM 식과 topology 간상대 성능을 비교할 수 있는 정규화된 FoM을 제안하여, 전통적인 buck 구조 대비 hybrid 구조의 우수성을 정량적으로 분석하였다.

[그림 1] #24-1에서 제시한 5가지로 분류한 컨버터 topology

[그림 2] #24-1에서 제시한 기존의 Inductor last hybrid topology

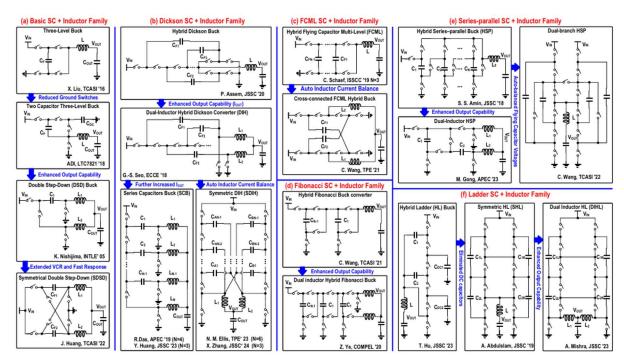

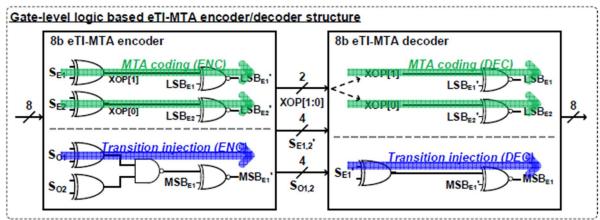

#24-2 논문은 데이터 센터에서 사용 가능한 DC-DC 컨버터를 제안하였다. 데이터 센터는 multi-core CPU 및 GPU의 사용으로 인해 100A 이상의 high current 와 1000A/µs 이상의 고속 load transient 특성을 요구한다. 기존의 hybrid converter나 LLC converter는 각각 고효율 또는 넓은 conversion ratio를 제공하지만, heavy load 환경에서는 효율이 떨어지며 voltage regulation capability에도 한계가 있다. 이를 해결하기 위해 본 논문은 double step-down(DSD) converter와 LLC converter를 융합한 새로운 하이브리드 토폴로지를 제안하였다. 제안된 구조는 각각의 장점을 동시에 취하면서, 트랜지언트 응답 성능 또한 크게 향상된다. steady-state에서는 flying capacitor 전압으로 LLC를 구동하고, 트랜지언트 상황에서는 입력 전압을 직접 LLC에 인가하여 voltage droop를 최소화하는 방식이다.

이로 인해 70A/20ns의 부하 변화 조건에서 전압 undershoot는 기존 167.5mV에서 51mV로 감소하며, 3배 이상 개선된 성능을 달성하였다. 효율 측면에서는 출력 전압 VO = 1V 기준, 입력 전압이 48V일 때 89%, 60V일 때는 86%의 효율을 보여준다.

[그림 3] #24-2 논문에서 제안하는 hybrid LLC resonant converter 구조

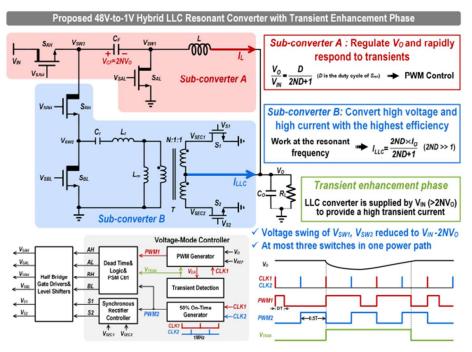

#24-5 논문은 모바일 디바이스를 위한 새로운 buck-boost 컨버터 구조를 제안하였다. 제안된 회로는 Inductor-first 구조를 채택하여 인덕터를 입력단과 직렬로 배치함으로써 입력 전류의 연속성을 확보하고, 이를 통해 EMI를 효과적으로 저감하였다. 또한 light load 조건에서는 출력 전류가 입력으로 회귀하는 동작 특성을 통해 light load 효율 향상을 가능하게 하였다. 회로는 3개의 flying capacitor와 7개의 스위치로 구성되어 있으며, 인덕터 voltage swing을 제한하여 전류 리플을 감소시켰다. 더불어, 전 변환 비율 범위에 걸쳐 VX 노드 전압을 고정함으로써 스위치의 전압 스트레스를 최소화하고, 모드 전환 없이 single-mode operation를 유지할 수 있도록 설계되었다. 성능 측면에서, 입력 전압 3.8V, 출력 전류 0.3A 조건에서 최대 효율 97.2%를 기록하였으며, light load와 heavy load 모두에서 고효율 특성을 안정적으로 유지하였다. 트랜지언트 응답은 ΔΙ<sub>LOAD</sub> = 1A, Τ<sub>EDGE</sub> = 200ns 조건에서 130mV의 undershoot를 나타내어 빠르고 안정적인 응답 특성을 보였다. 또한, 0.47μΗ 인덕터, 1.02mm³ 볼륨 기준으로 565mA/mm³의 전류 밀도를 구현할 수 있어, 소형 인덕터 기반의 고밀도 집적 설계에도 적합하다.

[그림 4] #24-5 논문에서 제안하는 inductor-first hybrid buck-boost converter 구조

[그림 5] #24-5 논문에서 제안하는 IFH converter의 구동 방식

# 저자정보

#### 안재웅 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : 디스플레이 드라이버 / 픽셀 보상 / 터치 센서

• 이메일 : ajw1104@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

고려대학교 전기및전자공학부 박사과정 안재웅

# **Session 2 Analog Building Blocks and Sensing Circuits**

이번 2025 CICC의 Session 2에서는 analog building blocks and sensing circuits라는 주제로 총 5편의 논문이 발표되었다. 이 중 #2-1은 mixed-signal 구조를 활용한 고속·저잡음 current sensing 회로를 제안하였으며, #2-3은 high input impedance와 flicker noise reduction을 동시에 달성한 뇌파 측정용 증폭기를 발표하였다. 또한 #2-5는 배터리 상태 진단이 가능한 고정밀 AFE를 구현하였다.

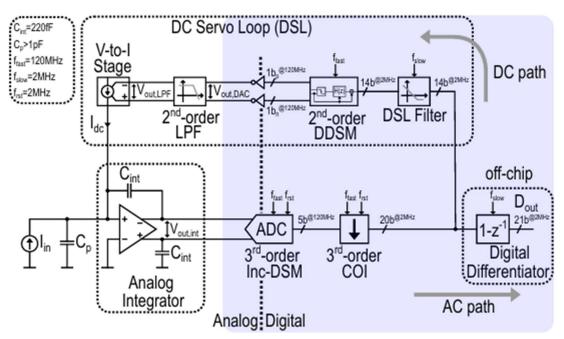

#2-1 논문은 low noise와 high throughput을 동시에 만족하는 current sensing을 위해 mixed-signal integrator-differentiator TIA(MS-TIA)를 제안하였다. 기존 analog I-D-TIA는 integrator로 낮은 노이즈를 확보하고 differentiator로 고속 처리를 달성하지만, 아날로그 differentiator는 고속 동작을 위한 대형 커패시터와 높은 전력 소모, 면적 부담 등 구조적 한계를 지닌다. 본 논문은 이러한 한계를 극복하고자, differentiator와 DC servo loop (DSL)를 디지털 블록으로 대체하여 주요 신호 처리를 디지털 도메인으로 이전함으로써 공정 이점을 극대화하고 설계 유연성과 확장성을 확보하였다. 입력 전류는 아날로그 integrator에서 적분된 후, 3차 incremental delta-sigma modulator와 COI 필터를 통해 직접 디지털화되며, 디지털 differentiator를 통해 AC 성분을 분리하고, 디지털 DSL 필터와 2차 digital DSM을 통해 DC feedback을 구현한다. 또한 아날로그 영역에서는 chopper 방식의 voltage to current converter와 2차 아날로그 low pass filter를 통해 정밀한 DC current feedback을 제공한다. 실측 결과, floating input 기준 최소 spot noise는 22fA√Hz, DC bias ±12nA 조건에서도 28fA/√Hz로 유지되었으며, 1MHz bandwidth에서 통합 노이즈는 131pArms에 달했다. 입력 주파수에 따라 동적 범위가 달라지며, -6dBFS 기준 800kHz 입력에서 SNDR 58.2dB, SFDR 64.0dB의 성능을 기록하였다.

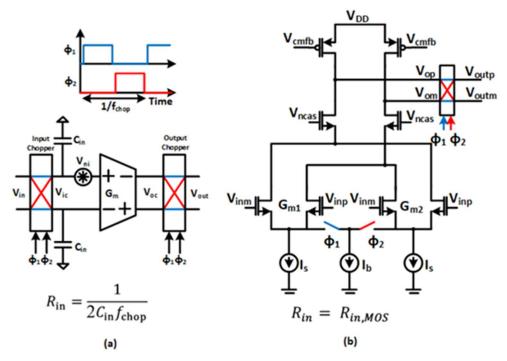

[그림 1] #2-1에서 제시한 mixed signal integrator-differentiator TIA

#2-3 논문은 neural recording 응용을 위한 high input impedence를 가지는 buffer amplifier를 제안하였다. 기존의 chopper-stabilized amplifier는 flicker noise를 효과적으로 억제할 수 있으나, 입력단 스위칭에 의해 input impedance가 수십  $M\Omega$  수준으로 낮아져 high impedance 소스와의 연결 시 신호 감쇠가 발생하는 문제가 있다. 본 논문에서는 이러한 문제를 해결하기 위해, 입력단에 스위치를 도입하지 않고 tail current에 chopping을 적용하는 bias chopping 기법을 제안하였다. 이 방식은 입력 MOS 트랜지스터 자체의 임 피던스를 그대로 유지하면서도, 신호를 chopping 주파수로 변조하여 flicker noise를 상위대역으로 이동시키고 저역에서 제거할 수 있도록 한다. 실측 결과, 입력 임피던스는 최대  $20G\Omega$ , 평균  $16.7G\Omega$ 으로 측정되었으며, conventional chopping 대비 최대 9dB, 평균 약 8dB 수준의 SNR 개선이 확인되었다. 특히 source impedance가 높은 조건에서 conventional 방식 대비 신호 감쇠가 크게 줄어들어 실제 응용 환경에서 실질적인 SNR 이 더 향상되는 효과가 입증되었다. 또한 전체 회로는 0.003mm²의 초소형 면적과  $64\mu$ W 의 소비전력을 가진다.

[그림 2] (a) 기존의 chopping 방식과 (b) 제안하는 chopping 방식

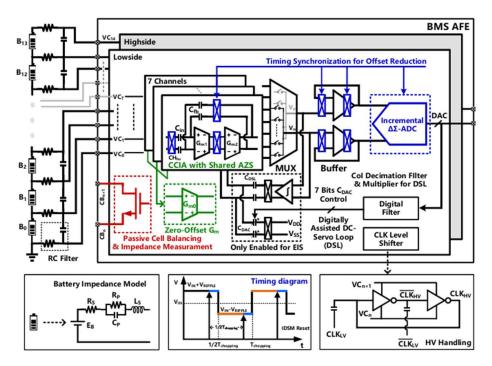

#2-5 논문은 총 14셀의 리튬이온 배터리를 모니터링할 수 있는 AFE를 제안하였다. 본 회로는 배터리 전압 측정 정확도를 극대화하기 위해 1mV 이내의 Total Measurement Error를 달성하였으며, 동시에 Electrochemical Impedance Spectroscopy (EIS)기능을 통합 하여 State of Health까지 가능한 점이 큰 특징이다. AFE의 핵심 증폭기는 capacitivelycoupled chopper instrumentation amplifier (CCIA) 기반이며, 여기에 채널 공유형 autozero stabilization (AZS) 경로를 도입하여 입력 offset을 억제하고, chopping 동기화를 통 해 출력 ripple을 디지털 필터 레벨에서 제거함으로써 추가적인 아날로그 회로 없이 높 은 정확도를 확보하였다. AZS 경로는 7개의 채널이 순차적으로 공유하며, 면적과 전력 측면 모두에서 효율적이다. EIS 기능은 기존의 패시브 셀 밸런싱 회로를 그대로 재활용하 여 구현되었으며, 외부 회로 추가 없이 1-bit delta-sigma 방식의 bit-stream current IP를 주입하고, 배터리 양단 전압 응답을 통해 실시간 임피던스를 추정한다. EIS 동작 중에는 coarse/fine DC servo loop을 순차적으로 적용하여 대용량 DC 성분을 제거하고, 이에 따 라 3Hz에서 2kHz까지의 주파수 대역과 0.2mΩ 수준의 임피던스 분해능을 확보하였다. 또한 incremental delta-sigma ADC의 내부 동작을 활용해 chopping에 의해 유입되는 ripple 성분을 디지털 필터 가중치 비대칭을 통해 자연스럽게 상쇄함으로써, 회로 복잡도 증가 없이 ripple-free 출력을 얻는 기법도 함께 제안되었다. 회로는 0.18µm BCD 공정으 로 구현되었으며, 12.5mm² 면적과 2.3mA@5V의 저전력으로 구동된다. 실측 결과, -40℃

에서 85°C에 이르는 넓은 온도 범위에서도 70채널 모두 TME가 1mV 이내로 유지되었고, AZS 및 chopping 동기화 적용 시 출력 ripple은 0.1mV까지 억제되었다.

[그림 3] #2-5 논문에서 BMS AFE 구조

## 저자정보

#### 안재웅 박사과정 대학원생

● 소속 : 고려대학교

● 연구분야 : 디스플레이 드라이버 / 픽셀 보상 / 터치 센서

• 이메일 : ajw1104@korea.ac.kr

• 홈페이지 : https://sites.google.com/site/kubasiclab/home

KAIST 전기및전자공학부 박사과정 박수언

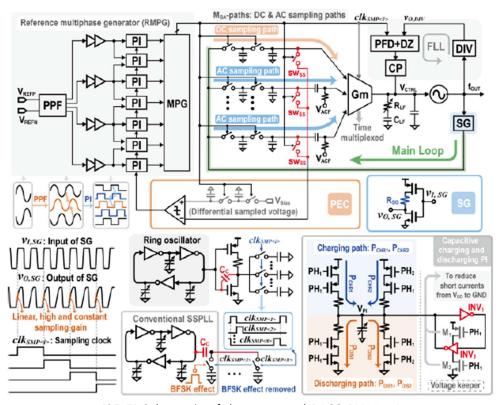

# Session 12 Advancements in Low-Power, High-Performance Analog Sensing and Interface Technologies

#12-2 는 Peking 대학에서 발표된 논문으로, IoT, 의료, wearable 등에 사용되는 energy efficient한 CT-based의 tracking-zoom sensor 구조를 발표하였다. 제안하는 구조는 높은 해상도와 에너지 효율성을 모두 갖기 위해 zoom architecture를 채택하였으며, ΔΣ loop이 artifacts에 의해 saturation되는 경우 asynchronous SAR이 동작하여 효율적으로 빠른 recovery 수행한다. Fine-quantization을 위한 CCO를 current-reuse 특성을 갖는 floating domain에서 구현하여 energy efficiency를 더욱 증가시킨 점이 차별화된 특징이다. Capacitive DAC의 matching을 위해 SAR과 CCO DAC을 layout에서 인접하도록 배치하였으며, input-impedance boosting 목적으로 2개의 replica-DAC을 coupling capacitor의 앞에 배치시켰다. Prototype은 4.82μW의 낮은 전력소모와 183.4dB의 FoM<sub>SNDR</sub>\*를 달성하였다.

Low-Cost Fast Tracking Technique

[그림 3] 본 논문에서 제안하는 Sensor readout frontend 구조

<sup>\*</sup>FoM<sub>SNDR</sub>=SNDR+10log<sub>10</sub>(BW/Power)

#12-3 은 Zhejiang<sup>1</sup> 대학에서 발표된 논문으로, Touch-sensor 의 정확성과 직결되는 높은 frame-rate 에 수반되는 dynamic power loss 의 감소 아이디어를 발표하였다. 높은 frame-rate 로 변하는 2-Level 0, 1 Digital 신호의 전압 변화( $\Delta V$ )를 3-level  $\Delta V$ /2 로의 변환을 통해  $CV^2f \rightarrow 1/4CV^2f$  로 감소시킨 dynamic power loss 가 큰 장점이다. 또한, 에너지 효율적인 터치 위치의 판단을 위해 스크린 전체를 탐색하지 않고, 터치된 부분과 인접한 부분의 신호 합  $S_{1,4}$ 을 정의하고 해당 신호의 합이 가장 큰( $W_1$ ) 신호에 공통된 신호( $R_{X1}$ )가 터치된 부분임을 결정하는 탐색 알고리즘을 사용해, dynamic power loss 를 크게 감소시켰다.

[그림 4] 본 논문에서 제안한 Energy-efficient Touch sensing algorithm

## 참고문헌

[1] N. Butzen et al., "Design of Single-Topology Continuously Scalable- Conversion-Ratio Switched-Capacitor DC-DC Converters," IEEE JSSC, vol. 54, no. 4, pp. 1039-1047, Apr. 2019.

#### 저자정보

#### 박수언 박사과정 대학원생

● 소속 : KAIST

● 연구분야: Power Management IC 설계

이메일: tndjs12221@kaist.ac.kr홈페이지: https://icdesignlab.net

서울대학교 전기정보공학부 박사과정 박현준

# Session 14 Innovations in High-Performance Analog and Mixed-Signal Circuit Design

최근 회로 및 시스템 분야에서는 고성능과 높은 효율성, 저잡음 특성을 동시에 만족하는 설계 기술이 주요 관심사로 떠오르고 있다. 2025 CICC Session 14에서는 최신 공정과 혁신적인 토폴로지를 활용하여 이러한 요구를 효과적으로 충족한 여러 연구가 소개되었다. 밀리미터파(mm-wave) VCO, MEMS 마이크로 스피커 드라이버, 초고속 다이내믹 비교기, 고정밀 오디오 디코더 등 다양한 응용 분야에서 성능과 효율성을 높이는 기술적 진보와 창의적인 접근법이 제시되었다.

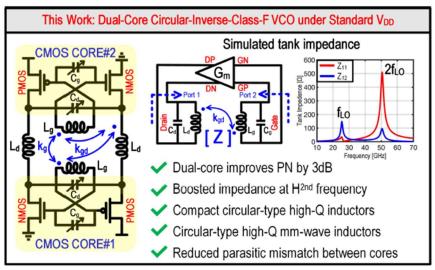

#14-1 본 논문은 65nm CMOS 공정에서 구현된 밀리미터파(mm-wave) 듀얼코어 circular-inverse-class-F VCO를 제안하였다. 기존 설계들이 FoM 향상을 위해 낮은 공급 전압을 요구하는 것과 달리, 본 설계는 표준 전압(1.2V) 하에서 우수한 성능을 제공한다. 22.0~28.4GHz의 주파수 대역에서 동작하며, 10MHz 오프셋에서 최대 192.2 dBc/Hz의 FoM과 206.2 dBc/Hz의 FoMA를 달성하였다. 특히, 듀얼코어 구성과 원형 토폴로지 인덕 터를 활용하여 위상잡음 성능을 약 3 dB 향상시키고, 칩 면적을 0.04 mm²로 최소화하였다.

[14-1] The proposed dual-core circular-inverse-class-F CMOS VCO.

#14-2 본 논문은 피에조 MEMS 마이크로 스피커(MMS)를 위한 고성능 클래스-H 드라이버를 제안하였다. 180nm BCD 공정으로 제작된 본 드라이버는 단일 리튬 이온 배터리 (2.75.5V)에서 구동되며, 최대 30Vpp의 오디오 신호 출력과 DC 바이어스 전압(515V)을 효율적으로 공급한다. Envelope tracking을 적용한 SIDO 부스트 컨버터와 클래스 AB 앰프를 통해 106.1dBA의 DR을 달성하였고, 디지털 및 아날로그 입력을 모두 지원하면서 2.1μs 이하의 매우 낮은 지연시간과 450μA의 낮은 idle 전류를 구현하였다.

[14-2] (좌)Block diagram of the MEMS micro-speaker driver

[14-3] (우)Proposed dynamic comparator with resistive dynamic bias pre-amplifier

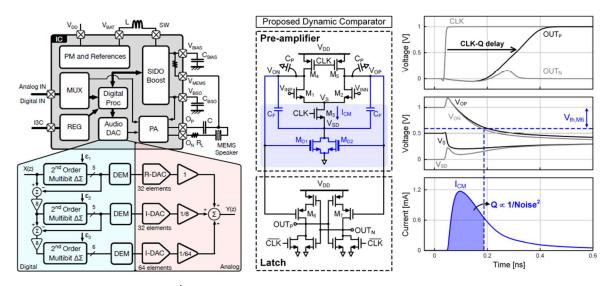

#14-3 본 논문은 28nm FD-SOI 공정으로 제작된 저잡음, 고속의 다이내믹 비교기를 제안하였다. 제안된 비교기는 flying capacitor를 이용한 저항성 동적 바이어스 기법을 적용하여, 기존 비교기의 속도와 잡음 간의 트레이드오프를 극복하였다. 1GS/s 이상의 동작 속도에서 129μVrms의 낮은 입력 참조 잡음과 0.39ns의 짧은 CLK-Q 지연을 동시에 달성하였다. 또한 입력 공통 모드 전압(VCM)에 따른 잡음과 CLK-Q 지연의 민감도를 크게 낮추었으며, 소모 에너지는 변환 당 288fJ로 우수한 효율성을 나타냈다.

#14-4 본 논문은 mismatch와 ISI를 동시에 저감하는 단일 벡터 양자화기(VQ)를 활용한 고성능 IDAC 기반 오디오 디코더를 제안하였다. 0.18μm CMOS 공정으로 제작된 본 디코더는 mismatch와 ISI shaping 루프를 통합한 단일 VQ 기술을 통해 -117.1dB의 우수한 THD와 -107.4dB의 THD+N, 111.2dB의 DR(A-weighted)을 달성하였다. 특히, 620ps rms의 높은 클록 지터 조건에서도 -100.9dB의 낮은 THD+N을 유지하여 우수한 지터 내성을 보였으며, 효율적인 디지털 설계로 전력과 면적을 각각 23%와 22% 감소시켰다.

[14-4] Block diagram of the proposed audio decoder.

# 저자정보

# 박현준 박사과정 대학원생

● 소속 : 서울대학교

● 연구분야 : 수학

● 이메일 : <u>spp098@snu.ac.kr</u>

서울대학교 전기정보공학부 박사과정 박현준

#### Session 25 High-speed Wireline and Optical Communication

Session 25에서는 최신 CMOS 공정 기술을 활용하여 고속 데이터 통신 시스템의 핵심이슈인 광대역 동작 범위, 높은 데이터 전송률, 저잡음 및 우수한 전력 효율성 등을 해결하기 위한 혁신적인 회로 설계 기법들이 제안되었다. 이를 통해 최근 고속 통신 분야의주요 설계 트렌드가 저전력, 저잡음, 넓은 동작 범위 및 고효율 데이터 전송 기술로 집중되고 있음을 확인할 수 있었다.