MMSIM · Xcelium · Spectre · Virtuoso Layout Suite · Assura · QRCX · AMS/APS · Virtuoso Schematic Editor

Cadence 사

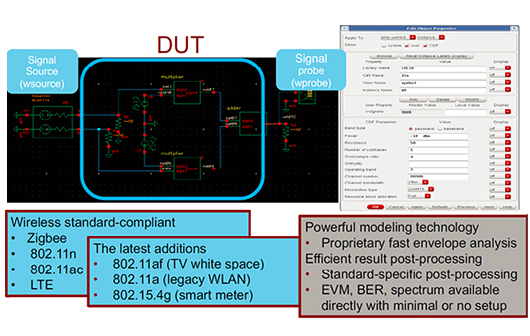

Cadence MMSIM

- A. 목적 : Simulation

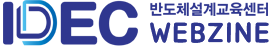

- B. 구분 : Cadence의 Circuit simulator를 한개의 software에 묶어놓은 Software Package

-

C. Supported platform and OS/ System

- - SUN Solaris10/ RHEL5, 6/ SUSE10, 11/ AIX6.1

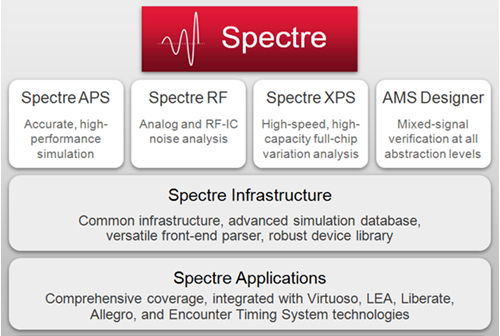

- D. 특성 : Spectre / SpectreRF /XPS/ APS / AMSDesigner로 구성되어 있으며, Analog Design Environment에서 invoke해서 사용 가능함

-

E. 기능

- - Spectre : Spice level accuracy를 제공

- - SpectreRF : S-parameter를 이용한 RF simulator

- - XPS : Full chip simulation의 capability를 제공

- - APS : Spectre와 동등한 정확도를 갖으며 fast simulation을 제공

- - AMS Designer : Mixed signal의 simulation을 제공

Integrated into the Virtuoso Analog Design Environment

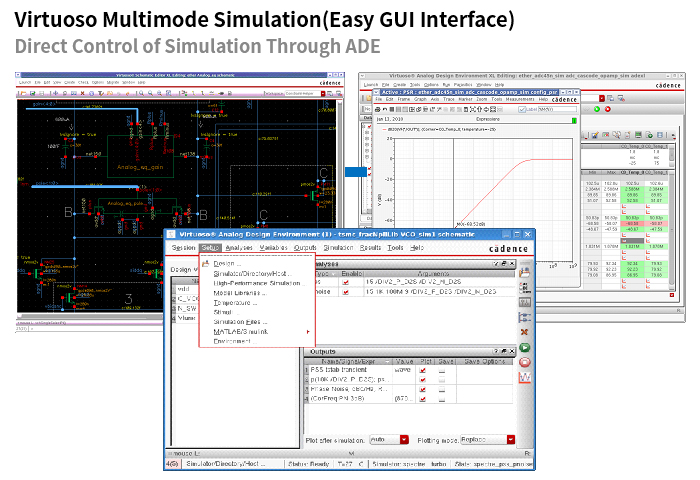

Cadence사 Xcelium™ Simulator

- A. 목적 : Functional Logic Verification

- B. 구분 : Cadence사의 Xcelium™은 는 반도체 설계의 functional logic verification에 다양하고 효과적인 solution을 제공

-

C. Supported platform and O/S System

- - RHEL 6, RHEL 7/ SLES 11

-

D. 특성 및 기능

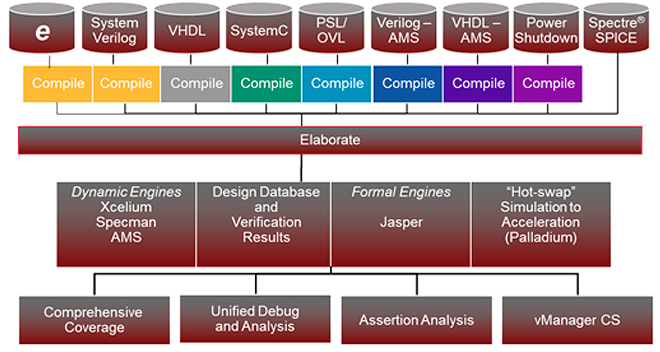

Xcelium™은 아래의 <그림1>과 같이 Multi language를 지원하는 simulator로서 다양한 language, methodology (eRM, OVM, UVM), CPF(Common Power Format)/IEEE1801(UPF2.0)를 이용한 Power aware simulation, coverage, functional-safety simulation 등을 지원합니다.

<그림1> Xcelium - Native-Compile and Multi-Language Support

-

Xcelium™은 functional verification 분야에서 유일하게 모든 IEEE-standard language들과 gate level부터 system level에 이르는 모든 design abstraction들을 지원합니다. 또한, tool에 적용가능한 verification plan도 지원합니다.

Cadence functional verification platform에서 제공하는 Verification IP(VIP), HW acceleration/emulation 및 analog/mixed signal/RF verification 등의 구성요소들을 가지고, Xcelium™은 다양한 종류의 testbench, HDL, CPF/IEEE1801(UPF2.0) file, Software 및 assertion IP들도 지원합니다.

Source code의 Compile과 elaboration시 MSIE(Multiple Snapshot Incremental Elaboration) 기능을 사용하여 최대 10배까지 build time 성능 개선 및 스토리지 절감을 달성할 수 있습니다.

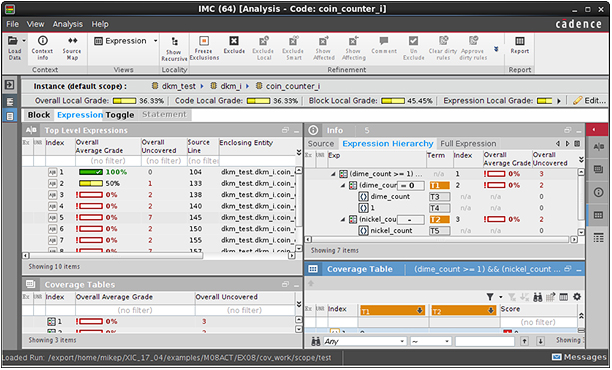

Xcelium™은 모든 상용의 coverage metric(assertion coverage, code coverage, functional coverage등)들을 포함하는 total coverage analysis 를 지원합니다. 따라서, 사용자는 모든 종류의 coverage 결과를 IMC(Incisive Metric Cetor)라는 하나의 GUI를 통해서 분석하므로써, 모든 function 들이 빠짐없이 test되었는지 확인해 볼 수 있고, 이것을 통해 한 번에 error가 없는 silicon을 얻을 수 있습니다.

<그림2> Coverage Analysis with IMC

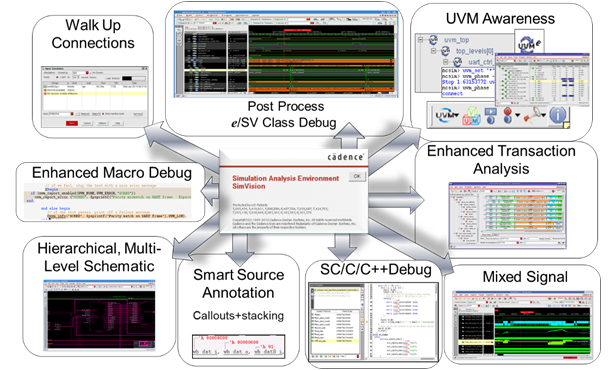

- Xcelium™에서 제공되는 SimVision tool은 하나의 통합 GUI환경에서 모든 IEEE-standard design, testbench 및 assertion language에 대하여 signal level부터 transaction level까지 통합된 debugging을 수행할 수 있게 해 줍니다.

<그림3> Debugging with SimVision

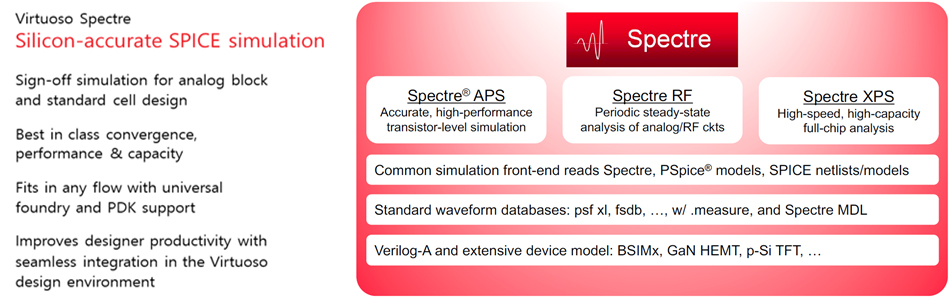

Cadence사 Spectre / SpectreRF

- A. 목적 : Simulation

- B. 구분 : Spice의 Accuracy를 가지는 Cadence의 Simulator

- C. 특성 : Time & Frequency에 대해서 Analysis가 가능하며, GUI에서 사용하기 편한 Interface를 제공

- D. 기능 : AC, Transient, DC 등의 Analysis를 제공

1. Cadence Spectre

- A. 목적 : Simulation

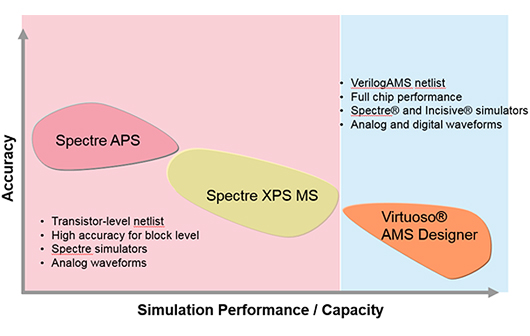

- B. 구분 : RF simulator

- C. 특성 : S-Parameter를 연산 할 수 있으며, Harmonic Balance & Shooting Newton Algorithm을 이용한 RF Circuit Design 가능함

- D. 기능 : PSS, PNOSE, PAC, QPSS, QPNOISE, QPAC를 simulation하는 것이 가능함

2. Cadence Spectre RF

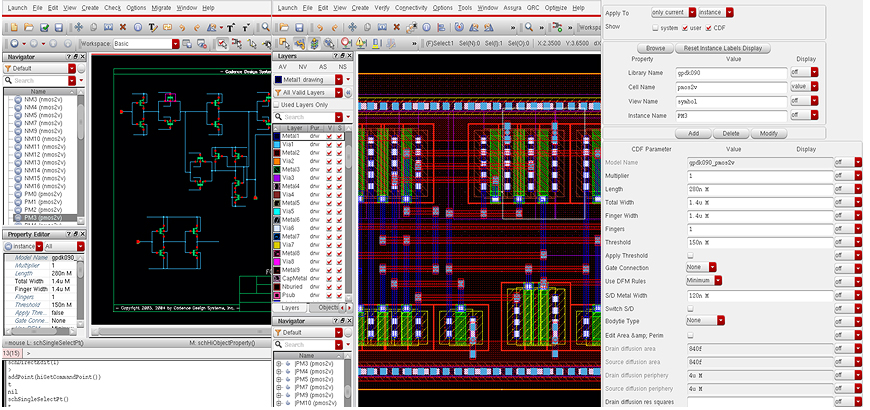

Cadence사 Virtuoso Layout Suite-L

- A. 목적 : Layout

- B. 구분 : Custom IC design Layout분야의 Total solution을 제공

-

C. Supported platform and O/S System

- - Red Het Enterprise Linux (64bit) RHEL 6, RHEL 7

- - SuSE Linux Enterprise Linux (64bit) SLES 10, SLES 11

-

D. 특성 및 기능

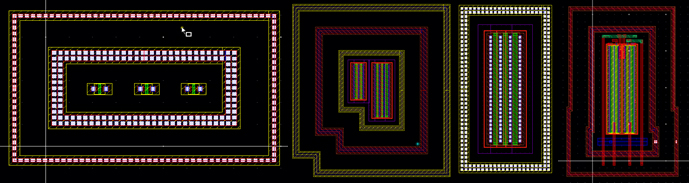

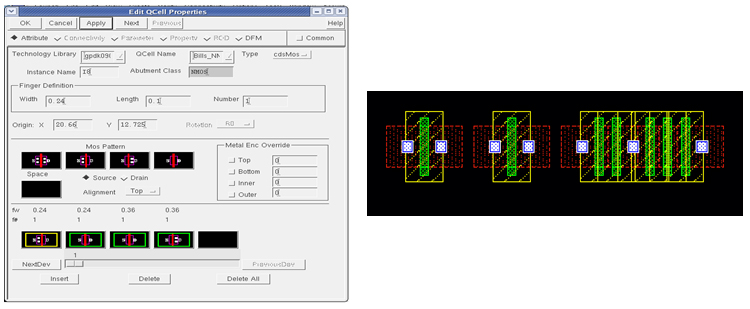

Virtuoso Layout Suite-L은 Foundries에서 PDK로 사용하고 있는 Pcell(Parameterized Cell)을 user가 스스로 제작, Schematic과 Layout에서 사용할 수 있으며, abutment, pin permutation, folding, chaining, cloning등 여러가지의 기능이 포함된 Automates pcell을 Cadence SKILL language에서 지원합니다.

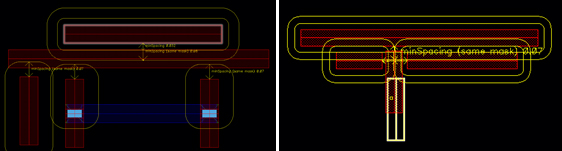

- DRD( Design Rule Driven )와 iPVS( Integrated Physical Verification System )는 Layout 진행시 실시간으로 Check & Guide 기능으로, High Tech로 갈수록 복잡해지는 Rule과 Layout에 꼭 필요한 기능입니다. Design rule을 바로 적용시키므로 낭비되는 Area의 감소는 물론, Chip Size에서의 Margin 역시 늘어나는 결과로 이어집니다.

- FGR(Fluid Guard Rings)는 Click한번으로 ring, rectangle, path, polygon등 여러가지 모양의 guard ring을 만들어주는 기능으로, Cell이나 Block의 shapes에 따라 guard ring을 creating 하며, 모든 shape_editing과 Merge, Tunneling등 많은 option functions으로 편리하게 Substrate와 Well의 bias를 잡아줄 수 있습니다.

- Quick Cell은 user가 width, length, m-factor등을 입력하여 Transistor를 generating하는 기능입니다. Pattern에 따른 shape과 implant enclose를 설정하여 보다 편리하게 Transistor, Resistor들을 generate할 수 있습니다.

-

Virtuoso Layout Suite

- - VLS-L : Manual layout editing tool

- - VLS-XL : Assisted Automated tool

- - VLS-GXL : Full automated tool

- Virtuoso Layout Suite는 3 tiers로 구성되어 있으며, Ease-Of-Use와 Intuitive layout을 위한 Common user interface를 제공하고 있습니다. 이렇듯 Layout의 Place부터 Route까지 Automatic Solution을 이용하여, The highest Technology인 14nm, 16nm 공정을 이끌어가는 Tool입니다.

Cadence사 Assura

- A. 목적 : DRC(Design Rule Check), LVS(Layout Versus Schematic) Physical Verification

- B. 구분 : Cadence 사의 ASSURA는 IC design flow 중 physical layout 을 검증하는 solution을 제공함

-

C. Supported platform and O/S System

- - Red Het Enterprise Linux RHEL 5(32bit), RHEL 6(64bit), RHEL 7(64bit)

- - SuSE Linux Enterprise Linux (64bit) SLES 9, SLES 10

-

D. 특성 및 기능

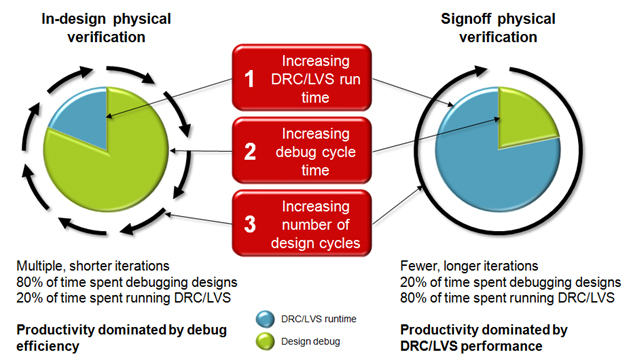

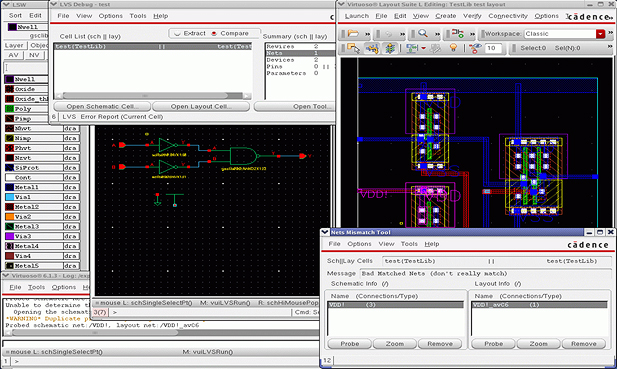

DRC(Design Rule Check)/LVS(Layout Versus Schematic) 검증 작업은 block level physical layout을 진행과 동시에 검증하는 In-design physical verification 과 block design이 완성된 후 top level에서 최종 검증하는 Signoff physical verification 으로 구분할 수 있다. In-design physical verification에서는 physical layout을 진행하면서 수시로 violation이 있는지를 확인하는 과정을 거치게 되며, 실제 DRC/LVS running time 보다는 violation debugging 시간이 많이 차지하고, Signoff physical verification은 debugging time 보다 DRC/LVS running time이 더 많은 부분을 차지하게 된다.

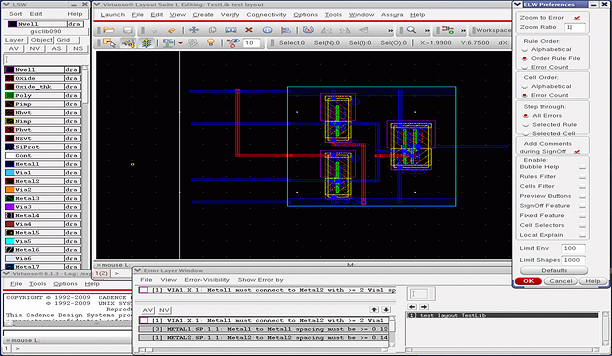

- ASSURA DRC는 Cadence Virtuoso Layout Suite에 integration이 되어 있어 layout 중간에 수시로 physical verification을 진행할 수 있는 User friendly 환경을 갖추고 있으며, error debugging 창을 이용해서 즉시 수정 및 재 검증 가능한 환경을 제공하고 있다.

- ASSURA LVS는 Cadence VSE(Virtuoso Schematic Editor)로 구성한 회로와 Cadence VLS(Virtuoso Layout Suite)로 구성한 physical layout 을 유기적인 환경을 이용하여 LVS를 진행할 수 있으며, LVS error 발생시 소요되는 debugging time을 줄일수 있도록 error를 쉽게 찾아 수정할수 있는 design 상호간 cross probing 기능을 포함한 LVS error 전용 debugging 창을 제공하여 설계자의 실수를 쉽고 빠르게 찾아 수정할 수 있는 환경을 제공한다.

- 이렇게 DRC/LVS 검증이 완료된 design은 Cadence QRCX Extraction 제품과도 유기적으로 연계되어 parasitic extraction시 사용 가능하도록 Cadence design environment 내에서 모든 IC design을 완성할 수 있는 장점을 제공한다.

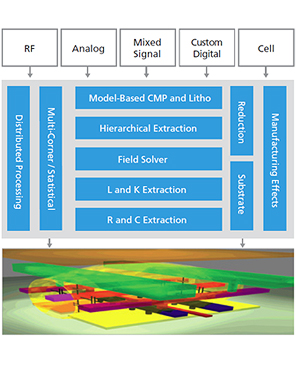

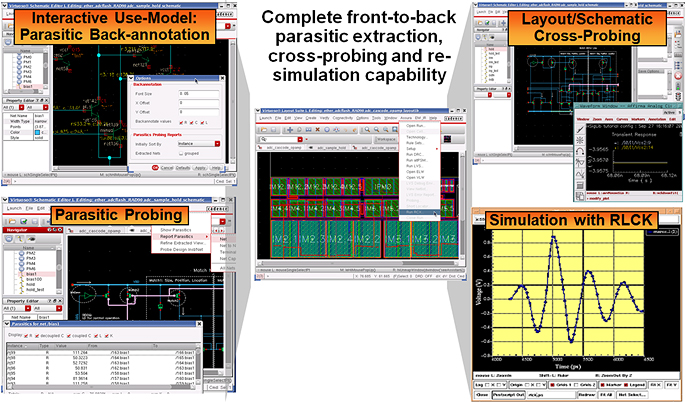

Cadence사 Quantus QRC Extraction

- A. 목적 : Physical Layout에서 Parasitic Extraction

-

B. 구분

Cadence 사의 Quantus QRC Extraction는 IC design flow 중physical layout 을 검증 완료 후 설계자가 의도하지 않는 design 내 기생성분 즉, parasitic을 추출하여 검증하는 solution을 제공함 -

C. Supported platform and O/S System

- - Red Het Enterprise Linux RHEL 5(32bit), RHEL 6(64bit), RHEL 7(64bit)

- - SuSE Linux Enterprise Linux (64bit) SLES 11

-

D. 특성 및 기능

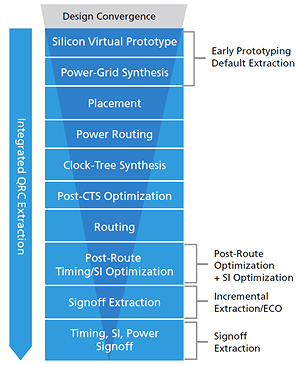

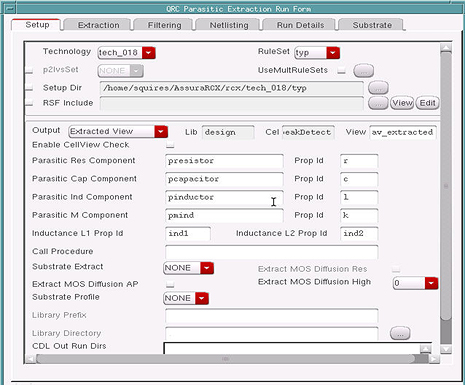

Cadence 사의 Quantus QRC Extraction는 IC design flow 중physical layout 시 설계자가 의도하지 않는 design 내 기생성분이 생기면서 회로 동작에 영향 주게 되는데, 실제 제품 생산을 위한 최종 Mask제작 전 설계자의 의도하지 않은 parasitic 추출 후 parasitic을 포함한 post simulation을 통해 회로 오동작을 미연에 방지하기 위해 사용되며, Cadence Quantus QRC Extraction은 하나의 technology file을 이용해서 Digital 또는 Analog design 모두 사용 가능하다.

-

Figure1 : Enabling in-design in the Encounter digital implementation platform

-

Figure2 : Key functionalities of Cadence QRC Extraction

- Cadence Quantus QRC Extractor는 ASSURA/PVS LVS 검증결과와 연동하여 Quantus QRC extraction 전용창을 통해 설계자 의도를 반영한 av_extracted cellview를 만든 후 ADE(Analog Design Environment)를 이용하여 post simulation을 위한 유기적 환경을 제공하며, 설계자가 직관적으로 사용할 수 있는 GUI(Graphic User Interface)를 제공한다.

- 그리고, 정확한 parasitic 추출과 추출된 parasitic을 이용한 post simulation 결과를 바탕으로 회로 오동작 원인 분석및 오동작 방지를 위한 회로 분석을 위해 Quantus QRC Extraction이 제공하는 parasitic cross probing 기능 또한 설계자들에게 큰 도움이 되며, advance node 공정에서 발생하는 여러 문제점을 파악하여 이미 제품에 반영하여 최신 공정에서도 보다 정확한 결과를 추출하여 회로 오동작을 사전에 방지할 수 있도록 다양한 기능을 제공하고 있다.

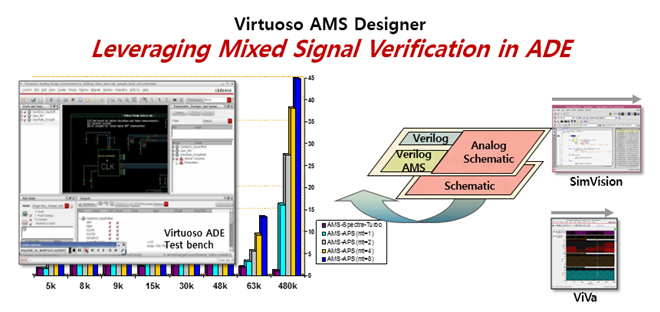

Cadence사 AMS/ APS

- A. 목적 : Simulator

- B. 구분 : Mixed Simulation in Cadence

- C. 특성 : Analog & Digital 이 같이 혼성으로 되어있는 경우 Digital은 NCSIM or irun이 Analog는 Spectre / APS / XPS-MS이 같이 simulation을 돌리면서 연산하는 Simulator

- D. 기능 : Verilog & VHDL, System Verilog등의 다양한 language를 지원함

1. AMS

-

· Performance

- - Analog solver multi-threading support - retaining SPICE accuracy and improving capacity

- - Real value modeling - analog functionality at digital speeds

-

· Usability/functionality

- - Flexible use model - supporting both top-down and bottom-up approach

- - Comprehensive language and cross domain connectivity support - supporting design, modeling and testbench languages

- - Low-power support - ensuring proper handling of power domain and state information

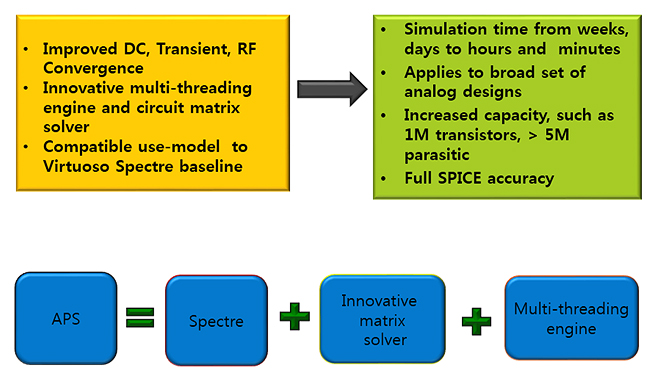

- A. 목적 : Simulator

- B. 구분 : Multi-Threading Simulator

- C. 특성 : 최대 64개의 CPU까지 활용해서 Spectre의 accuracy를 가지고 빠른 연산을 하는 것이 가능합니다.

- D. 기능 : Spectre로 simulation이 가능한 모든 simulation을 APS를 이용해서 빠르게 연산하는 것이 가능하며, ADC, DAC, PLL 등의 block을 빠르게 연산할 수 있는 고유의 algorithm을 내장하고 있습니다.

2. APS

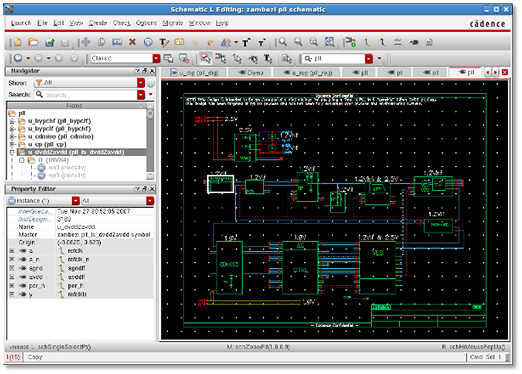

Cadence사 Virtuoso Schematic Editors

- A. 목적 : Schematic Capture, Netlist추출

- B. 구분 : Circuit Entry

-

C. Supported Platform and OS Sytem

- - Red Hat Enterprice Linux (32/64bit) 5,6,7

- - SuSe Linux Enterprice Server (32/64bit) 10,11,12

- D. 특성 및 기능 : Gui에서 회로들을 손쉽게 구현가능

-

E. FAMILY FEATURES AT A GLANCE

- · Modern, familiar, and user-customizable toolbars, icons, pull-down menus, a multi-tab, multi-view design canvas, workspaces, bookmarks, history, search, dockable assistants and more

- · Multi-tab, Multi-view canvas

- · Customizable workspaces

- · Hierarchical schematics

- · Supports the ability to use Verilog-AMS and VHDL-AMS mixed-signal languages, thereby providing a standard way of entering designs regardless of design type. Block representations can be generated from the HDL descriptions, facilitating a system-level approach to IC design

- · Hierarchical cross probing front to back

- · Supports multi-sheet designs and provides the ability to design hierarchically with no limit on the number of levels used.

- · Rapid command execution with user configurable bindkeys and menus

- · Extensive design checking capabilities including custom checks

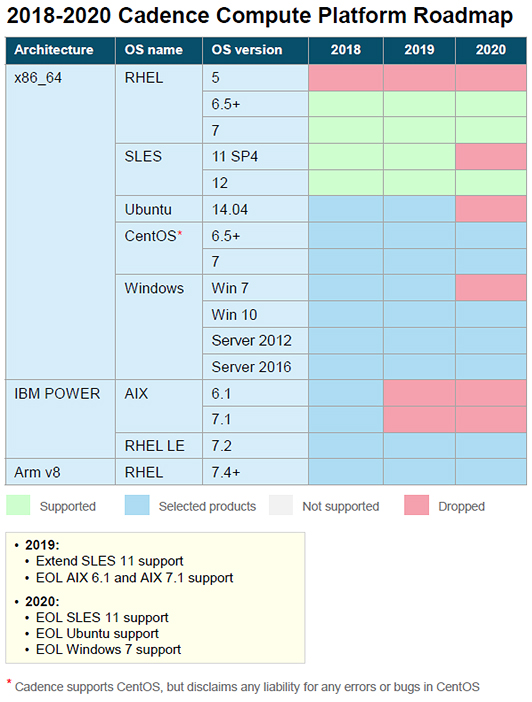

[참고] Cadence Platform Roadmap

-

Cadence Korea, Ltd.

Cadence Korea, Ltd.- Webpage www.cadence.com

- E-mail korea_crc@cadence.com

- Tel 031-728-3114