VCS · Verdi · Spyglass · Synplify · Premier · Design Compiler Family · DFT Product Family · Formality · PrimeTime Prime Power · IC · Compiler · StarRC · IC Validator

Synopsys 사

Synopsys사 VCS

- A. 목적 : Functional Verification (Verilog/VHDL Simulator (X-Prop, UPF-Low Power))

- B. 구분 : Synopsys 사의 VCS는 세계적인 Functional Simulation 및 Verification 툴임

-

C. Supported platform and OS/ System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: 최근 선도적인 디자인을 설계하는 디자이너들은 Synopsys VCS의 Functional Verification Solution에 의존하고 있다. 사실, 32nm 공정 및 그 이하에서는 대다수의 디자인을 VCS를 통해서 검증한다. VCS는 세계적인 반도체 회사 중 Top 20개들로부터 주요 Verification Solution으로써 사용되고 있다. VCS는 고성능의 Simulation Engine과 Constraint Solver Engine, Native Testbench (NTB) 지원, Systemverilog 지원, Verification Planning, Coverage 분석 및 통합 디버그 환경을 제공한다.

VCS의 Multicore 기술은 Multiple Core를 가진 여러 개의 머신들에서 병렬적으로 Design, Testbench, Assertions, Coverage 그리고 디버깅을 할 수 있도록 하므로 검증속도를 2배 빠르게 해줄 수 있다. VCS의 PartitionCompile Flow는 수정된 코드로 인한 Re-Compile시 최대 10배 빠른 Compile Turn Around Time을 달성할 수 있다. 또한, 다양한 검증 툴을 포괄적으로 지원하기 때문에 시뮬레이션 메모리와 Time Profiling, 쌍방향 Constraint 디버깅, Smart Logging 등을 통해 유저로 하여금 빠른 분석이 가능하도록 했다. VCS의 저전력 시뮬레이션과 UPF 지원기능은 Voltage 분석 검증기능을 제공하여 버그를 찾아낼 수 있도록 한다. 기본 내장된 디버깅 기능과 그래픽 환경은 거의 모든 유명한 디자인과 Verification Language를 지원한다. 예를 들어 Verilog, VHDL, Systemverilog, OpenVera, SystemC, VMM, OVM, UTM Methodology 등인데, 이를 통해 VCS는 고성능 디자인 개발을 돕는다.

-

1. Comprehensive Coverage

: VCS는 검증 안정성을 측정하기 위한 고성능의 Coverage 기술을 내장하고 있다. 매우 큰 범위의 Coverage는 Code Coverage, Functional Coverage 그리고 Assertion Coverage와 User-Defined Metrics도 포함한다. 통일된 Coverage는 하나의 Common Database에서 모든 Coverage를 하나로 합치게 되므로 강력한 쿼리들과 쓸모 있는 통일된 Report 생성이 가능하다. 통일된 Coverage Database는 머지 시간을 최대 2배에서 5배 개선해주고, Disk Space는 최대 2배 감소시켜준다. -

2. Advanced Debugging and Visualization Environment

: VCS는 Discovery Visualization Environment (DVE)를 포함하여 가시적인 Full-Featured 디버깅 환경을 제공한다. DVE는 VCS의 디버깅 탐색 기능을 끌어 쓸 수 있도록 설계되었다. 다른 SYNOPSYS 툴과 비슷한 GUI 환경으로 되어 있는데 특히 직관적인 Drag-and-Drop를 통해 검증 데이터에 쉽게 접근할 수 있어서 직관적인 툴 사용이 가능하다.

DVE는 Transaction-Level의 디버그 기능이 있어서 List View와 Waveform View에서 분석과 디버깅이 쉽게 되어 있다. DVE는 Tracing Drivers, Waveform Compare, Schematic View, Path Schematic등의 기능 및 VCD+ Binary Dump Format도 지원함에 더하여 Mixed-HDL (SystemVerilog, VHDL, Verilog) 및 SystemC/C++ 언어 디버깅 윈도우를 통하여 Tracing의 자동화를 도울 것이다. TCL 지원은 당연하며 통합 Command Language가 모든 툴과 Language 그리고 개발 환경에 적용되어 있다.

Synopsys사 Verdi

- A. 목적 : Design Debug & Analysis

- B. 구분 : Verdi는 다양하고 복잡한 설계 환경을 통합하는데 도움을 주며 디지털 설계 디버깅을 위한 플랫폼이다.

-

C. Supported platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: Verdi 시스템은 일반적으로 50% 이상 설계자의 디버그 시간을 단축하며, 설계에 더 많이 집중할 수 있도록 도움을 준다.

- - 독특한 행동 분석 기술을 사용하여 추적 동작을 자동화

- - 추출, 분리, 그리고 유연하고 강력한 디자인 뷰에 관련 로직을 표시

- - 디자인과 테스트 벤치 사이의 상호 작용 동작 표시

Verdi 시스템은 여러 도메인에 걸쳐 원활하고 일관되게 작동하는 단일 솔루션을 제공하여 디버그 프로세스를 통합한다. 이러한 일관성은 사용자가 다른 도구와 언어를 사용해도 새 프로젝트에 이식하는 시간을 절약해 준다.

Timing과 Power에 대한 분석 도구 기능을 포함하고 있으며 STA (Static Timing Analysis) 툴의 Report 파일(SDF)을 불러와 분석할 수 있으며, UPF와 CPF 형식, FSDB 형식을 지원한다.

Synopsys사 Spyglass

- A. 목적 : RTL단계에서의 Design 문제 분석

- B. 구분 : Spyglass는RTL 설계 단계에서 예측 가능한 Lint, CDC, DFT, Constraints, Power, Physical 등의 문제를 미리 검증하여 설계기간 단축과 비용 절감을 위한 Solution을 제공

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: Spyglass는 향상된 알고리즘과 분석 기술을 바탕으로 초기 RTL단계에서 Design에 대한 분석을 완벽하게 수행할 수 있도록 도와준다.

Spyglass는 GUI/BATCH 모드의 환경을 제공하며, GUI에서는 Source Code, Result, Schematic, Help Viewer 등이 제공된다. 이 Viewer들은 서로 간의 Cross Probing을 통해 쉬운 Debugging 환경을 제공한다.

-

Lint

Spyglass Lint는 Simulation, Synthesis 등의 단계에서 발생 가능한 문제를 미리 검증하기 위해 Design Rule Checking을 진행하며, Verilog, VHDL, SystemVerilog 등 여러 format의 RTL를 지원한다. -

CDC

Spyglass CDC는 Asynchronous Clock 간의 Domain Crossing에서 발생할 수 있는 Meta-Stability, Reset Synchronization 등의 문제를 Check 한다.

추가로 Design 내에 CDC를 위해 사용된 장치에 대한 Formal Analysis를 진행하여 Functional Issue(Re-Convergence, Data Loss, FIFO Underflow/Overflow 등) 발생 여부에 대한 검증도 진행한다. -

DFT

Spyglass DFT는 RTL단계에서 Stuck-At-Fault, Transition Fault에 대한 Test Coverage를 Estimation 한다.

Coverage Drop이 발생하는 Point에 대해 Report 하여, Coverage를 높이기 위한 Guide를 준다. RTL 단계에서 DFT 문제를 미리 Fix 하는 것은 Scan-Insertion과 ATPG 단계에서의 불필요한 Iteration을 최소화할 수 방법이다. -

Constraints

Spyglass Constraints는 Synthesis, STA, Layout에 필수적인 SDC를 RTL단계에서부터 Generation, Validation, Managing 할 수 있다. RTL/Nestlist와 SDC의 간의 일치성을 확인하며, 누락되거나 잘못된 Constraints가 있는지를 Check 한다. -

Power

Spyglass Power는 Design에서 소모되고 있는 Dynamic Power/Leakage Power를 Estimation하고, Clock Gating을 통하여 소모되는 Power를 줄일 수 있는 Point를 찾아내어 Design의 Power Saving을 Guide 한다.또한, CPF, UPF를 지원하여 Voltage Domain, Power Domain을 위한 Component들이 올바르게 Implementation 되었는지를 검증한다. -

Physical

Spyglass Physical은 Layout 전에 RTL/Netlist를 이용하여 Layout 상황 예측을 통해, Layout에서의 Congestion 발생 여부를 확인할 수 있으며, Timing Critical Path 및 Physical Area를 예측한다.

Synopsys사 Synplify

- A. 목적 : Logic Synthesis for FPGA

- B. 구분 : Synopsys 사의 Synplify Premier는 전 세계 모든 FPGA의 Synthesis가 가능한 독보적인 합성 툴임

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

-

1. High Performance FPGA Synthesis Tool for All FPGA Vendors

: Synplify Premier는 1992년 자체 개발한 최고의 합성 알고리즘인 BEST (Behavior Extracting Synthesis Technology)를 사용하여 설계자가 생성한 Verilog HDL / VHDL 소스 코드를 바로 게이트 레벨로 변환하지 않고 Behavioral 상태에서 합성한다. 또한, Mixed Language Support가 지원되고 합성결과에 대한 Timing을 분석하기 위한 STA (Static Timing Analyzer)를 자체 내장하였으며, HDL Analyst를 이용해서 Critical Path에 대한 추적과 분석이 쉬워 전 세계 최대의 FPGA 공급사인 Xilinx, Altera 사도 자사의 합성툴보다는 Synplify Premier의 사용을 적극 권장하고 있고, ACTEL 사는 OEM 공급을 체결하여 고객사에 Actel 전용의 Synplify Premier를 공급하고 있다. -

2. 주요기능

- - Proprietary B.E.S.T Algorithms : 최적, 최상의 합성 결과를 위한 고유의 합성 알고리즘.

- - Integrated Module Generation and Mapping : 각종 산술연산에 대한 모듈 생성기를 내장, 각 디바이스에 최적화된 구조로 Mapping.

- - SCOPE Multi-Level Design Constraints : 합성에 필요한 여러 Constraint을 GUI 환경의 SCOPE를 이용해서 쉽고 빠르게 적용.

- - Comprehensive Language Support Language-Sensitive Editor Intuitive Use Model w/ Intelligent Defaults

- - Direct Synthesis Technology : FPGA 별로 전용 Mapper를 가지고 있어서, 해당 FPGA에서 최적의 Primitive Cell을 찾아서 합성.

- - Automatic RAM Interfacing : 이용하는 각 FPGA의 구조와 크기에 맞는 Memory를 합성.

- - Third-Party Tool Integration : 사용하는 FPGA 벤더 툴, 그리고 다른 기타 툴의 활용도를 최대화.

- - Advanced Counter Extraction : 디자인 내의 카운터들을 자동으로 인식해서 추출, 최적의 합성.

- - Advanced HDL Enhancement : Verilog 2001 지원하며, 차기 버전에서는 System Verilog 지원 예정.

- - HDL Analyst : Schematic Viewing 기능과 디버깅 툴.

- - FSM Explorer& Compiler : State Machine 합성.

- - Graphical State Machine Viewer : FSM을 State Machine Diagram과 Table을 이용해서 쉽게 분석.

- - Register Balancing for Pipelined Multipliers and ROMs : Multiplier와 ROM에서의 Pipeline을 쉽게 처리.

- - Probe Point Creation : RTL 소스 코드의 수정 없이 내부 신호를 쉽게 외부 핀으로 Probing .

- - Generic Cross-Probing of Critical Paths : Critical Path에 대한 용이한 분석과 수정을 위해 HDL Analyst (RTL View Schematic Netlist, Technology View Schematic Netlist)와 Text Editor (RTL 소스코드, 합성 결과 Log File, Timing Analysis File)를 이용한 Cross-Probing이 가능.

- - STAMP Support : IP를 이용한 디자인에서 STAMP Model을 이용한 합성과 타이밍 분석이 가능.

- - Mixed Language Design Entry : VHDL과 VerilogHDL 뿐만 아니라 둘이 혼합 사용된 디자인도 합성 지원.

- - Re-Timing : Critical Path에 대한 분석을 통해서 Critical Path에서의 레지스터 재배치를 통해서 각 Path 간의 Delay의 균형을 맞춰서 전체 디자인의 타이밍 성능을 최대화.

- - Automatic Constraint : 스스로 Over Constraint를 사용해서 디자인을 위한 최대 타이밍 성능의 합성결과를 만들어 냄.

- - Multi-point Synthesis : Compile Point를 이용한 다양한 형태의 합성방법과 Incremental 합성까지 지원.

Synopsys사 Design Compiler

- A. 목적 : RTL Synthesis

- B. 구분 : Design Compiler는 Verilog나 VHDL과 같은 HDL (Hardware Description Language) 디자인을 최적화된 게이트 레벨 디자인으로 합성 가능

-

C. Supported platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: DC Ultra는 Synopsys RTL Synthesis 솔루션에서 핵심으로, Power Compiler, Design Ware, PrimeTime, DFTMAX를 포함하고 있다. DC Ultra를 통해 오늘날의 고성능 설계를 위한 타이밍, 면적, 파워, 테스트를 동시에 최적화할 수 있다. 또한, DC Ultra에는 RTL 합성 단계에서, 최종 Layout의 타이밍, 면적, 파워의 정확한 예측을 통해 최종 물리적 설계를 더욱 보장할 수 있는 Topographical 기술을 포함하고 있다.

Topographical Technology : Topographical Technology는 Wireload Model을 기반으로 하는 통계적인 Net의 근사치 대신에, 실제 Net의 Resistance와 Capacitance의 정확한 예측을 통해, Post-Layout의 타이밍, 면적, 테스트, 파워의 상관관계를 알 수 있다. 이는 Physical 설계의 전문기술이나 합성 모델의 변경 없이, 합성과정에서 RTL 설계자가 실제 설계 문제를 해결할 수 있고, 배치 및 배선을 위한 더 나은 결과물을 얻을 수 있다.

Advanced Arithmetic Optimization : DC Ultra는 타이밍, 면적, 파워 면에서 더 나은 품질을 달성하기 위해 혁신적인 경로 최적화 알고리즘을 사용한다. DC Ultra는 HDL의 연산 트리를 확인하고, Carry 전파의 실행과 면적의 영향을 최소화하기 위해 Carry save 알고리즘 기술을 사용하여 최적화한다.

Powerful Critical Path Synthesis : DC Ultra는 초고속의 중요한 타이밍 경로에 대해 합성하는 과정에서 다양한 최적화 알고리즘을 사용한다. 타이밍 중심의 구조조정, 매핑 및 게이트 레벨 최적화를 통해 더욱 나은 전반적인 타이밍 기반 구조로 변화시키고, 중요 경로의 부하를 줄이기 위해 로직을 중복으로 복제하여 부하 분산을 통한 중요 경로의 타이밍을 개선한다. 또한, DC Ultra는 면적, 타이밍, 파워 향상을 위해, 중요 경로 상의 디자인 부분을 자동으로 Ungroup 및 Cell의 그룹화를 수행한다.

Register Retiming : Register Retiming은 레지스터가 포함된 디자인에서 적용되는 기술로서, 면적의 영향은 최소화하며 타이밍을 최적화하기 위해 Logic Boundary 상에서 레지스터를 이동하여 Sequential Logic을 최적화한다. 또한, 성능의 요구사항을 충족하며 면적을 줄이기 위해, 순수한 조합 회로에 파이프 라인 레지스터를 삽입할 수 있다.

Synopsys사 DFT Compiler

- A. 목적 : Design For Test (DFT)

- B. 구분 : DTF Compiler 는 Scan Chain을 삽입하여 테스트 분석 가능

-

C. Supported platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: DFT Compiler는 Synopsys의 설계를 위한 TEST 종합 솔루션을 제공한다. DFT 컴파일러는 설계자가 RTL의 효과적인 테스트 기능 분석을 수행할 수 있도록 하며 필요한 경우 DRC 위반을 자동으로 수정한다. 또한, 높은 품질의 결과를 위해 DFT MAX 와도 호환할 수 있다.

주요 특징

- - Standard Scan 합성

- - 반복된 설계 및 주기 단축

- - 초기 설계 시 테스트를 위한 비용 감소 및 생산성 향상

- - 저전력, 멀티 전압 지원

- - Design Compiler에 포함되어 제공되며 결과를 ICC에서 사용 가능

- - Tetra MAX에 사용될 STIL Protocol 파일 자동 생성

-

Test DRC& Auto Fix

전통적인 설계 과정에서 테스트와 관련된 문제는 초기에 발견하기 어려우며 게이트 수준에서의 문제는 전체 칩에 문제가 될 수 있다. TestDRC 는 설계자가 테스트에 적합한 RTL 을 설계할 수 있도록 도와주며 이를 통해 DFT 합성이 원활히 이루어질 수 있도록 한다. DRC 후 Violation이 발생할 경우 설계자는 AutoFix 기능을 사용하여 자동으로 테스트 로직을 삽입하여 해결할 수 있도록 한다.

Synopsys사 Formality

- A. 목적 : Equivalence Checking (EC)

- B. 구분 : Formality는 Equivalence Checking Tool로 RTL 와 NETLIST 사이의 등가 검사를 진행한다.

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: Synopsys Formality의 주요 목적은 예상하지 않은 합성 결과를 발견하는데 있다. 디자인을 시뮬레이션 할 경우 많은 Input 벡터를 사용해야 하며 디자인이 클수록 더욱더 많은 벡터를 고려하여 시뮬레이션 해야 한다. Synopsys Formality 툴은 RTL 와 Netlist (DC, ICC)의 등가검사(Equivalence Checking)기능을 포함하고 있으며, 큰 디자인의 경우에도 테스트 벡터를 사용하지 않고 신속하게 검증할 수 있는 장점이 있다.

- • 분산 검증을 내장한 성능상의 이점 확장

- • 검증된 자동화된 지침을 사용하여 사용자 설정 감소

- • 흐름 기반 그래픽인터페이스를 통한 검증 생산성 확대

- • 높은 완성을 달성하기 위해 DC Ultra 연동

- • 저전력 설계를 위한 EC 기능 포함

- • IEEE 1801(UPF) FLOW 지원

-

그래픽 사용자 인터페이스 제공

Formality는 흐름 기반 그래픽 사용자 인터페이스를 제공한다.

사용자는 메뉴의 흐름에 따라 손쉽게 툴을 사용할 수 있으며 대부분의 설정은 자동으로 입력된다.

참조(Reference)디자인 실행(Implementation)디자인을 비교하기 쉽도록 보여주며 자동으로 불필요한 Path를 줄여 사용자가 내용을 확인하기 쉽도록 하고 있다. 또한, Formality는 Power Compiler와 호환할 수 있으며 Power-Up, Power-Down, Multi-Voltage 등에 대한 확인이 가능하다.

-

Input Formats

- • Synopsys DC, DDC, Milkyway

- • IEEE 1800 SystemVerilog

- • Verilog-95, Verilog-2001

- • VHDL-87, VHDL-93

- • IEEE 1801 Unified Power Format (UPF)

-

Guided Setup Formats

- • Synopsys V-SDC

- • Formality Guide Files (SVF)

Synopsys사 PrimeTime

- A. 목적 : Pre/Post Static Timing Analysis

- B. 구분 : Synopsys 사의 Prime Tim은 가장 높은 신뢰성을 제공하는 Static Timing 분석 툴로서 가장 진보된 Timing Signoff 툴임

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: PrimeTime은 합성 후 진행하는 Gate-Level Static Timing Analysis 부분에서 업계 Standard가 되어 있다.

28nm 공정 및 그 이하 공정에서 PrimeTime을 활용하여 만든 수많은 칩이 본 툴의 STA 성능과 정확성을 증명한다.

PrimeTime Static Timing Analysis는 StarRC Parasitic Extraction과 연동하여 검증하는 것이 업계의 Golden Standard이다.

PrimeTime의 장점은 Timing Signoff와 Timing Analysis를 위한 탁월한 개발 환경이다. 진보된 On-Chip Variation 검증 기술과 우수한 Delay Calculation, 툴 사용의 편리함, 유저 중심의 GUI, 쉬운 모델링의 장점들은 PrimeTime이 ASIC Vendor와 Foundry들 사이에서 가장 널리 사용되는 Signoff 툴이 될 수 있도록 했다.

-

1. Comprehensive Timing Analysis

PrimeTime의 매우 방대한 연산 능력은 복잡한 디자인도 Signoff 할 수 있도록 한다. 복잡한 Constraint의 동시 적용 및 Delay Reporting 기능을 통해서 동시에 여러 타입의 Timing Check 및 Design Rule Check를 진행할 수 있기 때문에 사용자들은 설계 중인 디자인의 모든 특성을 확인할 수 있으므로 신뢰성 있는 분석 및 Signoff가 가능하다. -

2. Golden Delay Calculator

PrimeTime 안에 내장된 RC Delay Calculator는 Parasitic 정보와 Composite Current Source (CCS) 라이브러리를 사용하여 정확하게 Cell Delay와 Interconnect Delay를 계산한다. 광범위한 Delay Calculation과 Parasitic이 반영된 Reporting 능력은 설계자들이 쉽게 문제를 찾아내고 해결할 수 있도록 하므로 생산성이 향상된다. 진보된 Delay Calculator는 전압과 온도도 반영하는데 이는 Multi-Voltage 분석 기능을 제공함과 동시에 PVT 정보를 담은 큰 라이브러리들의 유지를 하지 않아도 되도록 한다. -

3. Advanced On-Chip Variation (AOCV) Analysis

65nm 공정과 그 이하에서 On-Chip Variation 관련하여 일반적으로 부여한 부정확한 Margin은 Over-Design, 성능 저하 등의 결과를 가져오곤 했다.

PrimeTime의 AOCV 모델링 기능은 디자인에 Margin을 추가하는 방법을 통해 신뢰도 높은 OCV 분석기능을 제공한다. 각각의 Path의 Logic Depth와 Location을 분석하여 정확한 Factor들을 뽑아내어 시뮬레이션한다. 결과적으로 과도한 Margin 적용을 하지 않게 되고 Timing Violation 수는 줄어들게 되어 Over-Design의 확률이 낮아진다.사용자들은 정확한 타이밍을 갖춘 신뢰성 높은 디자이너가 될 수 있을 것이다. -

4. Distributed Multi-Scenario Analysis (DMSA)

최근에는 최소 사이즈 구현이 당연시되고 있는데, 작은 사이즈 구현 때문에 역효과 적으로 발생하는 Physical 현상에도 불구하고 좋은 칩을 만들어 내기 위해서는 많은 시나리오 적용이 필수적이다. 칩 디자인의 검증을 하기 위해서는 동작 모드, 전압, 온도, Process Corner를 표현하는 다양하고 독립적인 시나리오들이 필요하다.

많은 시나리오 분석 결과를 검증하고 관리하는 것은 PrimeTime의 DMSA 기능으로 쉽고 편리하게 할 수 있는데 이 기능은 다양한 시나리오에 대하여 동시에 Setup, Distribute, Run 그리고 ECO까지 할 수 있도록 함으로써 Turnaround Time이 감소하도록 한다. -

5. Additional Features in PrimeTime

- - Advanced Modeling Capabilities with Interface Logic Models (ILM) and Extracted Timing Models (ETM)

- -UPF (Unified Power Format) Support

- -GUI Enabling Timing Analysis and Design Visualization using Schematics, Histograms, Tables, and Tree Graphs

- -Save and Restore

- -What-if ECO analysis

- -Exception and Constraint Analysis for Debugging

- -ASIC Vendor Signoff and Foundry Support

- -Extensive Support of Industry-Standard Input and Output

- -File Formats

Synopsys사 PrimePower

- A. 목적 : accurate dynamic and leakage power analysis

- B. 구분 : PrimePower 는 cell 기반 설계의 full-chip 전력 소모를 정확하게 분석하는 전력 분석 솔루션으로 SoC 설계자가 적시에 설계 최적화를 할 수 있도록 정확한 전력 분석 보고서를 제공한다. 또한 PrimeTime 툴과 통합함으로써 타이밍과 신호 무결성 분석 솔루션을 확장하여 정확한 동적 및 누출 전력 분석을 제공.

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: PrimePower 툴은 vector-free, vector-based peak power 그리고average power 분석을 제공하며 Vector는 Value Change Dump (VCD), Fast Signal Database (FSDB), 또는 Switching Activity Interchange Format (SAIF) 형식의 RTL- 또는 gate- 레벨 시뮬레이션 결과이다.

PrimePower는 Synopsys 데이터베이스 형식(.db) 라이브러리에서 회로 연결, switching activity, circuit connectivity 및 셀 레벨 전력 동작 데이터를 기반으로 설계의 상세 전력 프로파일을 구축한다. PrimePower는 또한 비선형 전력 모델(NLPM) 라이브러리를 지원하고 cell-level에서 회로에 대한 전력의 거동을 계산하며, chip, block, cell-level 수준에서 전력 소비량을 보고한다.

전력 분석이 끝나면 power map과 파형을 포함하여 GUI(Graphical User Interface)에서 설계 데이터와 분석 결과를 볼 수 있다.

-

1. Vector-Free Dynamic Power Analysis

Vector-Free Dynamic 전력 분석은 시뮬레이션에서 switching date를 기다리지 않고 전력 분석을 수행할 수 있으며, PrimeTime 툴의 정확한 timing windows를 사용함으로써 vector-free analysis는 설계 초기 전력 소비량이 가장 높은 블록을 더 빨리 식별하여 전력 분석을 할 수 있게 한다. -

2. Time-based Power Analysis

시간에 대한 정확한 전력 분석을 위해 시간에 따른 RTL 또는 gate-level simulation activity에 기초한 분석을 지원한다.PrimePower는 각 event의 전력 소비량을 계산하기 위해 event-driven 알고리즘을 사용하며, Time-based 전력 분석을 위해 PrimePower는 전력 보고서뿐만 아니라 detailed average 및 peak power 파형을 생성한다. -

3. Cycle-accurate Peak-power Analysis

PrimePower는 cycle-accurate peak 전력 분석 모드에서 전력을 계산하기 위해 RTL switching activity data를 사용하며 event당 전력을 정확하게 계산하여 clock-cycle resolution에서 전력 파형을 생성한다.설계에서 최대 전력 소비량이 발생하는 주기를 결정하기 위해 결과를 사용한다.

Synopsys사 IC Compiler

- A. 목적 : Auto Place and Route

- B. 구분 : IC Compiler는 Logical &Physical Design 설계를 위한 디자인 계획, Physical Synthesis, Clock Tree Synthesis, Routing 기능의 결합을 통해 완벽한 Netlist-to-GDSII 또는 Netlist-to-Clock Tree Synthesis 디자인 솔루션을 제공

-

C. Supported Platform and OS Sytem

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: IC Compiler는 Galaxy Design Platform에 속하는 종합적인 배치 및 배선 시스템이다.

IC Compiler는 멀티코어 지원, 강력한 Design Planning 능력, 설계 단계의 완벽한 통합과 빠른 디자인 융합을 통해서 동종 최강의 Placement, CTS, Routing 기능을 제공한다.

-

Design Planning

: IC Compiler는 Die Size의 최소화와 최적의 세부적인 배치가 가능한 빠른 디자인 탐색 기능을 바탕으로 Flat &Hierarchical 디자인 계획을 할 수 있다. 또한, 전력 네트워크 합성 및 분석을 통해서 IR Drop의 요구사항에 충족하는 Power Network를 만들 수 있다.

-

Early Analysis Facilitates Faster Design Convergence

-

Thermal Map Based on PNS and IR Drop

-

-

Multi-Corner Multi-Mode (MCMM)

: MCMM솔루션을 이용한 Placement, Clock Tree Synthesis, Routing 및 최적화 변환은 크고 복잡한 칩들의 TAT (Turn Around Time)를 극적으로 줄인다. -

QoR (Quality of results)

: IC Compiler는 타이밍, 면적, 파워, 신호 무결성, 라우팅 가능성 및 제조 등의 전체적인 측면을 고려한 QoR을 제공한다.

Relative Placement (RP) reduces Power and improves Routability

-

Zroute Technology

: IC Compiler에서 Zroute 기술은 가장 빠르게 TAT를 전달하기 위하여, 멀티코어 컴퓨팅 플랫폼을 최대한 활용하는 고급 라우팅 알고리즘과 멀티 스레딩 기능을 사용한다. -

Ease of Use

: IC Compiler는 직관적 명령어를 사용하여 사용 편이성을 증가시켰다. IC Compiler의 GUI는 사용자 친화적이고, 디자이너가 모든 설계 단계에서 문제를 해결할 수 있는 기능을 사용하기 쉽게 제공한다. GUI는 빠른 분석, 시각화, 디버깅 및 복구 기능을 사용할 수 있다.

Critical Path Cross-Highlighting Enables Faster Debugging

-

Flow :

-

1. Design Setup : IC Compiler Flow의 첫 번째 단계로 Synthesis Data와 Physical Date를 IC Compiler에 읽어 들이는 단계이다.

Design Setup

-

2. Design Planning : IC Compiler는 기본적인 Floor planning과 평면 및 계층적 설계를 위한 프로토 타입 기능을 제공한다. (불완전하거나 문제가 있는 net 처리, 자동적인 칩 사이즈 측정, 블랙박스 모듈 지원, 매크로 및 셀들의 신속한 배치, Prototype Global Routing 분석, 핀 할당 및 개선, Power Network Synthesis)

-

Pin Placement

-

Macro Placement

-

Power Network Synthesis

-

-

3. Placement : 배치 및 최적화를 통한 Congestion과 Setup Timing을 개선할 수 있다.

-

Path Slack Visual Mode

-

Global Route Congestion Map

-

-

4. CTS (Clock Tree Synthesis) : 디자인의 Clock에 대한 최적화 및 Hold Timing의 개선과 Clock Net에 대한 배선과정을 수행한다

-

Clock Tree Visual Mode

-

Latency Abstract Clock Graph

-

- 5. Route : 설계자는 Global Routing, Track Assignment, Detail Routing을 통해 자동적인 배선이 가능하며, ECO Routing을 이용하여 Net의 변경 및 재연결이 가능하다.

-

6. Chip Finishing : IC Compiler는 칩 가공 및 칩 제조 과정에서 발생하는 공정 설계 문제를 해결하기 위해, 설계 흐름의 여러 단계를 걸쳐 제조 및 수율 성능을 위한 설계 기능을 제공한다.

(Tap Cell 삽입, Antenna Violation 수정, 추가 Via 삽입, Wire 길이 및 Via 수 최적화, Shielding Nets, Filler Cell 삽입 등)

-

1. Design Setup : IC Compiler Flow의 첫 번째 단계로 Synthesis Data와 Physical Date를 IC Compiler에 읽어 들이는 단계이다.

Synopsys사 StarRC

- A. 목적 : Physical Layout Parasitic Extraction

- B. 구분 : Synopsys 사의 StarRC는 Parasitic Extraction 쪽에서 Industry Gold Standard 툴임

-

C. Supported Platform and OS Sytem

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: StarRC는 Digital, Custom IC 칩 구현 및 Signoff 검증에 필수적인 Parasitic Extraction에 있어서 매우 높은 정확성과 고성능을 갖춘 차세대 툴이다. StarRC는 Sub-Femto 단위에서도 정확하게 값을 뽑아내는데, 나노미터 공정에서 발생하는 Interconnect Parasitic Effect 및 디바이스를 정확하고 세세하게 모델링하기 때문에 정화도 높은 결과를 제공할 수 있다. 진보된 모델링 기술과 정확성은 Embedded Rapid3D 공정처럼 엄청난 정확성이 요구되는 곳에서도 보장된다. Multicore Distributed Processing 기술은 기능은 툴 구동 하드웨어의 Physical 자원의 부담을 덜어주며 Multi-Corner Extraction 기능은 Multi Corner 및 Multi 시나리오 고려를 하나의 Process로 처리할 수 있도록 해주는 매우 유용한 기술이다.

-

1. Multicore Processing

StarRC의 멀티 코어 기술은 가용한 서버 하드웨어 자원을 최대한 효율적으로 사용하기 위해 일반 Commercial 한 컴퓨팅 매니지먼트 소프트웨어와 연동이 잘되도록 만들었다. StarRC의 멀티 코어 기술은 손쉬운 컴퓨팅 자원할당과 각 Core에게 자동으로 디자인 Partitioning을 하여 쪼개주는 기술, 안정적인 Load Sharing 및 자동 Failure 복구 기능도 함께 포함한다. -

2. PrimeTime Binary Interface

SoC 디자이너에게 있어서 Parasitic Netlist Size와 Timing Signoff Analysis Runtime은 매우 큰 고민이다.

수백만 개의 Net으로 구성된 디자인을 Extract 한 Parasitic Netlist Size는 매우 커서 Parasitic Read와 분석을 하는 데 매우 큰 영향을 줄 수 있다. StarRC는 SBPF (Synopsys Binary Parasitic Format)이라는 유일하고 Compact 한 Binary Parasitic 제공하는데 이는 PrimeTime에서 혼용할 수 있다. SBPF Binary Interchange Format은 SPEF처럼 Connection 정보에 전기적 특성까지 Capture 하지만 Primetime의 정확성을 유지하면서도 최대 15배까지 Parasitic Netlist Size를 줄여주어 최대 80%까지의 Runtime 감소 효과를 보여준다. -

3. Custom AMS Design Platform Integration

StarRC는 Synopsys의 Galaxy Custom Designer Mixed-Signal Implementation 시스템과 Cadence의 Virtuoso Analog Design Environment와 연동을 할 수 있다. StarRC와 Galaxy Custom Designer는 Open Access 인터페이스를 도입하여 일반적인 Data Flow를 사용하는 시놉시스의 개발 환경에 익숙한 사람들이 편히 사용할 수 있도록 한다. 한편, Virtuoso 환경을 위해서 StarRC는 Netlisting과 시뮬레이션을 위해 Open Acess 또는 Cadence DFII Database Parasitic View를 만드는데, 이는 ADE에서 사용되는 Common Netlisting Interface와 호환된다. StarRC는 Parasitic View 또는 Schematic View에서 Parasitic을 뽑을 수 있도록 한다. Parasitic Prober는 Schematic과 Parasitic View 사이에서 Parasitic View나 지점간 저항, 전체 Net Capacitance, Net-to-Net Coupling Capacitance 그리고 Cross-Probing의 기능을 제공한다. 또한, Probing 된 Parasitic 값을 ASCII Report File로 뽑아내는 기능과 Parasitic View에서의 Total Capacitance 값을 관련된 Schematic View에서 주석으로 보여줄 수 있는 기능도 보유하고 있다.

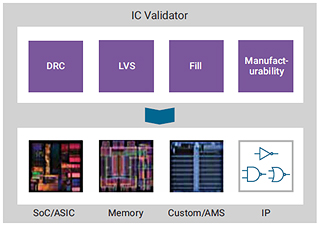

Synopsys사 IC Validator

- A. 목적 : physical verification – DRC or LVS checking

- B. 구분 : IC Validator는 모든 메인스트림 및 고급 프로세스 노드에 대해 성능 확장성과 광범위한 런셋 지원을 제공하는 포괄적인 물리적 검증 사인오프 솔루션

-

C. Supported Platform and OS Sytem

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: IC Validator는 100억개 이상의 트랜지스터와 800mm2보다 큰 die sizes를 몇 시간 이내에 DRC signoff를 deliver 하며, The Design Rule Checking (DRC) and Layout Versus Schematic (LVS) 물리적 검증 엔진은 수백 개의 CPU 코어에 걸쳐 거의 선형적인 확장성을 통해 결과 도출 시간을 상당히 단축한다.

IC Validator는 설계 내 물리적 검증을 위해 IC Compiler II place and route 시스템과 완벽하게 통합된다. -

High Performance and Scalability

IC Validator는 advanced node에서 물리적 검증의 capacity 및 performance requirement를 해결하기 위해 가용 하드웨어의 확장성과 효율적인 활용을 위해 설계되었다.

멀티 스레딩은 현대 멀티코어 CPU의 실행 시간을 크게 단축시켜 수백 개의 CPU 코어가 있는 distributed computing network를 통한 거의 선형적 확장성은 대부분의 물리적 검증 작업을 하룻밤 사이에 완료할 수 있게 한다.

-

Comprehensive Physical Signoff Solution

IC Validator는 입증된 고성능 및 포괄적인 signoff 물리적 검증 솔루션으로 DRC, LVS, Programmable Electrical Rule Checks (PERC), dummy fill, Design For Manufacturing (DFM) 기능을 포함한 물리적 검증 도구 제품 군을 제공한다.

-

(유)시높시스 코리아

(유)시높시스 코리아- Webpage www.synopsys.com

- E-mail kor_feedback@synopsys.com

- Tel 02-3404-2700