2020 IDEC Tool소개 :: Synopsys 사

Custom Compiler · Laker · Hspice · Finesim Pro 및 SPiCE2 · CustomSim · Custom WaveView · VCS AMS · SiliconSmart · TCAD Sentaurus · Virtualizer · Saber Simulator

Synopsys사 Custom Compiler

- A. 목적 : Custom Design

- B. 구분 : Custom Compiler는 full-custom analog, custom digital 그리고 mixed-signal IC 설계를 위한 최신의 solution이다.

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: Custom Compiler는 Synopsys Custom 설계 플랫폼의 중심으로 설계 항목, 시뮬레이션 관리 및 분석, custom layout editing 기능을 제공한다. FinFET process 기술의 가장 까다로운 요구사항을 다루도록 설계되어 legacy 툴 사용자에게는 업계 최고의 생산성, 성능 및 사용 편의성을 제공한다.

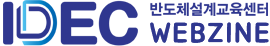

Design Entry and Simulation

Custom Compiler는 mixed-signal 설계, debug, 시뮬레이션 관리, 분석 및 보고를 위한 강력한 기능을 갖춘 design entry 및 시뮬레이션을 위한 고생산적인 환경을 제공하며, Schematic entry는 automatic wiring, symbol generation, 파라미터의 on-canvas editing 등을 통해 간소화되었다.

Custom Compiler의 schematic 편집기에는 설계 계층 전반에서 전원공급 확인 및 inherited connection을 위한 전력 도메인 분석기 그리고 설계 전반에서 신호 추적을 위한 net tracer와 같은 유용한 디버깅 보조장치가 포함되어 있으며 또한 schematic간 변화를 보고하는 설계 비교 기능도 포함되어 있다.

Text and schematic 뷰는 mixed-signal 설계를 자유롭게 결합할 수 있고 Verilog를 위한 a language-sensitive 편집기가 포함된다. 시뮬레이션 결과의 탐색, 교차 탐색 및 back-annotation은 schematic and text 뷰에 모두 사용 가능하며, mixed-signal 분할 및 시각화를 위한 parameterizable interface element와 같은 강력한 기능도 있다.

Custom Compiler는 Synopsys의 회로 시뮬레이터인 HSPICE, FineSim, CustomSim과 통합되며, 그 밖의 simulator 와도 통합이 가능하며, 시뮬레이션 지원은 코너 설정, 멀티플 테스트벤치, 몬테카를로 및 기타 분석을 위한 GUI가 포함된다. Custom Compiler는 배치모드 시뮬레이션을 위한 grid-based job distribution 및 모니터링을 지원하며, 검증 실행을 위한 TCL 스크립트가 가능하다.

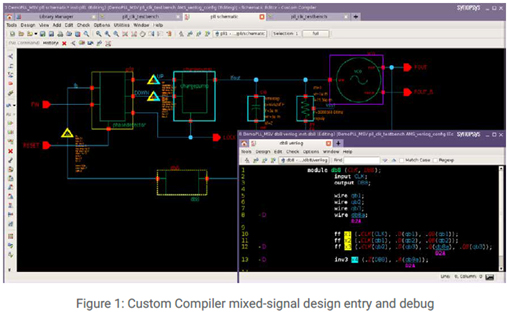

Custome Compiler는 Synopsys의 Custom WaveVies와 통합하여 파형의 시각화 및 후처리 기능을 제공하며, 데이터 시각화 기능으로는 차트 작성, 통계 분석, 히스토그램 및 scatterplot을 포함하고 또한 HTML기반의 보고 기능을 제공하여 설계 검토를 위한 시뮬레이션 결과를 제공한다.

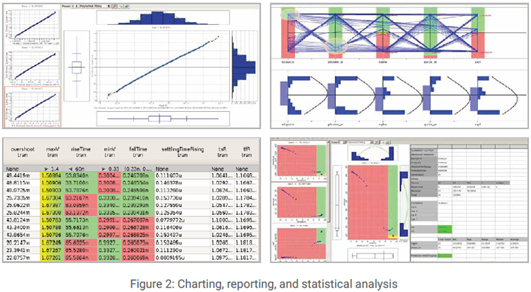

Custom Layout Editing with Visually-Assisted Automation

Custom Compiler는 users need의 polygon 편집 기능의 빠르고 사용자 친화적인 버전을 포함하며, Visually-assisted automation(VAA) flow로 레이아웃 팀의 생산성을 향상시킨다.

VAA는 특히 어려운 FinFET 기반 설계의 경우 2~10배 더 나은 생산성을 제공하는 것으로 입증된 layout effort를 줄이기 위한 혁신적인 접근법이며, layout 설계자에게 익숙한 graphical use model을 통해 requiring manual constraint entry 없이 자동화를 제공한다. 이는 Custom Compiler를 사용하면 일상적이고 반복적인 작업이 별도의 설정 없이 자동으로 처리된다.

Synopsys사 Laker

- A. 목적 : Physical Layout Design

- B. 구분 : Synopsys 사의 Laker는 IC Design 등의 Physical Layout 설계분야의 Solution을 제공

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 5, 6, 7

- - CentOS Linux (64bit) 5, 6, 7

-

D. 특성 및 기능

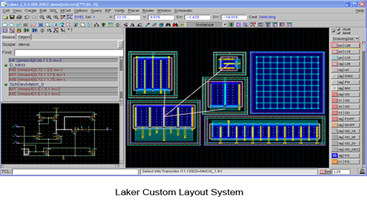

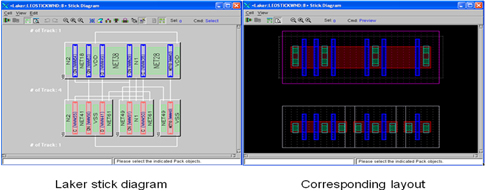

: Laker는 아래의 그림과 같이 Netlist Schematic Layout Data를 한 화면에서 상호작용하는 작업을 할 수 있으며 Device Generation의 기술을 통해 DRC/LVS의 검증 시간과 PCell Scripting의 시간을 최소화할 수 있다.

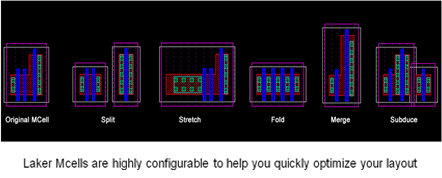

Magic Cell (MCell™)은 별도의 Scripting 없이 Window 기반으로 Transistors, Resistors, Capacitors, Contacts/Vias 그리고 Guard Rings의 Device들을 간단하게 생성하여 Multiple-Gate Transistors, Guard-Rings, Contact Arrays, Inter-Digitized Resistors and Capacitors와 같은 복잡한 형태로 손쉽게 만들 수 있는 기능을 제공한다.

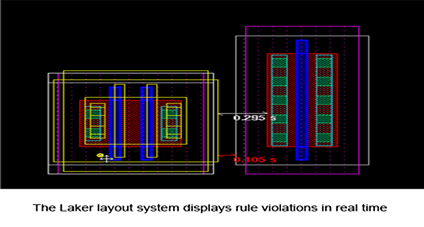

Rule-Driven Layout은 Realize, Place, Route, Edit의 Layout 작업 중 DRC/LVS를 실시간으로 검증하는 기능으로 추후의 DRC/LVS에서 소요되는 시간을 단축해준다.

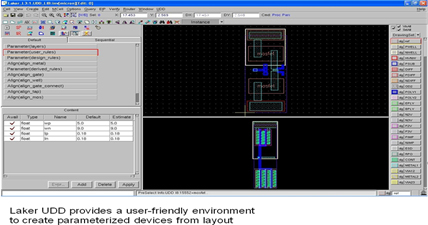

User-Defined Device (UDD)는 Spiral 같은 설계자가 직접 설계하기 복잡한 Device들을 Parameter화 된 Device의 형태로 생성하여 사용할 수 있는 기능이다. PCells과 비슷하지만 Scripting은 물론 Window 상에서도 만들 수 있기 때문에 더욱 손쉽게 사용할 수 있다.

Schematic-Driven Layout (SDL)은 Schematic, Netlist, Layout을 동시에 한 화면에서 각각의 Browser를 통해 Rule-Driven Layout, Realize, Place, Route and Edit 등이 가능하도록 제공하는 기능이다.

Stick Diagram Compiler는 MCell에 기반을 둔 Device 생성과정에서 TR의 Floor-Plan을 설정해 주는 기능이며 이외에도 Abstraction, Swap, Merge, Move, Spilt, Align Gate의 기능들이 포함되어 있어 Design Rules, Connectivity 나 Parameter Value와 관계없이 Symbol Level에서 Device를 Optimize 할 수 있다.

Laker 는 3rd Party에서 설계한 Data의 호환을 위해 GDSll, OASIS, LEF/DEF, CDL, EDIF, Verilog를 In/Output 할 수 있으며, DRC / LVS를 위해서 Calibre® 와 Hercules™ 를 Integration 하여 사용할 수 있도록 지원하고 있다. 또한, Tcl (Tool Command Language)를 완벽하게 제공함으로써 Tool Customization, Database Query 그리고 Layout Creation 등을 편리하게 이용할 수 있다.

Synopsys사 Hspice

- A. 목적 : Circuit SPICE Simulation

- B. 구분 : Synopsys 사의 Hspice는 모든 Application의 설계 및 검증을 위한 Solution을 제공

-

C. Supported Platform and O/S System (HSPICE)

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

- - Microsoft Windows 7, 10 (64bit)

-

D. 특성 및 기능

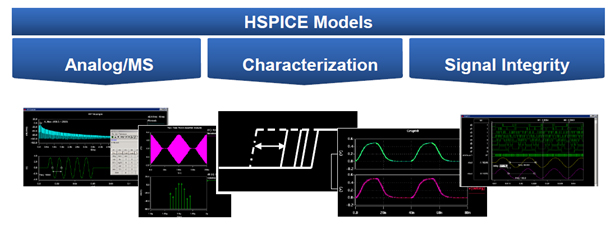

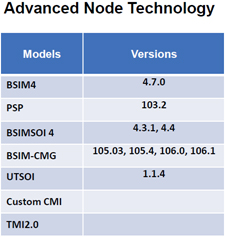

: Hspice는 다양한(Analog, RF, Mixed) 설계 및 공정에 걸쳐 입증된 솔루션으로 특성은 아래와 같다.

- • Glden Accuracy – Best Silicon Correlation

- • Most widely Adopted – Reference Simulator at 9/10 top Foundries

- • Boroadest Application – IC, Package, Borad, Backplane

- • Continuos Innovation –Signal Integrity, Multi-Core, Foundry Modeling

멀티코어 시뮬레이션이 가능하여 더욱 빠른 시뮬레이션이 가능하다.

Synopsys사 CustomSim

- A. 목적 : FastSPICE Simulation

- B. 구분 : Synopsys 사의 CustomSim은AMS 설계 및 검증을 위한 Solution을 제공

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능 :

CustomSim은 다양한 설계 및 공정에 걸쳐 입증된 솔루션으로 특성은 아래와 같다.

- • CustomSim (XA) Simple to Use

- • FastSPICE Performance &Capacity

- • SPICE-like Accuracy

- • Support for HSPICE, Eldo & Spectre Inputs

- • Adopted by leading customers in Analog, Memory, Custom Digital and SoC Applications

파운드리에서 인증한 HSPICE 모델을 제공한다. FastSPICE를 위한 최적화된 모델이며, 멀티코어 시뮬레이션이 가능한 구조이다.

Fastest Digital 엔진과 FastSPICE 엔진을 결합하여 시뮬레이션 속도를 향상시켰다.

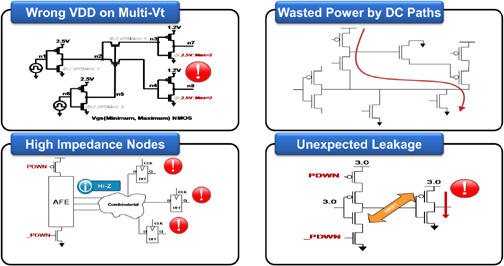

저전력 혼합 신호 검증이 가능하며 정확한 시뮬레이션을 보장할 뿐만 아니라 디지털 블록을 통한 누설 전류를 포함한 전류 흐름을 확인할 수 있다.

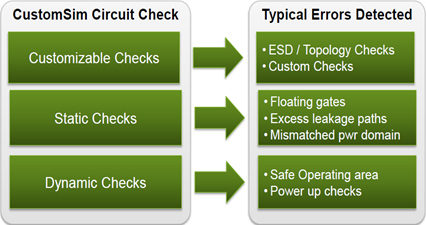

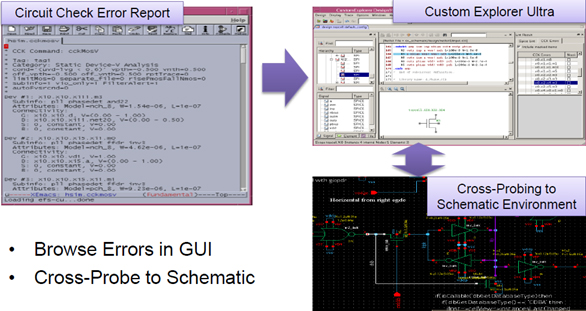

CustomSim은 회로 레벨의 시뮬레이션도 지원하며, 에러 감지 기능도 가지고 있다.

시뮬레이션 결과 및 에러는 Custom Explorer를 통해 확인할 수 있다.

시뮬레이션 결과 및 에러는 Custom Explorer를 통해 확인할 수 있다.

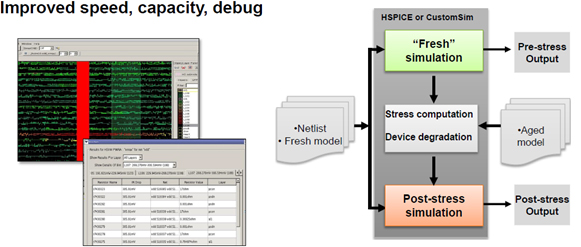

회로의 신뢰성도 확인을 위한 EM/IR 분석 및 MOS Device Aging 확인도 가능하다.

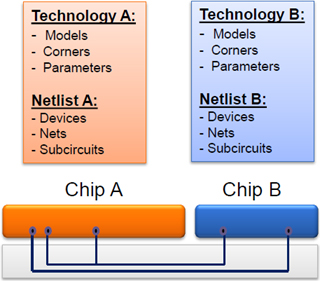

CustomSim은 Multi-Tech 시뮬레이션도 가능하다.

Synopsys사 Finesim Pro 및 SPICE2

- A. 목적 : full SPICE and FastSPICE simulation engines

- B. 구분 : Custom 설계 플랫폼의 integral part로 full SPICE 및 FastSPICE 시뮬레이션 엔진이 내장 된 고성능 회로 시뮬레이터

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

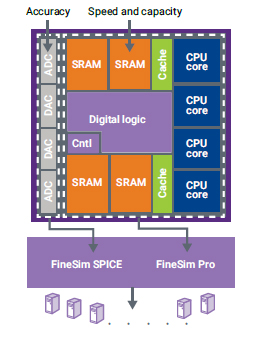

: FineSim은 DRAM / SRAM / 플래시 메모리 설계뿐만 아니라 크고 복잡한 아날로그 회로의 시뮬레이션에도 매우 적합한 코어 가속 회로 시뮬레이터이며, 설계자가 기존 솔루션의 overhead 없이 mixed-signal SoC를 기능적으로 검증할 수 있는 first single executable product 이다.

Features

- single executable에서 정확성과 성능의 조합은 크고 mixed-signal 설계를 매우 정확한 SPICE와 FastSPICE solving 기술로 시뮬레이션 할 수 있게 하여 전체 설계 검증 프로세스에서 속도와 정확도 균형을 완벽하게 제어를 제공한다.

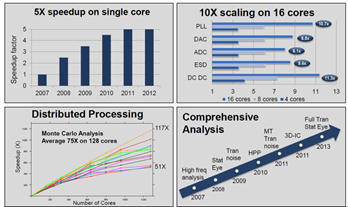

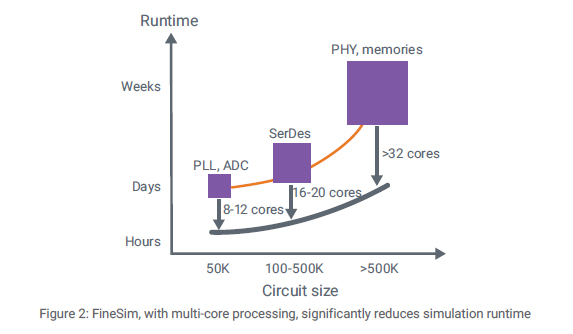

- Multi-core/multi-machine 시뮬레이션은 매우 큰 복잡한 시스템(10M+ transistors)에서 silicon-accurate 결과를 제공하고 이 혁신적인 기술은 성능과 용량 모두를 위한 linear scaling 제공하고 multiple core를 넘어 true SPICE 시뮬레이션을 가능하게 한다.

- advanced SPICE와 FastSPICE solvers를 통해 탁월한 성능을 제공하고 single core 시뮬레이션의 런타임을 3~10배 까지 향상시키며, multi-core 시뮬레이션에서 성능은 코어당 선형적으로 확장되며 경우에 따라 20~30배 이상으로 증가할 수 있다.

- PLL, ADC, SerDes, power management, charge pumps, memory를 포함하여 일반적으로 simulation closure challenge를 보여주는 모든 아날로그, mixed-signal, 메모리, custom digital 및 SoC 설계에 대해 silicon-accurate 결과를 달성한다.

FineSim Pro vs. FineSim SPICE

FineSim은 FineSim Pro 및 FineSim SPICE 도구의 두 가지 제품으로 구성되며, 두 제품 모두 옵션 세트뿐만 아니라 동일한 바이너리 및 실행 파일을 공유한다.

FineSim Pro는 mixed-signal SoC의 설계 및 분석에 가장 적합한 full-chip circuit-level simulator이며, 설계자에게 정확도와 속도 균형을 최대로 융통성 있게 제공하는 완전한 FastSPICE 엔진과 full SPICE 엔진이 포함되어 있다.

FineSim SPICE는 single matrix solver와 linear scaling 및 true SPICE 정확도를 갖춘 multiple CPU/machines (multi-CPU기술)에서 SPICE 매트릭스를 해결할 수 있는 고유한 기능을 가진 true SPICE 엔진이다. 이 SPICE 기술은 PLL, ADC, charge pump 및 기존 SPICE의 어려운 회로와 같은 sensitive 아날로그 블록에 매우 적합하다.

Synopsys사 Custom WaveView

- A. 목적 : Waveform Viewer and Simulation Post-processing Tool

- B. 구분 : Custom WaveView는 아날로그 또는 디지털 시뮬레이터에서 시뮬레이션 결과를 읽고 뷰 간 완전한 변환을 가능하게 하는 full analog 그리고 mixed-signal display및 분석 환경이다.

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 5, 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

- - Microsoft Windows 7, 8, 10 (64bit)

-

D. 특성 및 기능

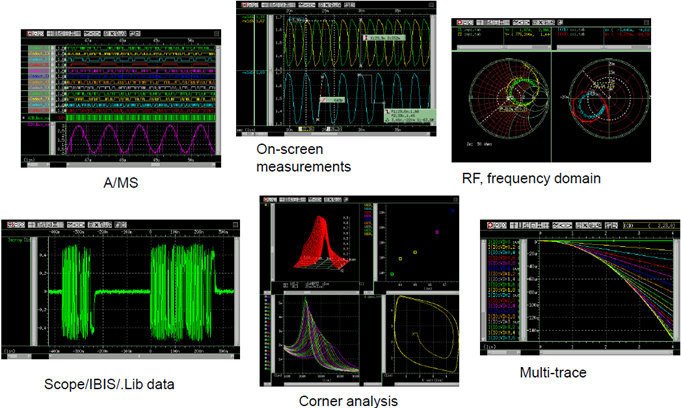

: Waveform Viewing과 Analysis에 사용되며, 대용량의 데이터(GB)를 처리할 수 있으며, 매우 빠른 데이터 로딩, 화면 스크롤, 줌 기능이 포함되어 있다. 또한, 시간 및 주파수 도메인 디스플레이 및 광범위한 측정 및 표시를 할 수 있다.

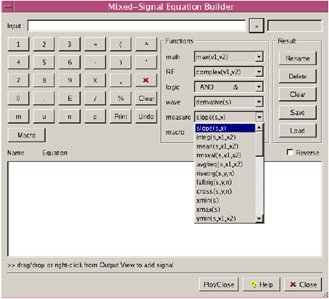

Custom WaveView에는 Equation Builder가 포함되어 있으며, 28개의 수학 연산자 함수, 20개의 RF 기능, 10개의 로직 기능, 27개의 파형 함수, 36개의 측정 기능을 가지고 있다.

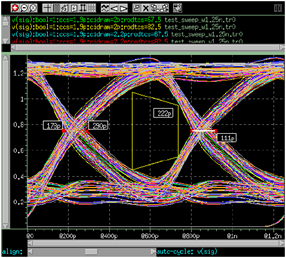

Advanced Toolbox로 Eye Diagram, ADC 설계 Toolbox, FFT, Jitter 측정이 있다.

또한, Laker, Virtuoso, Custom Designer, JEDAT과 함께 Schematic Cross-Probing이 가능하다.

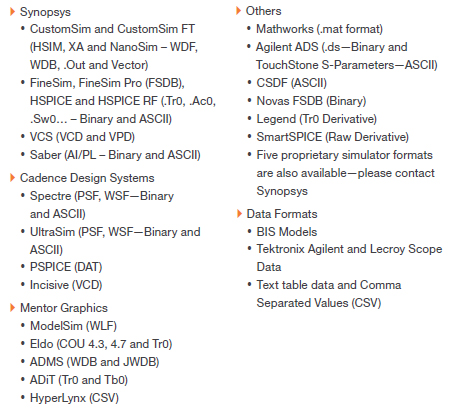

Custom WaveView는 45개가 넘는 포맷을 지원한다.

Custom WaveView로 확인한 Waveform은 Text, SPICE PWL, WDF, VCD, M-File (Matlab)로 추출이 가능하다.

Synopsys사 VCS AMS

- A. 목적 : Mixed-Signal Verification Solution

- B. 구분 : VCS AMS는 VCS 기능 검증과 Synopsys의 CustomSim Fast SPICE 시뮬레이터를 통합한 mixed-signal 검증 솔루션으로 보다 빠른 mixed-signal SoC regression 테스트를 위해 동급 최고의 성능과 용량을 결합한 첨단 기능 및 저전력 검증 기술을 제공.

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

: VCS AMS는 UVM 방법론에 대한 아날로그 확장과 함께 기능 및 저전력 검증을 위한 첨단 기술을 기본적으로 통합함으로써 compute farms 간에 병렬로 실행할 수 있는 범위 기반, 제한된 무작위 testbench를 신속하게 개발할 수 있어 전체적인 regression 테스트 비용을 절감할 수 있다.

-

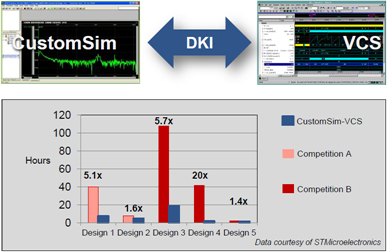

1. Performance

VCS AMS는 고성능 아날로그 및 디지털 시뮬레이션 엔진의 독점적 통합으로 트랜지스터 수준의 정확도로 동급 최고의 성능을 제공하며, CustomSim의 FastSPICE 엔진을 통합한다. -

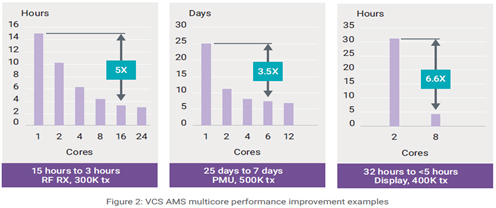

2. Multicore Technology

VCS AMS는 FastSPICE 엔진에서 멀티코어 시뮬레이션 기술을 지원함으로써 검증 처리량이 훨씬 높아 트랜지스터 수준의 정확도로 확장 가능한 mixed-signal regression testing이 가능하다.

-

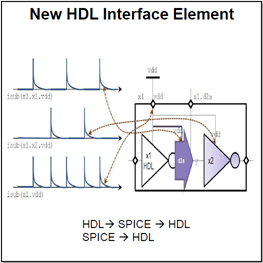

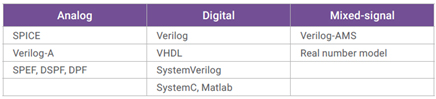

1. Flexibility

VCS AMS는 SystemVerilog, Verilog, VHDL, Verilog-AMS 및 SPICE를 위한 언어 지원으로 abstraction level과 설계 계층을 혼합할 수 있는 다양한 사용 모델을 제공하며, 포스트레이아웃 시뮬레이션은 SPF, DSPF 및 SPEF 형식을 통해 지원된다

VCS AMS는 상위 구성에 아날로그, 디지털 또는 혼합 신호뿐만 아니라 그러한 구성에 대한 계층적 수준도 제공함으로써 복잡한 설계 아키텍처를 완전히 가능하게 한다.

-

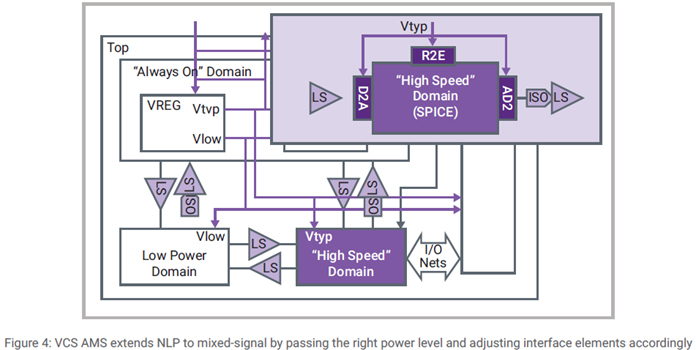

2. Low-power Verification

VCS AMS는 mixed-signal 설계를 위해 UPF를 지원하는 native low power(NLP) 기술을 확장함으로써 종합적인 mixed-signal 저전력 검증 솔루션을 제공한다. 또한 디지털과 아날로그 사이에 전압 레벨을 전달하면서 interface element는 전력 설계 의도를 정확하게 모델링하기 위해 자동으로 삽입되며 이는 오류가 발생하기 쉬운 프로세스를 자동화하고 저전력을 위한 system-level 솔루션을 제공한다.

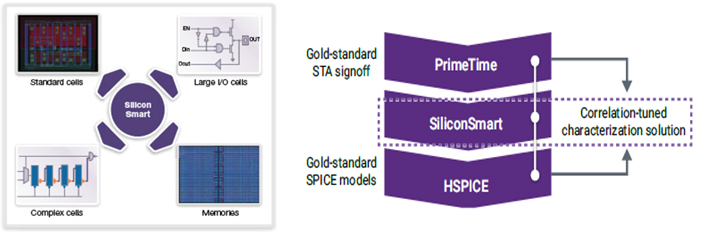

Synopsys사 SiliconSmart

- A. 목적 : Standard 및 IO 등 Library Cell 의 characterization

- B. 구분 : SiliconSmart 는 Standard cell 및 I/O cell 등을 characterization 하여 합성 및 place-and-route, 타이밍 검증등에 활용할 수 있도록 관련 파일을 제공

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

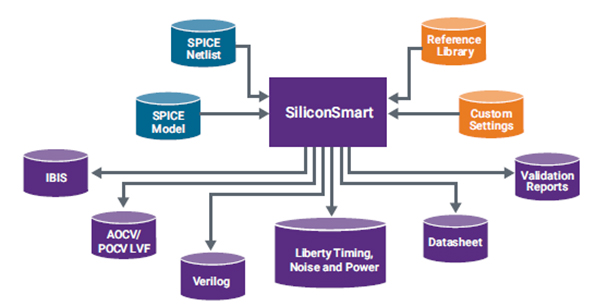

D. 특성 및 기능

: SiliconSmart 는 라이브러리를 characterization 하여 설계자가 원하는 형태로 디지털 설계를 진행할 수 있도록 기본 데이터를 제공한다. 정확한 동작을 위해서는 많은 코너를 검증해야 하고 공정사에서는 지속적으로 SPICE 모델을 업데이트하고 있으므로 설계자는 Cell 을 characterization 하여 사용할 경우 효과적으로 설계를 진행 할 수 있다.

-

Inputs

- - SPICE transistor-level netlist

- - Differential inputs and outputs

- - Multiple voltage supplies

- - User-specifiable complex load networks

- - Characterization of multiple electric modes per driver

-

Outputs

- - Library (.lib)

- Non-linear delay model (NLDM)

- Non-linear power model (NLPM)

- CCS timing, powerm noise, variationaware

- Compact CCS

- ECSM timing, power, statistical

- AOCV

- POCV

- - Verilog

- - VHDL

- - IBIS I/O models

- - Library (.lib)

-

Supported SPICE Simulators

- - HSPICE

- - FineSim

- - Cadence Spectre

- - Mentor Graphics Eldo

Synopsys사 TCAD Sentaurus

- A. 목적 : Process & Device Simulation

- B. 구분 : Synopsys 사의 TCAD는 반도체 제조 공정 및 디바이스 특성 확인의 Solution을 제공

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

-

D. 특성 및 기능

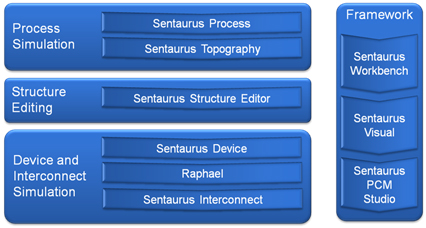

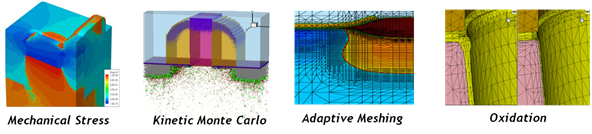

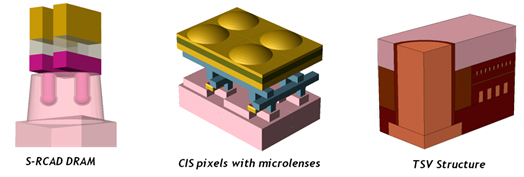

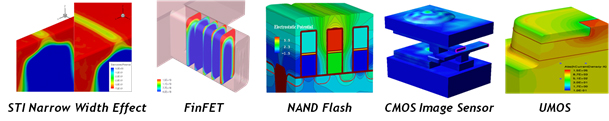

: TCAD는 아래의 그림과 같이 여러 Product로 구성되어 있다.

-

- Sentaurus Process Simulator

범용의 다차원(2D/3D) 공정 시뮬레이터로 통합 3D 형상 모델링 엔진을 포함하고 있으며, Advanced 물리적 모델이 포함되어 있다.

• Advanced Physical Models

- – Analytic and Monte Carlo Implantation

- – Diffusion: Laser/Flash Annealing, Kinetic Monte Carlo

- – Mechanical Stress

- – Oxidation

- – Geometric Deposition and Etching

-

- Sentaurus Structure Editor

형상 작업을 하기 위한 Product로써 사용하기 쉬운 GUI로 되어 있고, 스크립팅 언어도 사용 가능하며, 기하학적 모델링에도 사용할 수 있다.

-

- Sentaurus Device Simulator

범용 다차원(2D/3D) 소자 시뮬레이터로 Full 3D Meshing 엔진을 포함하고 있으며, 실리콘 및 화합물 반도체의 시뮬레이션에 사용할 수 있다. 그리고 넓은 범위의 Advanced 물리적 모델이 포함되어 있다.

• Wide Range of Advanced Physical Models

- – Strained Silicon Mobility Enhancement

- – Quantization and Random Doping Effects

- – Non-Volatile Memory Operation

- – Raytracing and Maxwell FDTD Solver

-

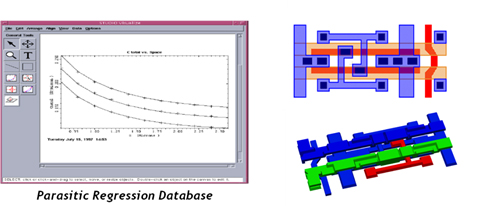

- Raphael Parasitic Extraction

Capacitance와 Resistance의 표준 Interconnect Field Solution으로 기생 Database를 자동 생성해주고, LPE Rule의 교정에도 사용된다.

-

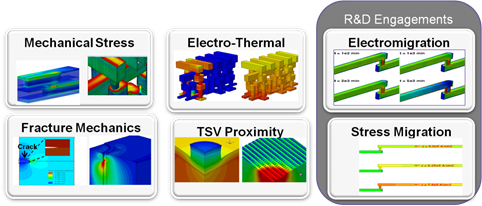

- Sentaurus Interconnect

BEOL 및 TSV의 신뢰성 분석을 위해 사용하며, GDSII 인터페이스 또는 프로세스 에뮬레이션 언어로부터 유연하고 사용하기 쉬운 구조를 생성할 수 있다. Mechanical Stress, Electro-Thermal and RC Analysis를 위한 포괄적인 모델을 포함하고 있다.

-

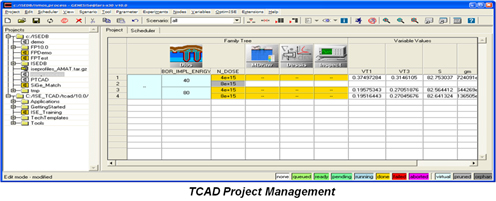

- Sentaurus Workbench

TCAD 프레임워크 환경에서 프로젝트 관리를 하기 위한 것으로 실험의 설계 및 최적화를 할 수 있다.

-

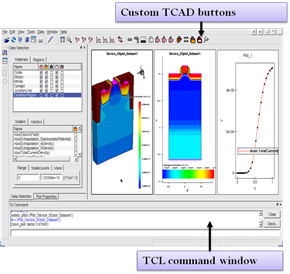

- Sentaurus Visual

TCAD 데이터를 시각화해주는 것으로 향상된 GUI를 제공하며, 강력한 스크립팅 기능이 포함되어 있고, Tcl 스크립트 액티브 커맨드 라인 창을 제공한다. 밴드 다이어그램 및 오버레이, 플롯을 만들기 위한 특수 버튼을 제공한다.

-

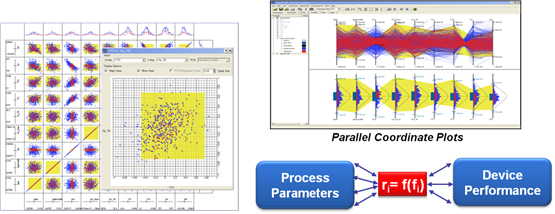

- Sentaurus PCM Studio

Process Compact Models (PCM) 기반 표면 반응 시뮬레이터로 공정 변수 및 장치 성능의 상관관계를 확인할 수 있으며, 제조 제어에 사용할 수 있다.

Synopsys사 Virtualizer

- A. 목적 : SoC Architecture Exploration & Validation and S/W Development

- B. 구분 : Synopsys 사의 PA-MCO는 SoC Architecture Level의 H/W and S/W 개발 환경 제공

-

C. Supported Platform and OS Sytem

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

-

D. 특성 및 기능

1. Platform Architect MCO

2. Hardware-Software Partitioning and Optimization of Multicore Systems

Platform Architect with Multicore Optimization (PA-MCO)는 Architecture 설계 초기에 End-Product Application의 Task-Driven Workload Model들을 만들 수 있도록 해준다.

일반적인 Task Model들은 Task-Graph라 불리는 응용프로그램의 System C 성능모델을 쉽게 구성할 수 있도록 한다.

Task-Graph의 사용한 병렬 응용프로그램 작업의 성능은 가상처리장치(Virtual Processing Unit : VPU) 작업기반의 Traffic Generator에 Mapping 된다.

Simulation과 작업의 분석은 Application을 사용하기 전, 최고의 시스템 성능을 위한 최적화에 H/W 및 S/W의 Partitioning을 가능하게 한다.

Task-Graph는 트래픽 생성기의 Trace-Driven과 함께 Memory Subsystem의 성능 최적화와 연동을 위한 트래픽 생성기 작업기반을 재사용할 수 있게 한다. -

3. Interconnect and Memory Subsystem Performance Optimization Using Trace-Driven Traffic Generation

PA는 최적화 및 Backbone SoC 연동의 성능향상과 Global Memory Subsystem과 연관된 Architecture Design의 개선에 중점을 두고 있다.

Dynamic Application의 Workload는 트래픽 생성기를 사용하여 모델링을 하며, 소프트웨어를 사용하기 전에 시스템 성능의 조기측정을 가능하게 한다.

Simulation Sweeping은 성능 데이터의 매개변수 수집을 가능하게 하며, 설계구성 전체에 대한 트래픽 시나리오를 검토할 수 있게 한다.

시각적 분석을 위한 강력한 Tool은 성능저하의 Bottleneck 이나 근본 원인을 결정하는데 있어Graphical Transaction Tracing 및 통계적 분석관점을 제공하며, 시스템 성능이 독립적 혹은 복합적 변수의 설정인지에 대한 Sensitivity를 확인할 수 있다. -

3. Hardware/Software Performance Validation Using Processors Models and Critical Software

설계모델들의 성능확인 후, Cycle-Accurate 프로세서모델들을 추적기반 및 작업기반의 Traffic 생성기를 대신해 개선할 수 있다.

이는 설계모델들의 유효성을 인증하는 중요한 소프트웨어로 사용될 수 있다.

시각화된 소프트웨어와 하드웨어의 분석관점에서 성능의 측정을 위한 독창적인 System-Level Visibility를 제공하여 최종목적에 맞는지를 확인하도록 해 준다.

-

4. Virtual Prototype Creation with Fully Functional Model

Fully Functional Model인 TLM2 Model을 이용하여 RTL이 준비되기 전에 Model Based SoC Platform을 Creation 할 수 있는 환경을 제공한다. 이를 통해 Early Stage에서 가상의 Virtual Prototype을 만들어 S/W 개발 및 분석을 위한 Platform으로 사용할 수 있다. 또한, 기존의 H/W Based의 S/W 개발 환경과는 다르게 Debugging 및 S/W 개발자들에게 개발 환경을 배포하는 것이 빠르고 쉬워진다. -

5. Early Enable S/W Development with Analysis and Debugging

TLM2로 구성된 Virtual Prototype은 H/W 개발과 동시에 S/W 개발을 가능하게 하여 전체 SoC 개발 Time to Market을 줄여줄 수 있을 뿐 아니라 H/W와 S/W 간의 Interoperating Analysis를 가능하게 하여 Design Iteration을 줄여줄 수 있다.

Synopsys사 Saber Simulator

- A. 목적 : Multi-domain and mixed signal simulator

- B. 구분 : 설계자에게 multiple physical domain(electrical, magnetic, mechanical, thermal, hydraulic 등등) 사이의 상호작용을 시뮬레이션, 분석, 검증을 할 수 있는 기능을 제공.

-

C. Supported Platform and O/S System

- - Red Hat Enterprise (64bit) Linux 6, 7

- - SUSE Linux Enterprise (64bit) 11, 12

- - Windows 7, 10 (64bit)

-

D. 특성 및 기능

: 설계자는 Advanced 분석 및 modeling capabilities로 설계 최적화 및 견고한 설계를 수행하고 어떤 시스템의 가상 프로토타입에 대한 failure effect를 분석할 수 있다.

-

Saber Benefit:

- - 싱글 시뮬레이션 환경을 통한 모든 견고한 설계 분석의 효율적인 실행

- - 30,000개 이상의 behavioral과 characterized model에 의해 지원되는 가상 시스템 설계를 빠르게 생성

- - grid computing으로 계산 집약적인 통계 분석을 수행

-

(유)시높시스 코리아

(유)시높시스 코리아- Webpage www.synopsys.com

- E-mail kor_feedback@synopsys.com

- Tel 02-3404-2700