iPDK

IDEC은 설계 환경의 다변화를 위하여 Interoperable Process Design Kit (iPDK)개발과 iPDK를 이용한 칩 설계 환경을 구축하였습니다. 새로운 개발 환경의 경험을 통해 설계자들은 좀 더 폭넓은 설계 능력을 갖게 될 것입니다

iPDK 구성 및 특징

IDEC에서 개발한 iPDK는 기존의 설계환경에 더하여 IDEC이 보유한 다양한 Tool의 활용을 위하여 개발되었습니다. Synopsys의 Custom Designer 에서 사용이 가능한 iPDK는 아래 그림과 같이 구성되어 있습니다. 기존의 PDK를 사용할 때와 유사한 인터페이스가 제공되므로 사용시 이질감이 크지 않으며 Schematic 설계부터 Post Layout Simulation까지 진행할 수 있기 때문에 MPW 참여자들이 부담 없이 사용이 가능합니다.

iPDK 개발공정

- 매그나칩/SK하이닉스 180nm 공정

- 매그나칩/SK하이닉스 350nm 공정(제작 중)

iPDK 구성도

iPDK를 활용하기 위한 EDA Tool 리스트

- Synopsys CustomDesigner

- Synopsys CustomExplorer

- Synopsys Hspice

- Synopsys PyCellStudio

- Mentor Calibre

- CustomDesigner는 원활한 Calibre Interactive Tool의 사용을 위해 J-2014.12 이상의 버전을 권장합니다.

- 상기 명시된 툴 설치 방법은 IDEC 홈페이지의 EDA Tool 설치 가이드를 참고하시기 바랍니다. (바로가기)

iPDK 사용 및 다운로드 방법

완성된 iPDK는 공정사의 레이아웃 정보 및 공정 파라미터들을 담고 있으므로 홈페이지를 통한 다운로드는 불가합니다. NDA를 작성하고 MPW 에 참여하는 분들은 IDEC FTP 서버에 접속하여 다운로드 받은 뒤 Synopsys Custom Designer 를 연동하면 사용이 가능합니다

Custom Designer User Guide

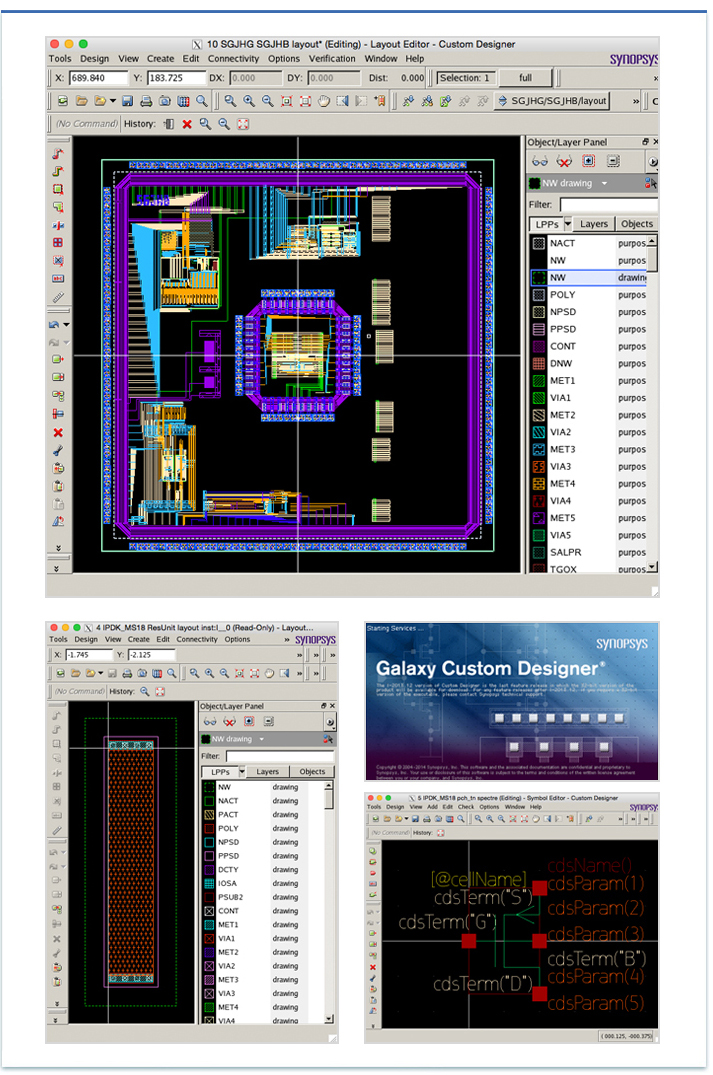

iPDK를 활용한 칩 디자인 모습

주의 사항

본 iPDK는 IDEC이 자체 제작한 것으로, 공정사에서 제공하는 PDK와 동일한 성능을 목표로 제작되었습니다. 다만, 다소 차이는 있을 수 있다는 점을 설계자께서 인지해주시기 바라며 설계 과정 중 발생된 문제점이나 개선사항을 IDEC에 알려주시면 빠르게 조치하겠습니다.

iPDK 담당 연구원

- 선혜승 연구원(smkcow@idec.or.kr), 김연태 연구원(ytkim@idec.or.kr)