| IP개요 |

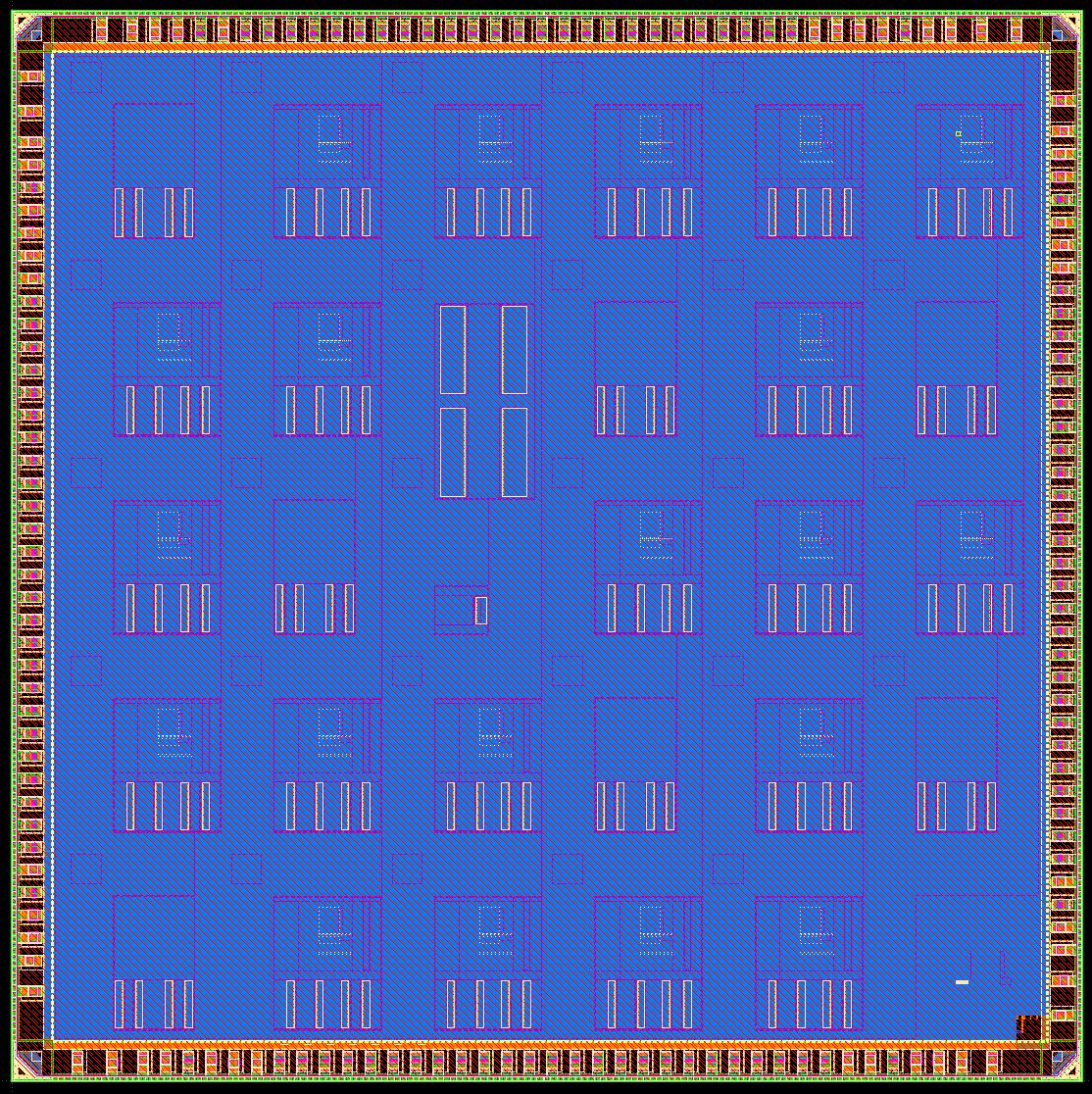

이 IP는 정적 랜덤 액세스 메모리 (SRAM) 컴퓨팅-인-메모리 (CIM)을 생성할 수 있는 자동화된 컴파일러에 적합한 SRAM-CIM 빌딩 블록을 연구하기 위한 설계를 포함하고 있습니다. CIM은 전통적인 폰 노이만 아키텍처에서 경험하는 에너지 소비 및 대역폭 제한에 대한 해결책으로 등장하여 인공 지능 및 딥 러닝과 같은 데이터 집약적인 작업을 효율적으로 처리합니다. 빠른 액세스 속도와 에너지 효율성을 갖춘 SRAM은 CIM에서 데이터 처리를 위한 적합한 메모리 구조로 탐색되어 왔습니다. 그러나 대부분의 기존 SRAM CIM 아키텍처는 고정된 구성과 크기의 매크로로 구성되어 있어 다양한 크기와 구성의 DNN 모델과 함께 사용하기에 유연성이 부족합니다. 매크로 크기가 DNN 레이어의 차원보다 작은 경우 반복적인 작업이 필요하며, 더 큰 매크로는 underutilization에 빠집니다. 이러한 도전에 대응하기 위해서는 각 레이어의 작업에 최적화된 이질적인 SRAM-CIM 매크로를 개발할 필요가 있습니다. 그러나 다양한 CIM 구조를 사용자 정의 디자인을 통해 최적화하는 것은 상당한 디자인 비용이 발생합니다. 따라서 효율적인 SRAM-CIM 컴파일러의 개발이 SRAM-CIM 구조의 광범위한 활용에 중요합니다. 본 IP에서는 SRAM-CIM 컴파일러에 적합한 빌딩 블록의 설계를 제안합니다. |