| IP명 |

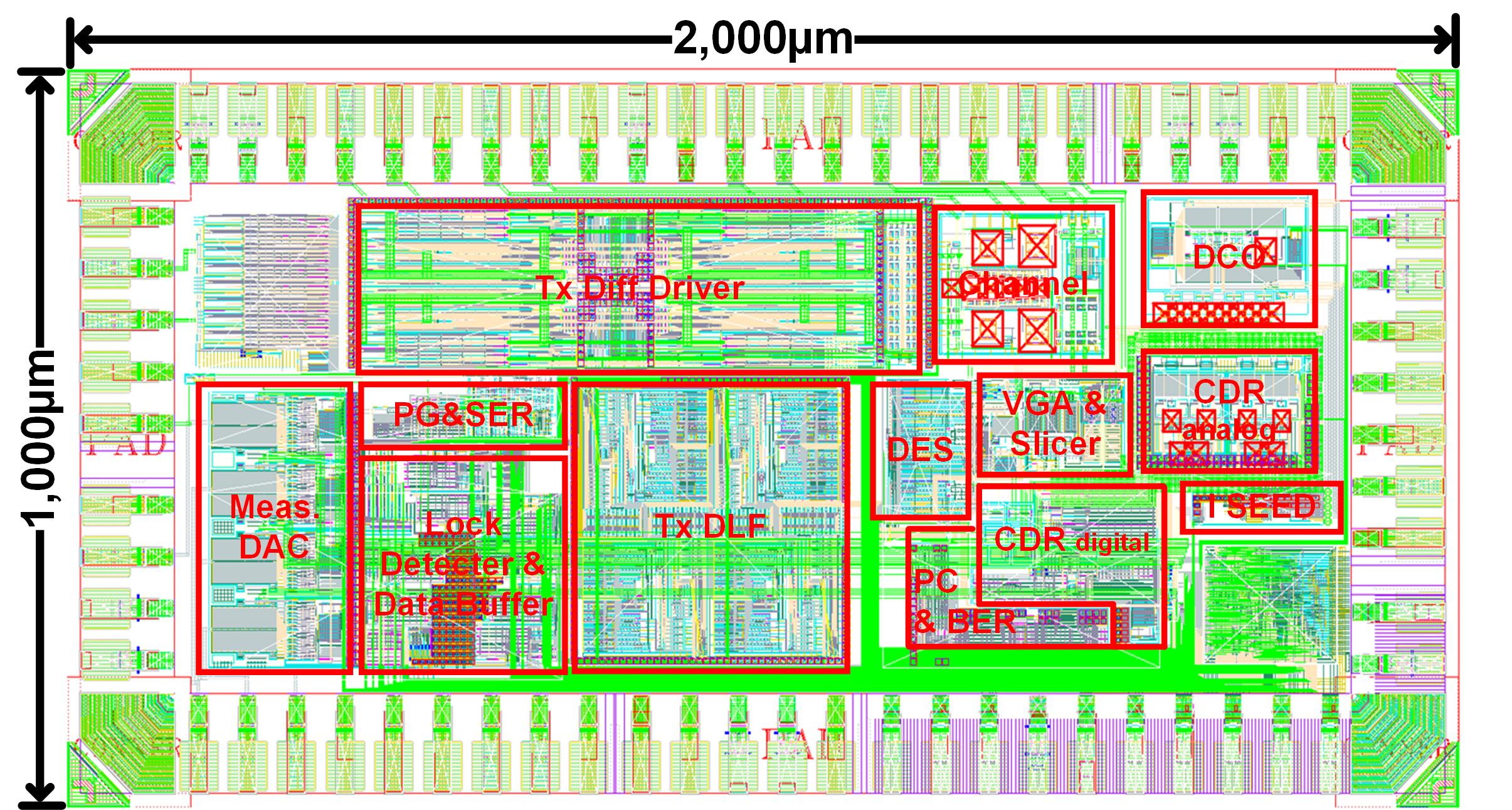

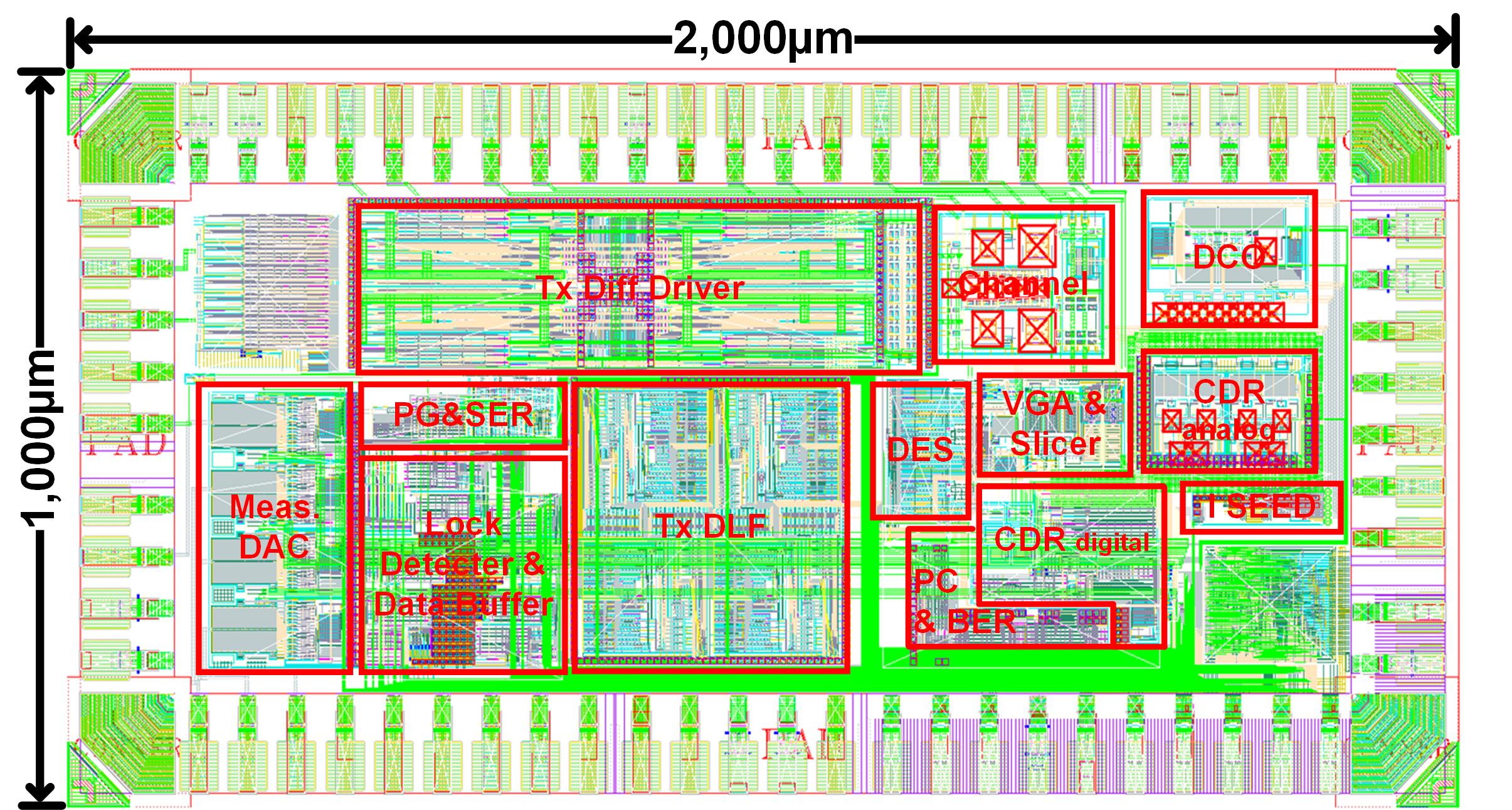

High-Speed IO Transmitter Design with adaptive FIR filter in 65 nm CMOS Process |

| Category |

Analog |

Application |

IO transmitter (CPU-to-memory interface) |

| 실설계면적 |

2㎛ X 1㎛ |

공급 전압 |

1.0V |

| IP유형 |

Hard IP |

동작속도 |

1-4 GHz |

| 검증단계 |

Silicon |

참여공정 |

HM-2203 |

| IP개요 |

1-4 Gbit/s의 연속주파수에서 동작하는 고속 인터페이스 IO 송수신기 회로를 설계할 계획이다. 송신기(Tx)의 탭크기가 다양한 채널 손실량과 동작 주파수의 변화에 따른 심볼간 간섭 노이즈(inter-symbol interference noise)의 크기에 따라 자동 적응(adaptive) 되는 방식으로 제거될 수 있는 시스템을 설계한다. 수신기(Rx)의 클럭 복원 회로(clock and data recovery-CDR)를 설계하여 고속 데이터 신호와 클럭 신호의 타이밍 정렬이 성공적으로 이루어 지게 한다. |

- 레이아웃 사진 -

|