| IP명 | MIPI D-PHY HS signaling standard를 이용한 8K 급 모바일 디스플레이 구동 고속인터페이스 개발 | ||

|---|---|---|---|

| Category | Analog | Application | Automotive |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.1V |

| IP유형 | Soft IP | 동작속도 | 6GHz |

| 검증단계 | Silicon | 참여공정 | SS28-2001 |

| IP개요 | MIPI D-PHY HS-mode signaling standard를 이용한 8K 디스플레이 드라이버 IC용 고속 인터페이스를 설계하고자 한다. 6Gbps/lane의 높은 동작속도를 위해 Samsung 28nm CMOS process를 이용하여 설계하며 저전력 transceiver 구조를 통해 고대역폭에서 증가하는 파워 소모를 보상할 것이다. Tri-state inverter를 이용한 저전력 Serializer 구조를 이용하며, 제안하는 selfbias receiver 구조를 통해 낮은 transmitter 설계에 대한 방안을 제시한다. 1.1 V 공급전압에서 1.6 mW/Gbps 이하의 파워소모 달성을 목표로 한다. High-speed transceiver circuit 및 Serializer/Deserializer를 포함하는 interface PHY (Physicallayer) mixed 회로를 설계할 것이다. |

||

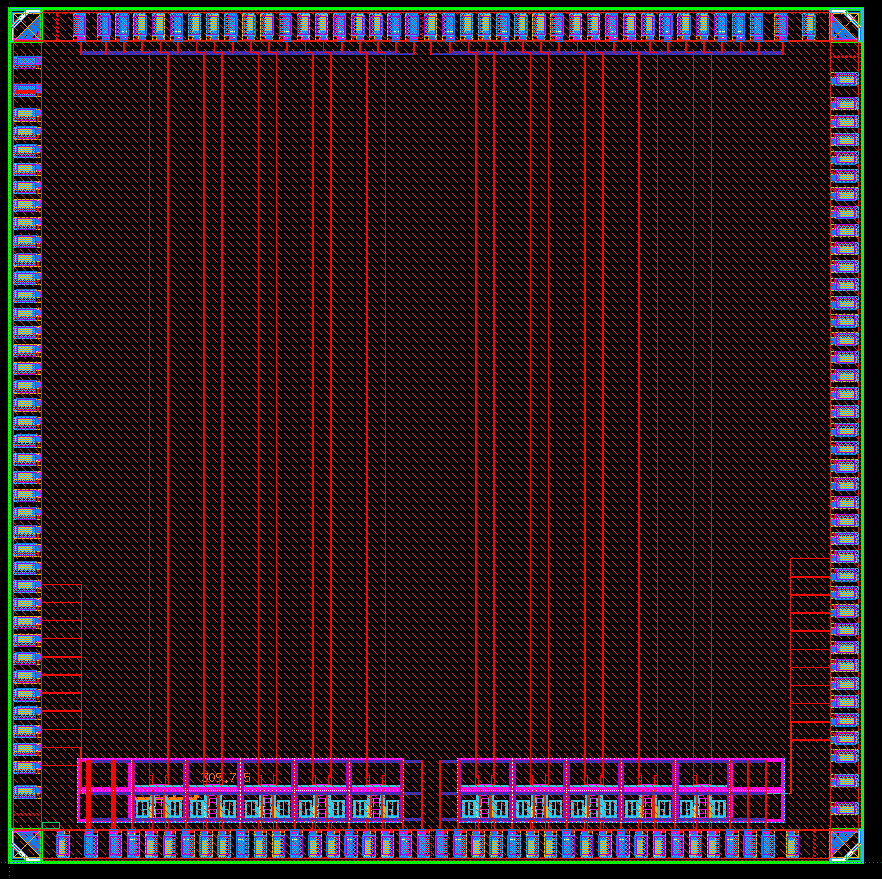

- 레이아웃 사진 -

|

|||