| IP명 | A Fully-Dynamic Zoom ADC Using a 2-Stage FIA with Time-Varying Frequency Compensation | ||

|---|---|---|---|

| Category | Analog | Application | Audio, Sensor |

| 실설계면적 | 5㎛ X 5㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 20.48MHz |

| 검증단계 | Silicon | 참여공정 | HM-2003 |

| IP개요 | 이 IP는 Static OTA 없이 SNDR 100 dB 이상을 달성한 Discrete-Time Delta-Sigma ADC임. Delta-sigma ADC의 핵심 기본 회로인 Closed-loop integrator를 OTA없이 구현하여 Fully dynamic operation을 가능케 함. FIA는 Time-varying system이기 때문에 기존의 Time-invariant system이라는 전제하에 적용했던 Stability compensation이 적절하지 않음. 이에 Time-varying frequency compensation technique이 제안됨. | ||

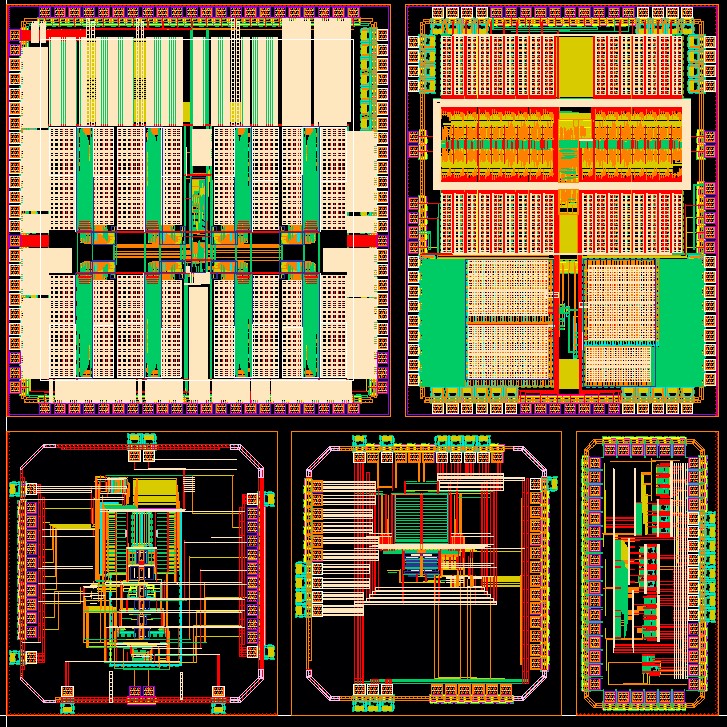

- 레이아웃 사진 -

|

|||