| IP명 | 온칩 학습이 가능한 스토캐스틱 컴퓨팅 기반 스파이킹 인공신경망 회로 | ||

|---|---|---|---|

| Category | Analog | Application | Processing in memory |

| 실설계면적 | 1.5㎛ X 1.5㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 100MHz |

| 검증단계 | Silicon | 참여공정 | HM-2102 |

| IP개요 | 위 IP는 Chip내에서 학습이 가능한 AI가속기 회로이다. Stochastic bit라는 확률 회로를 main compute block을 사용하여 저전력에서 동작하도록 설계하였다. Spiking nerual network의 시스템을 구현하였으며 STDP학습 알고리즘과 Supervised learning 학습방법을 적용한 회로이다. Stochastic bit는 VDD로 들어오는 전류를 조절하여 이 전류에 비례한 확률로 Cross coupled inverter의 양 노드의 전압을 결정하는 회로이다. 인버터의 VDD에 크기가 2배씩 차이나는 Pmos 5개를 연결하여 전류를 대수적으로 조절할 수 있도록 하였다. 인버터의 GND에는 NMOS를 연결하여 온도의 variation에 따른 확률 특성 변화를 보정하도록 하였다. 이렇게 확률적으로 결정되는 Stochastic bit 의 inverter의 전압을 Buffer를 통해 Spike를 발생시켜 Input 뉴런의 firing rate를 조절 할 수 있다. 시냅스는 Stochastic bit의 동작 특성을 고려해 STDP window에 맞도록 인코딩하여 SRAM에 weight를 저장하도록 설계하였다. 시냅스 동작 방법은 어레이 상에서 DEP counter, POT counter을 통해 Spike간의 시간 차이를 계산하였으며 post spike, pre spike여부를 SR LATCH를 통해 판단하여 확률적으로 STDP 동작 특성에 맞는 weight를 SRAM에 저장하도록 설계하였다. 각 시냅스는 1bit의 SRAM값을 갖는다. Output neuron 은 counter을 통해 Spike를 Intergrate하고 Modulator을 통해 Intergrate한 값을 Stochastic bit의 입력으로 인가한다. 이를 통해 Integrate & Fire 기능을 하는 output neuron을 구현하였다. |

||

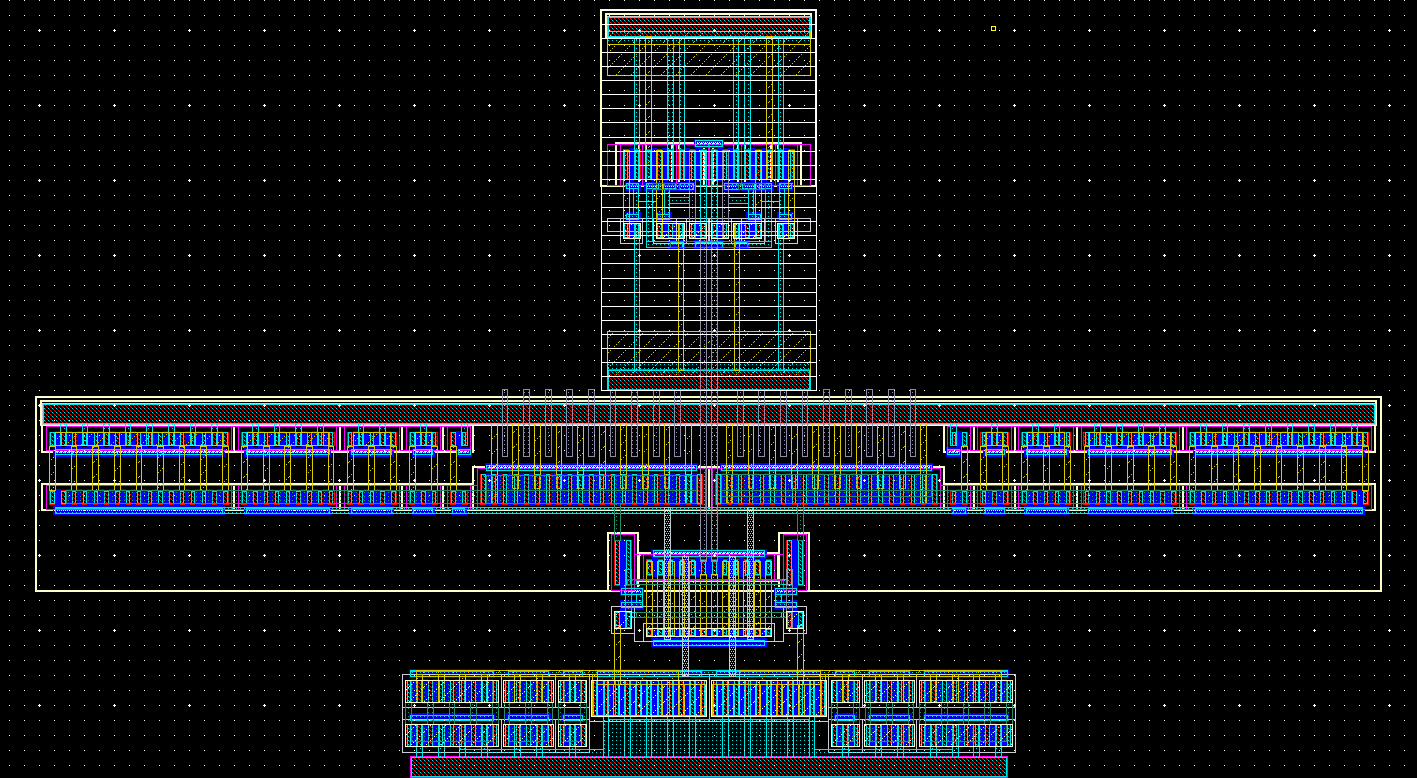

- 레이아웃 사진 -

|

|||