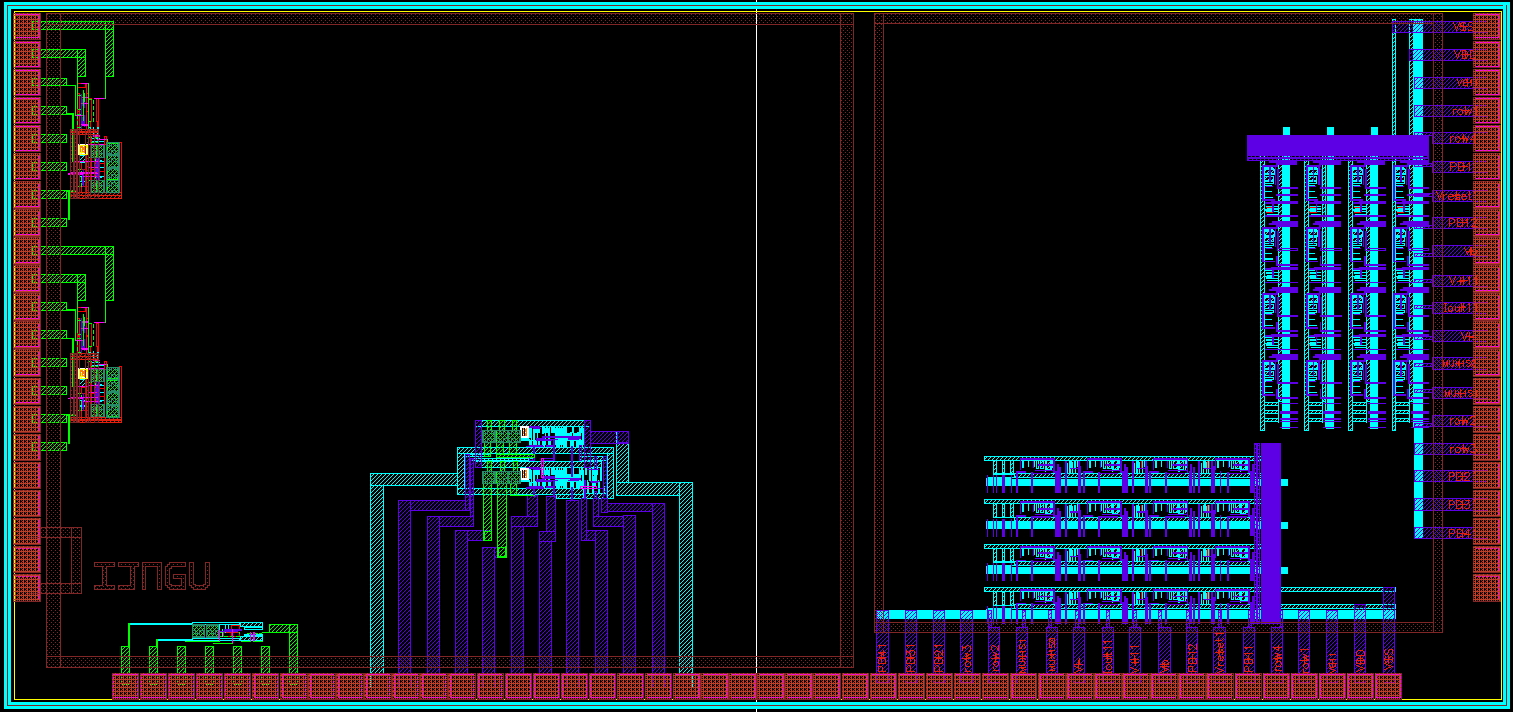

| IP개요 |

Recently, chaos generator has drawn much attention for the application in various academic/engineering fields. In this paper, a very simple CMOS generator associated with N-shape chaos map is proposed. The chaos map associated with the proposed circuit is derived via stroboscopic sampling method and its chaotic behaviors are analyzed with the help from numerical Mathematica simulation software. Additionally, the robustness of the proposed chaotic map is also confirmed by analyzing Lyapunov exponent diagram. To verify the idea, the chaotic circuit was implemented using 180 nm CMOS process. The simulation results from the mathematical model as well as the measurement results from the experiment confirmed the proposed scheme. The compactness, low power consumption and the robustness of chaos generation of the proposed chaotic circuit with variation of fabrication parameters thus recommending an effective solution of designing on-chip chaotic generator. |