| IP명 | A Wide-Lock-In-Range 12-GHz SSPLL Using a Low-Power Background-Operating Frequency-Disturbance-Detector | ||

|---|---|---|---|

| Category | Analog | Application | 5G/6G통신 통신반도체, 모뎀칩 |

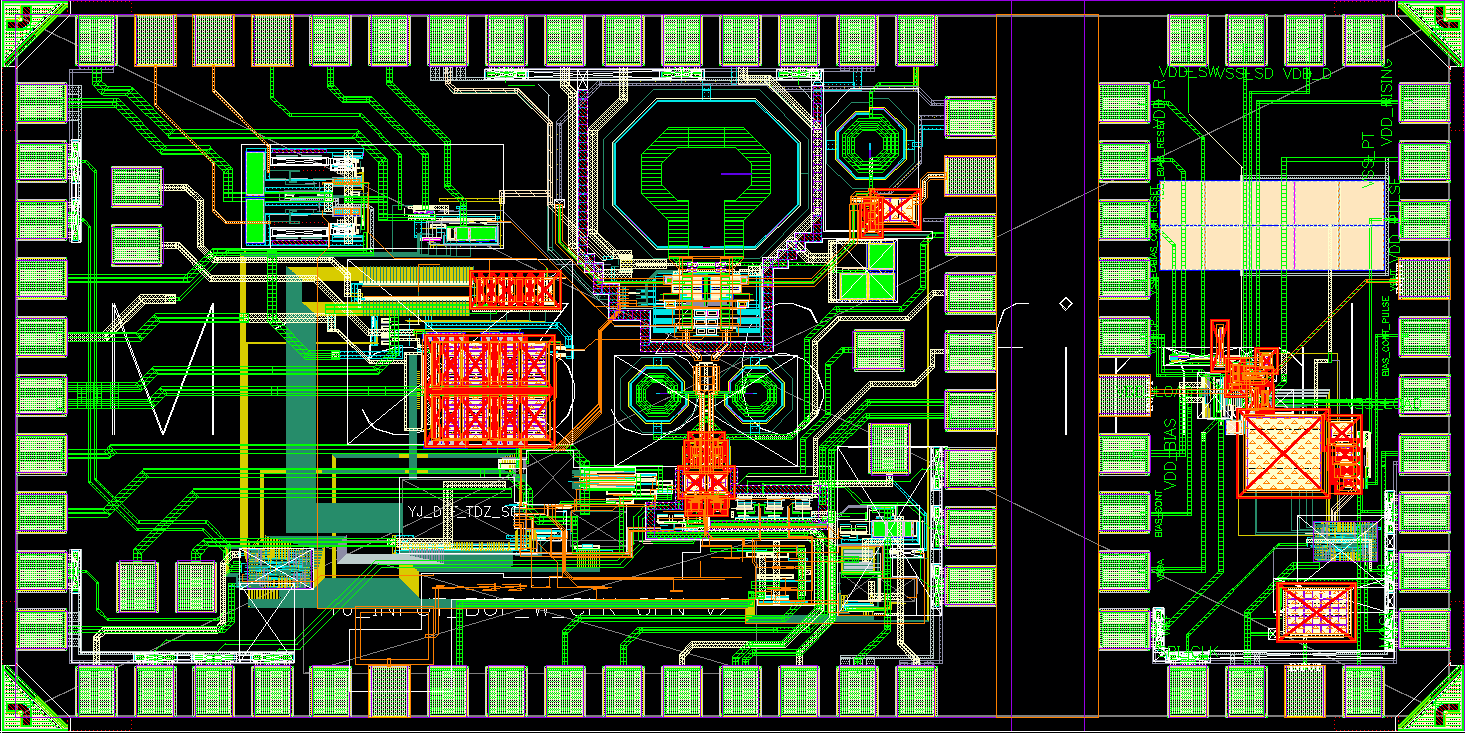

| 실설계면적 | 2㎛ X 1㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 15GHz |

| 검증단계 | Silicon | 참여공정 | HM-2402 |

| IP개요 | 50fs 미만 잡음을 가지는 Fractional PLL 개발 ◯ 기존 CPPLL을 Sampling PLL로 대체, 주파수에 비례하여 커지는 루프 이득을 얻을 수 있고, 전력 소모가 심한 내부 분배기를 없앨 수 있어 CPPLL 대비 초고주파 생성 시 잡음과 전력 성능이 우수. ◯ Fractional-N 동작을 위한 DTC의 비선형성과 노이즈를 해결하기 위해 선형성과 잡음 성능이 우수한 DAC을 사용하여 Fractional PLL을 구성. 이는 기존 Fractional PLL의 잡음장벽을 깰 수 있는 혁신적 방법. ◯ 기존 연구된 Sampling PLL 대비 넓은 주파수 영역과 우수한 잡음 성능을 위해 멀티밴드 PLL형식으로 구현. 이를 위해 Dual LC-VCO와 Dual band에서 최적화된 루프 이득을 가지는 Digital Low-Pass Filter (DLF) 탑재. 1μs 미만 초고속-세틀링타임을 가지는 PLL 개발 ◯ 기존 Sampling PLL은 내부 분배기가 없어 세틀링이 느린 단점 존재. 세틀링 개선을 위해 분배기 기반 주파수교정루프를 탑재시 VCO주파수로 동작하는 특성상 전력소모가 극심. ◯ 위 trade off를 타파하고자 Event-Driven 기반의 주파수락킹루프를 새롭게 개발. Sampling PD에서 벗어나는 전압을 모니터링하여 Event가 발생했을 때만 분배기를 on하여 세틀링을 개선하면서도 steady-state에서 전력소모는 0에 수렴. ◯ 잡음 교정 루프와 주파수 교정 루프는 병렬적으로 따로 동작하기 때문에 잡음 성능 열화 없이 정착시간만을 획기적으로 줄임. |

||

- 레이아웃 사진 -

|

|||