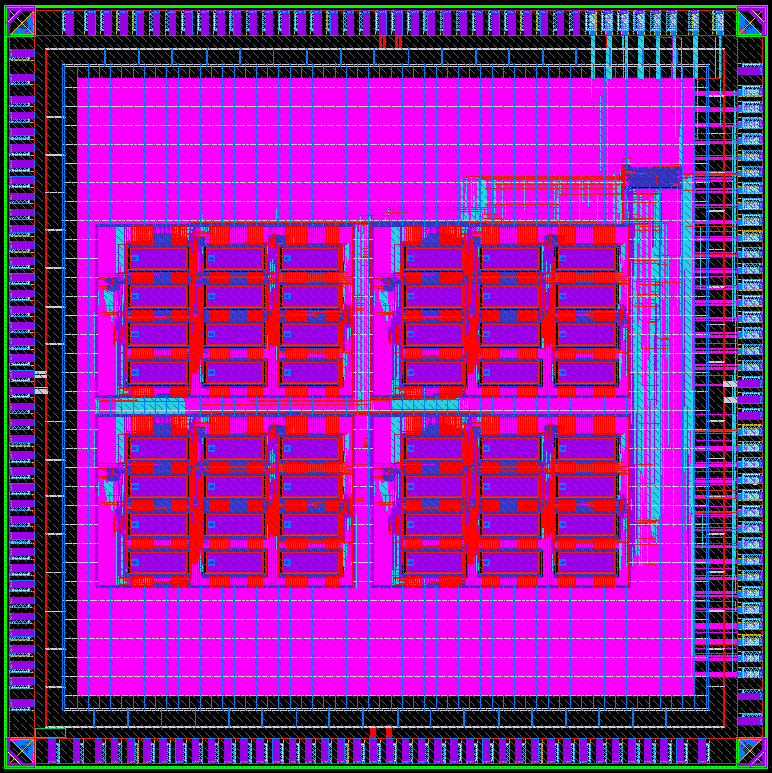

| IP개요 |

This paper presents a Network-on-Chip (NoC) based architecture aimed at addressing the rising demands of AI workloads such as high-performance object detection. The proposed design arranges computing, memory, and communication units in a 6×6 mesh topology, where each node is equipped with dual routers to alleviate congestion through parallel routing paths. By implementing XY-YX routing and wormhole flow control, the system balances traffic effectively, reduces latency, and ensures deadlock freedom. Additionally, a CoFEx module featuring 3×3 systolic array (SA) computing units maximizes data reuse and parallel processing for convolution operations, thus lowering power consumption. The dual-router setup allows flexible and scalable communication, while specialized modules such as the feature map setup unit (FSU) and on-chip memory interfaces streamline data movement. Simulation results confirm that parallel operations occur as intended, with results fed back to external systems through communication controllers. Overall, this architecture offers a robust, high-throughput platform that is well-suited to meet the real-time and power-efficiency requirements of next-generation AI applications. |