| IP개요 |

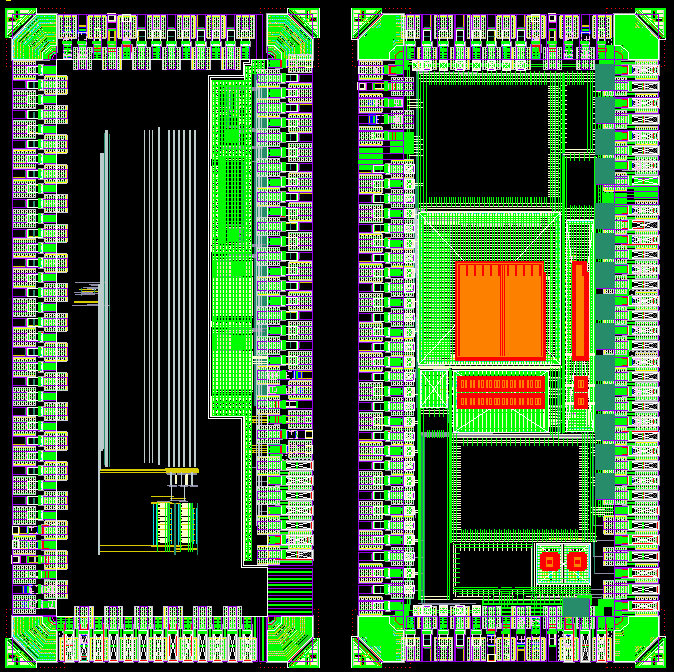

본 연구에서는 고면적 효율을 갖는 아날로그 Compute-In-Memory(CIM) 시스템인 RS-CIM을 개발하였다. 제안된 구조는 기존 아날로그 CIM에서 면적과 전력 소모의 주요 원인이 되는 DAC 및 ADC의 구조적 한계를 해결하고자 한다. 입력 구동을 위해 7T SRAM 기반의 Digital-to-Time Converter(DTC)를 제안하고, 출력 변환을 위해 저전력·소면적의 R-DAC과 SAR ADC가 결합된 하이브리드 ADC(RS-ADC)를 제안하였다. RS-ADC는 기존 SAR ADC 대비 샘플링 커패시터 수를 87.5%, 플래시 ADC 대비 비교기 수를 93.3% 감소시켰으며, 컬럼 병렬성을 유지하면서도 고효율 동작을 실현하였다. 제안된 RS-CIM은 180nm CMOS 공정에서 구현되었으며, 28nm 공정으로 스케일링 시 247.7 TOPS/W, 6.498 TOPS/mm²의 성능을 달성한다. 본 구조는 고속 병렬 처리 및 고밀도 메모리 배열 구성을 가능하게 하며, 저전력 인공지능 응용에 적합하다. |