| IP명 | An capacitor-less digital low drop-out regulator with memory-access algorithm-based predictive controller | ||

|---|---|---|---|

| Category | Mixed | Application | SoC |

| 실설계면적 | 0.972㎛ X 0.754㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 100MHz |

| 검증단계 | Silicon | 참여공정 | SF028-2501 |

| IP개요 | 본 설계는 AI를 위한 다수의 CPU Core, 메모리와 연산가속기 등의 Cell들을 포함한 Heterogeneous SoCs 구조 회로의 전력 관리를 목적으로 하는 An capacitor-less all digital LDO regulator with memory-access algorithm-based predictive controller를 제안한다. 최신 Heterogeneous SoCs 구조를 갖는 On device AI의 전력 관리 회로의 적은 면적부담 요구에 따라, 본 설계 또한 작은 부하 캐패시터를 사용한 Capacitor-Less 구조로 설계하였다. 그리고 CPU Core, 메모리와 연산가속기 등의 Cell들이 반복되는 동작 패턴을 가지며 소모하는 전력 또한 반복되는 패턴을 가지는 부하 특성을 활용하여 빠른 과도 응답 시간을 달성한다. |

||

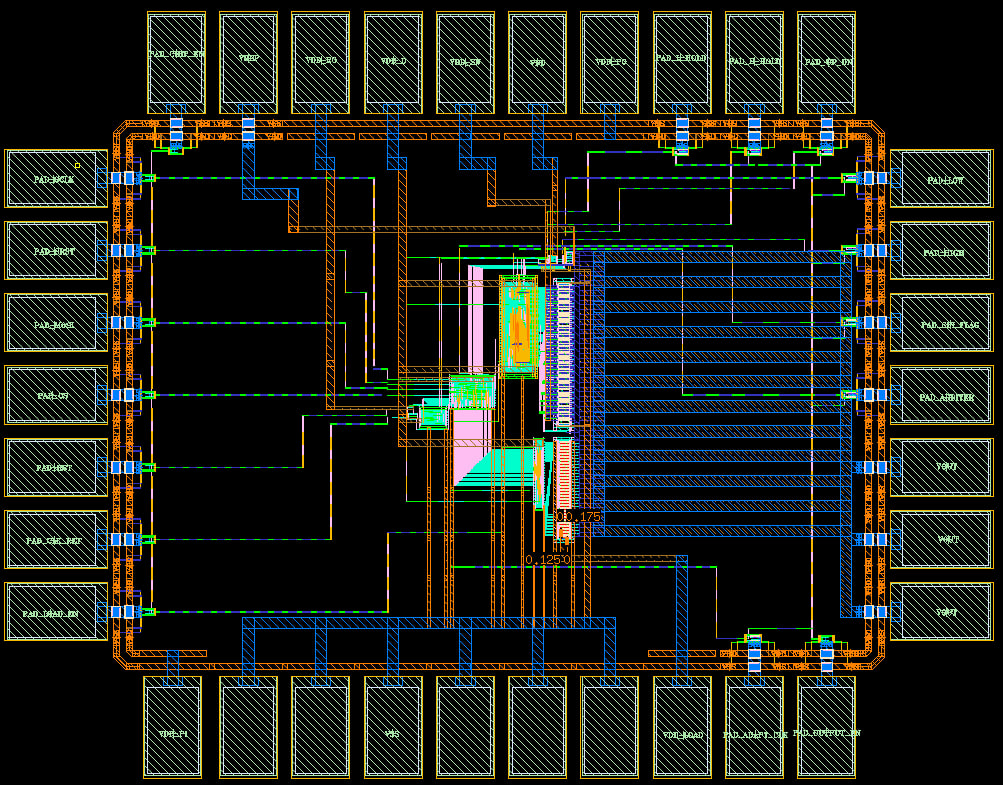

- 레이아웃 사진 -

|

|||