| IP명 | A 11-ENOB 1-GS/s Pipelined ADC with PVT Robust Ring Amplifier | ||

|---|---|---|---|

| Category | Analog | Application | Analog to digital converter |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 1GHz |

| 검증단계 | Silicon | 참여공정 | SF028-2501 |

| IP개요 | We propose a ring amplifier based 11–ENOB, 1-GS/s Discrete time pipelined ADC with PVT robust constant current and dead zone bias. Ring amplifiers are power efficient dynamic amplifiers which are suitable to be used as residue amplifier. The biasing of second stage of the amplifier in constant current across PVT has been a challenge in the recent years. We propose a new architecture called ‘split’ input stage ring amplifier. Another major robustness bottleneck is proper dead zone bias. We leverage the amplitude regulation circuit for oscillators to detect the extent of ringing during settling and accordingly bias the dead zone. |

||

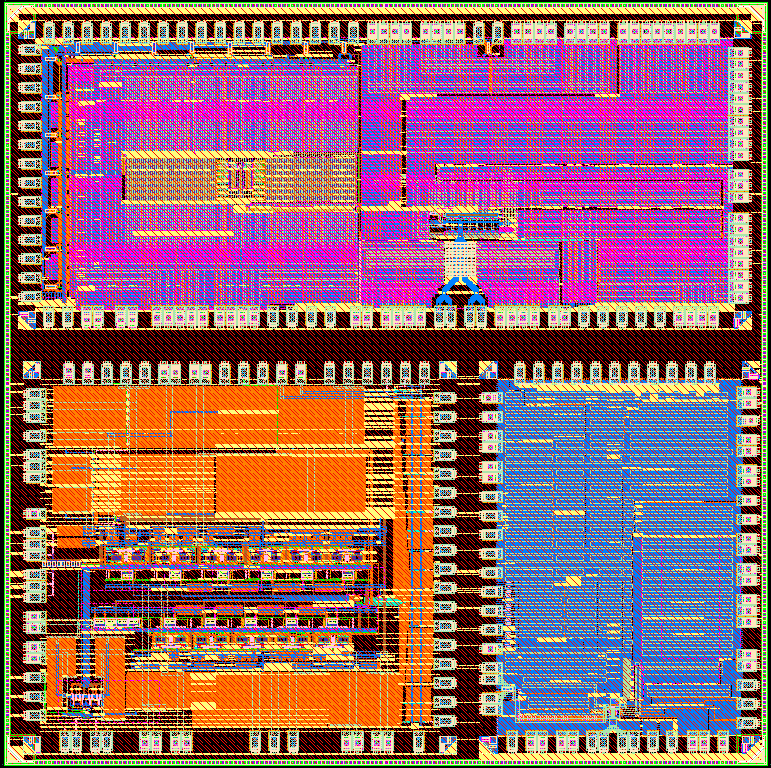

- 레이아웃 사진 -

|

|||