| IP개요 |

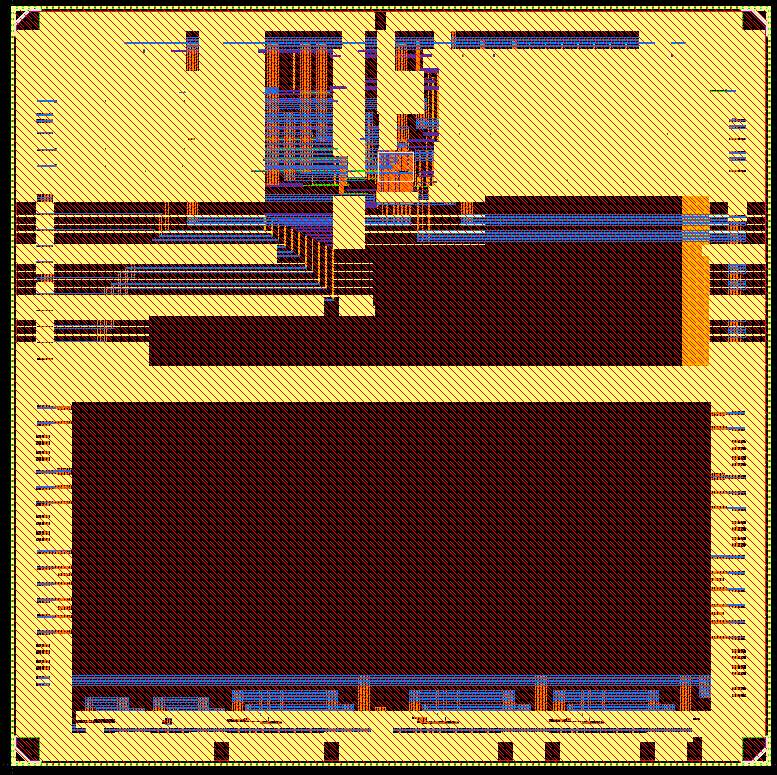

본 설계 제안서에서 제안하는 회로는 Switched Capacitive Peaking(SCP) 기법을 적용한 24 Gb/s PAM-3 Transmitter(TX)이다. 제안된 구조는 전송선에서 발생하는 전송 손실과 인터심볼 간섭(ISI)을 보상하기 위해 Pre-Emphasis 기반 Feed-Forward Equalizer(FFE)를 사용한다. 기존의 De-Emphasis(DE) 방식 대비 출력 신호 크기 감소와 대역폭 저하 문제를 방지하며, 또한 Conventional Capacitive Peaking(CCP) 방식 대비 출력 드라이버에 부가되는 부하 커패시턴스를 제거하여 대역폭 저하 없이 고주파 성분을 강화한다. 본 설계는 28 nm FD-SOI 공정을 이용하여 구현되며, 출력 드라이버는 N-over-N 구조와 LVSTL(Low Voltage Swing Terminated Logic) 방식을 채택하여 고속 동작에서 신호 손실을 최소화하고 전력 효율을 향상시킨다. 또한 3b/2UI 인코더와 트랜지션 디텍터를 통해 PAM-3 신호 레벨에 따라 적응적으로 펄스 폭을 조절함으로써, 전력 효율을 유지하면서 충분한 eye margin을 확보한다. 제안된 24 Gb/s PAM-3 TX는 메모리 인터페이스 차세대 표준에 부합하는 핵심 IP로서, 고속·저전력 동작을 동시에 만족시켜 글로벌 및 국내 반도체 산업에서 높은 수요가 예상된다. |