| IP명 | A 2.5GS/s Flash-and-VCO-Based Subranging ADC Using a Resistor-Ladder-Based Residue Shifter | ||

|---|---|---|---|

| Category | Mixed | Application | 인터페이 |

| 실설계면적 | 1㎛ X 1㎛ | 공급 전압 | 0.9V |

| IP유형 | Hard IP | 동작속도 | 5GHz |

| 검증단계 | Silicon | 참여공정 | HM-2503 |

| IP개요 | This work presents a 7-bit pipelined subranging ADC that integrates a 3-bit flash ADC with a ring VCO-based quantizer. A resistor-ladder-based residue shifter (RLRS) replaces traditional residue amplifiers, efficiently shifting the residue voltage into the most linear region of the KVCO , thereby eliminating the need for post-linearity calibration. | ||

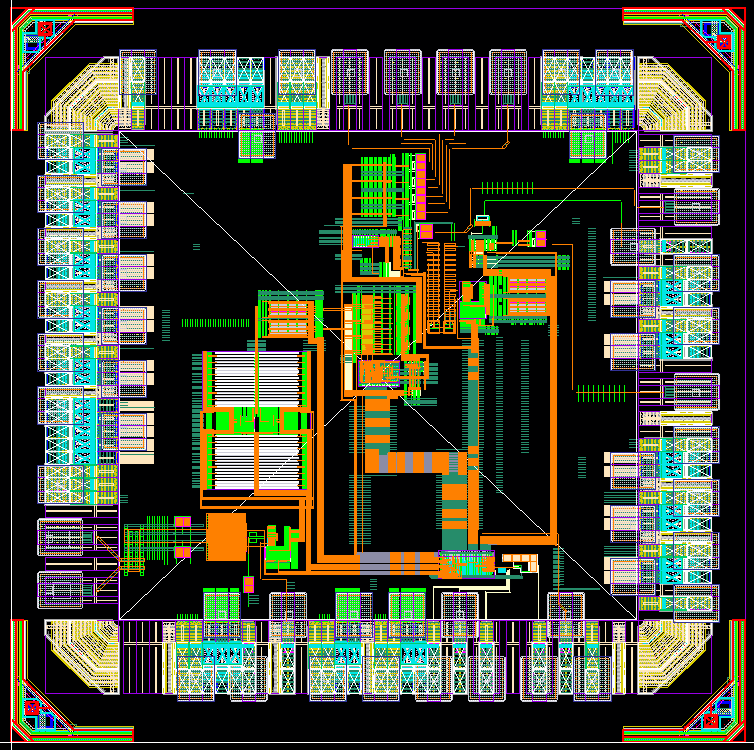

- 레이아웃 사진 -

|

|||