| IP명 | 배터리없이 상시 동작 가능한 뉴로모픽 태그 (NeuroTag) 구현을 위한 SNN 프로세서 IC 설계 | ||

|---|---|---|---|

| Category | Analog | Application | AI |

| 실설계면적 | 3㎛ X 1.67㎛ | 공급 전압 | 1.8V/3.3VV |

| IP유형 | Hard IP | 동작속도 | 1MHz |

| 검증단계 | Simulation | 참여공정 | HM-2503 |

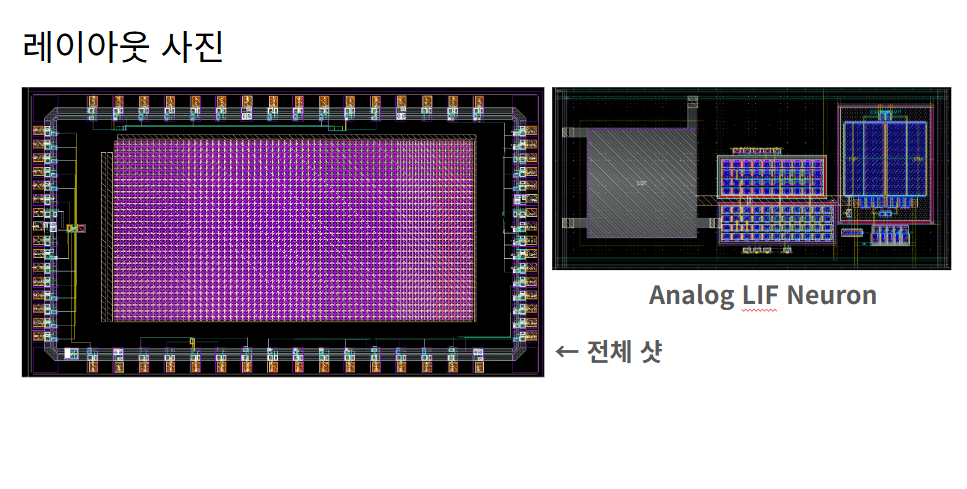

| IP개요 | 본 IP는 아날로그 뉴런, 뉴런 내 시냅스의 Weight Memory, 그리고 Analog Spike를 상용 RFIC (e.g., Rocky100)와 호환시키기 위한 어댑터를 포함하고 있다. 아날로그 뉴런은 Leaky Integrate-and-Fire (LIF) 구조를 기반으로 하며, PMOS 기반 스파이크 입력 게이트와 커패시터를 활용한 Multiply-Accumulate (MAC) 연산을 별도의 ALU나 Amplifier 없이 구현하는 회로를 포함한 기술을 포함하고 있다. 뉴런 내 시냅스의 Weight Memory는 Current Weight (전류원 기반 가중치)와 PMOS 트랜지스터를 결합하였으며, 전류 제어 방식을 적용하여 초저전력으로 시냅스 가중치 곱셈 연산 수행을 가능하게 할 것으로 기대된다. Spike-to-RFIC 어댑터는 비동기 Binary Ripple Counter와 PISO Shift Register로 구성되어, 스파이크 발생 시에만 전력을 소모하며 RFID 통신 기회가 올 때까지 스파이크를 저전력으로 저장한 후 SPI 프로토콜을 통해 직렬화된 데이터를 전송할 수 있도록 설계되었다. |

||

- 레이아웃 사진 -

|

|||