| IP명 | A Sturdy MASH Third-Order Noise-Shaping SAR ADC with Reuse of the SAR ADC | ||

|---|---|---|---|

| Category | Mixed | Application | ADC |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 80MHz |

| 검증단계 | Silicon | 참여공정 | SS028-2502 |

| IP개요 | Multi-stage noise-shaping(MASH) 구조를 활용한 3차 noise-shaping SAR ADC를 제안한다. 제안된 ADC는 첫 번째 stage에서 사용된 SAR ADC를 두 번째 stage에서 재사용함으로써 추가적인 하드웨어 요구를 최소화한다. CIFF(Cascade of Integrators with Feed-Forward) 구조를 기반으로 총 3차 noise transfer function(NTF)을 구현하며, closed-loop dynamic amplifier를 이용한 적분기를 활용하여 PVT variation에 강인한 noise-shaping 특성을 확보한다. 제안하는 ADC는 28-nm CMOS 공정을 사용하였고, 공급 전압은 1V이다. Sampling rate은 80 MS/s이며 oversampling ratio(OSR)는 10이다. SPICE 시뮬레이션 결과, 제안된 ADC는 84.4 dB의 SNDR 성능을 달성하였다. | ||

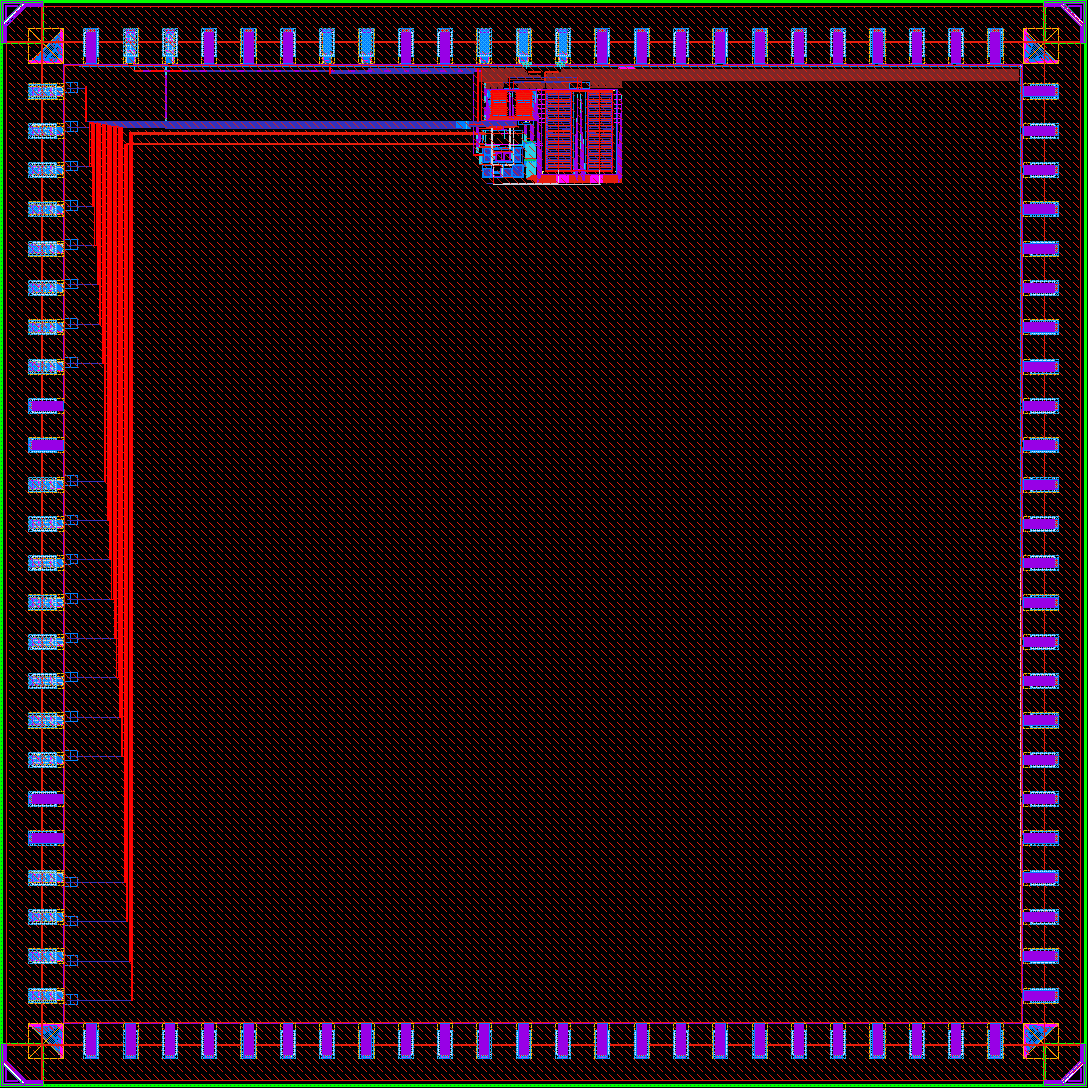

- 레이아웃 사진 -

|

|||