| IP명 | Asymmetric Simultaneous Bi-Directional Transceiver with Unified Signal Integrity Compensation for Efficient Heterogeneous Process Integration | ||

|---|---|---|---|

| Category | Analog | Application | Chiplet, Memory |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 28GHz |

| 검증단계 | Silicon | 참여공정 | SS028-2502 |

| IP개요 | In this design, a novel asymmetric simultaneous bi- directional (SBD) signaling method for high-bandwidth interfaces in heterogeneous chiplet-based packaging environments is proposed. The proposed design eliminates the need for adder circuits by directly canceling transmitted signals at the receiver comparators, thereby reducing overall area and power consumption. Additionally, a unified signal integrity compensation (USIC) circuit is introduced to effectively mitigate crosstalk, reflections, and inter-symbol interference with minimal power overhead. The proposed technique achieves high signal integrity and efficiency, making it well-suited for compact, low-power, high-performance chiplet integration. The prototype chip is planned to be fabricated with an area of 4mm x 4mm using a 28nm LPP process. |

||

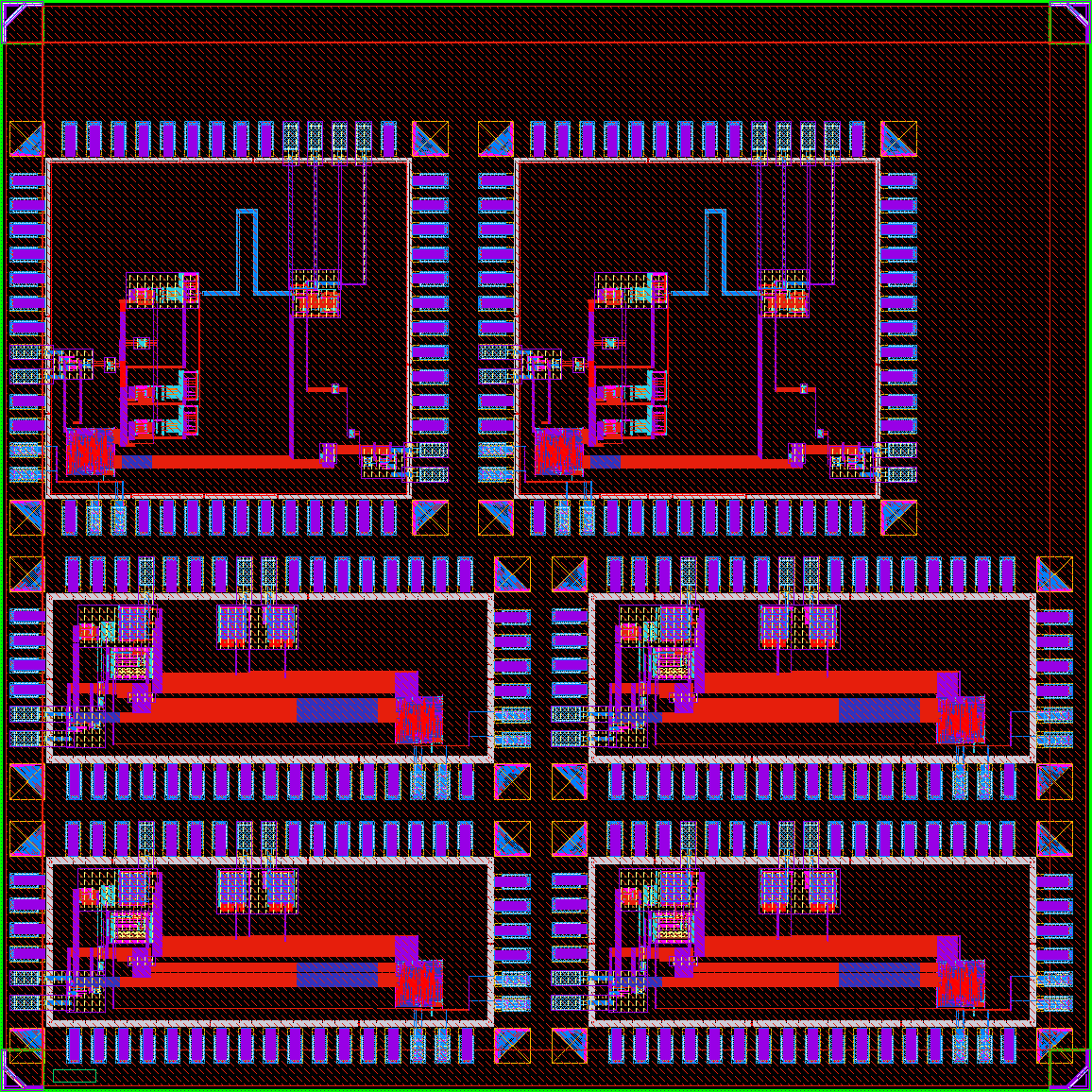

- 레이아웃 사진 -

|

|||